- Page 1 and 2: MicroBlaze Processor Reference Guid

- Page 3 and 4: Date Version Revision 06/25/07 8.0

- Page 5 and 6: Table of Contents Revision History

- Page 7 and 8: Introduction Guide Contents Convent

- Page 9 and 10: MicroBlaze Architecture Overview IX

- Page 11 and 12: Table 2-1: Configurable Feature Ove

- Page 13 and 14: Data Types and Endianness Data Type

- Page 15 and 16: Table 2-5: Instruction Set Nomencla

- Page 17 and 18: Table 2-6: MicroBlaze Instruction S

- Page 19 and 20: Table 2-6: MicroBlaze Instruction S

- Page 21 and 22: Table 2-6: MicroBlaze Instruction S

- Page 23 and 24: Instructions a word. For both instr

- Page 25 and 26: Special Purpose Registers Program C

- Page 27 and 28: Table 2-9: Machine Status Register

- Page 29 and 30: Exception Address Register (EAR) Re

- Page 31 and 32: Registers Table 2-12: Exception Spe

- Page 33 and 34: Floating Point Status Register (FSR

- Page 35 and 36: Process Identifier Register (PID) R

- Page 37 and 38: Translation Look-Aside Buffer Low R

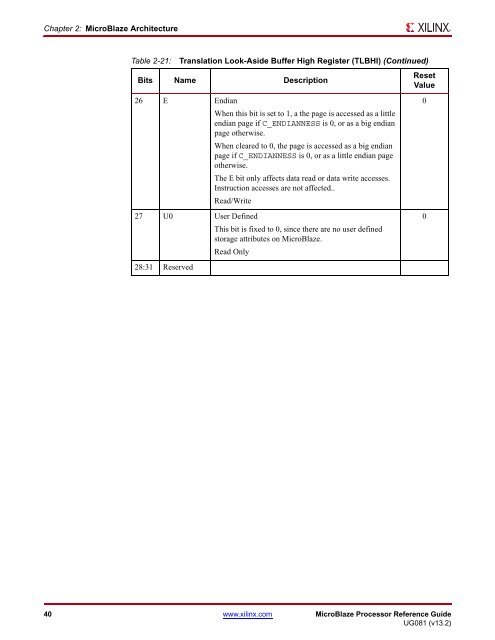

- Page 39: Translation Look-Aside Buffer High

- Page 43 and 44: Processor Version Register (PVR) Re

- Page 45 and 46: Table 2-26: Processor Version Regis

- Page 47 and 48: Table 2-29: Processor Version Regis

- Page 49 and 50: Pipeline Architecture Pipeline Arch

- Page 51 and 52: Memory Architecture Memory Architec

- Page 53 and 54: Virtual-Memory Management Real Mode

- Page 55 and 56: Virtual-Memory Management System so

- Page 57 and 58: TLBLO: TLB Entry Format Virtual-Mem

- Page 59 and 60: Virtual-Memory Management system so

- Page 61 and 62: Virtual-Memory Management A TLB ent

- Page 63 and 64: Reset, Interrupts, Exceptions, and

- Page 65 and 66: Exception Causes Reset, Interrupts,

- Page 67 and 68: Breaks Equivalent Pseudocode Reset,

- Page 69 and 70: User Vector (Exception) Reset, Inte

- Page 71 and 72: Instruction Cache Operation Instruc

- Page 73 and 74: General Data Cache Functionality Da

- Page 75 and 76: Data Cache memory before reading ba

- Page 77 and 78: Rounding Operations Floating Point

- Page 79 and 80: float sum, t; int i; sum = 0.0f; fo

- Page 81 and 82: Debug and Trace Debug Overview Trac

- Page 83 and 84: Fault Tolerance The LMB BRAM Interf

- Page 85 and 86: eturn XST_FAILURE; } Fault Toleranc

- Page 87 and 88: Small Typical Full Fault Tolerance

- Page 89 and 90: MicroBlaze Partition BRAM MicroBlaz

- Page 91 and 92:

Chapter 3 MicroBlaze Signal Interfa

- Page 93 and 94:

Table 3-1: Summary of MicroBlaze Co

- Page 95 and 96:

Table 3-1: Summary of MicroBlaze Co

- Page 97 and 98:

Table 3-1: Summary of MicroBlaze Co

- Page 99 and 100:

Table 3-1: Summary of MicroBlaze Co

- Page 101 and 102:

Table 3-1: Summary of MicroBlaze Co

- Page 103 and 104:

AXI4 Interface Description cache is

- Page 105 and 106:

Local Memory Bus (LMB) Interface De

- Page 107 and 108:

Clk Addr Byte_Enable Data_Write AS

- Page 109 and 110:

Clk Addr Byte_Enable Data_Write AS

- Page 111 and 112:

Clk Addr Byte_Enable Data_Write AS

- Page 113 and 114:

Slave FSL Signal Interface FSL Tran

- Page 115 and 116:

CacheLink Signal Interface The Cach

- Page 117 and 118:

Xilinx CacheLink (XCL) Interface De

- Page 119 and 120:

Lockstep Interface Description Lock

- Page 121 and 122:

Table 3-11: MicroBlaze Lockstep Com

- Page 123 and 124:

Table 3-11: MicroBlaze Lockstep Com

- Page 125 and 126:

Debug Interface Description Trace I

- Page 127 and 128:

Table 3-14: Type of Trace Exception

- Page 129 and 130:

Table 3-15: MPD Parameters (Continu

- Page 131 and 132:

Table 3-15: MPD Parameters (Continu

- Page 133 and 134:

Table 3-15: MPD Parameters (Continu

- Page 135 and 136:

Table 3-15: MPD Parameters (Continu

- Page 137 and 138:

Table 3-15: MPD Parameters (Continu

- Page 139 and 140:

Chapter 4 MicroBlaze Application Bi

- Page 141 and 142:

Stack Convention Stack Convention T

- Page 143 and 144:

Calling Convention Memory Model Sma

- Page 145 and 146:

Chapter 5 MicroBlaze Instruction Se

- Page 147 and 148:

Formats Type A MicroBlaze uses two

- Page 149 and 150:

addi Arithmetic Add Immediate Descr

- Page 151 and 152:

andi Logial AND with Immediate Desc

- Page 153 and 154:

andni Logical AND NOT with Immediat

- Page 155 and 156:

eqi Branch Immediate if Equal Descr

- Page 157 and 158:

gei Branch Immediate if Greater or

- Page 159 and 160:

gti Branch Immediate if Greater Tha

- Page 161 and 162:

lei Branch Immediate if Less or Equ

- Page 163 and 164:

lti Branch Immediate if Less Than D

- Page 165 and 166:

nei Branch Immediate if Not Equal D

- Page 167 and 168:

Note Instructions The instructions

- Page 169 and 170:

Registers Altered rD PC Latency N

- Page 171 and 172:

ki Break Immediate Description Inst

- Page 173 and 174:

si Barrel Shift Immediate Descripti

- Page 175 and 176:

cmp Integer Compare Description Ins

- Page 177 and 178:

frsub Reverse Floating Point Arithm

- Page 179 and 180:

fdiv Floating Point Arithmetic Divi

- Page 181 and 182:

Table 5-2: Floating Point Compariso

- Page 183 and 184:

fint Floating Point Convert Float t

- Page 185 and 186:

get get from stream interface tneag

- Page 187 and 188:

getd get from stream interface dyna

- Page 189 and 190:

idiv Integer Divide Description Ins

- Page 191 and 192:

lbu Load Byte Unsigned Description

- Page 193 and 194:

lhu Load Halfword Unsigned Descript

- Page 195 and 196:

lw Load Word Description Instructio

- Page 197 and 198:

lwx Load Word Exclusive lwx rD, rA,

- Page 199 and 200:

mbar Memory Barrier Description Ins

- Page 201 and 202:

Instructions The value read from FS

- Page 203 and 204:

msrset Read MSR and set bits in MSR

- Page 205 and 206:

The SLR and SHR are only valid as a

- Page 207 and 208:

mulh Multiply High Description Inst

- Page 209 and 210:

mulhsu Multiply High Signed Unsigne

- Page 211 and 212:

or Logical OR Description Instructi

- Page 213 and 214:

pcmpbf Pattern Compare Byte Find De

- Page 215 and 216:

pcmpne Pattern Compare Not Equal De

- Page 217 and 218:

Registers Altered Latency Note MSR

- Page 219 and 220:

Registers Altered Latency Note MSR

- Page 221 and 222:

subi Arithmetic Reverse Subtract Im

- Page 223 and 224:

tid Return from Interrupt rn from I

- Page 225 and 226:

tsd Return from Subroutine Descript

- Page 227 and 228:

sbi Store Byte Immediate Descriptio

- Page 229 and 230:

sext8 Sign Extend Byte Description

- Page 231 and 232:

shi Store Halfword Immediate Descri

- Page 233 and 234:

src Shift Right with Carry Descript

- Page 235 and 236:

sw Store Word Description Instructi

- Page 237 and 238:

swx Store Word Exclusive swx rD, rA

- Page 239 and 240:

wdc Write to Data Cache wdc wdc.flu

- Page 241 and 242:

wic Write to Instruction Cache Desc

- Page 243 and 244:

xori Logical Exclusive OR with Imme

- Page 245 and 246:

Additional Resources EDK Documentat