Power Management in Embedded Systems - DAIICT Intranet

Power Management in Embedded Systems - DAIICT Intranet

Power Management in Embedded Systems - DAIICT Intranet

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

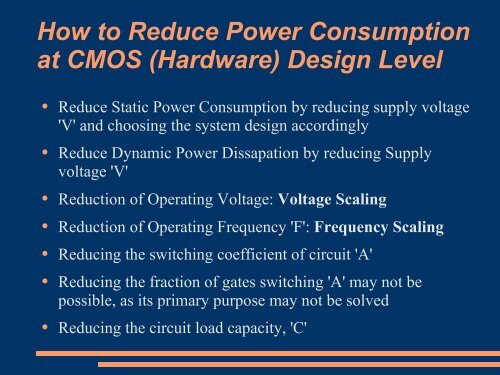

How to Reduce <strong>Power</strong> Consumption<br />

at CMOS (Hardware) Design Level<br />

● Reduce Static <strong>Power</strong> Consumption by reduc<strong>in</strong>g supply voltage<br />

'V' and choos<strong>in</strong>g the system design accord<strong>in</strong>gly<br />

● Reduce Dynamic <strong>Power</strong> Dissapation by reduc<strong>in</strong>g Supply<br />

voltage 'V'<br />

● Reduction of Operat<strong>in</strong>g Voltage: Voltage Scal<strong>in</strong>g<br />

● Reduction of Operat<strong>in</strong>g Frequency 'F': Frequency Scal<strong>in</strong>g<br />

● Reduc<strong>in</strong>g the switch<strong>in</strong>g coefficient of circuit 'A'<br />

● Reduc<strong>in</strong>g the fraction of gates switch<strong>in</strong>g 'A' may not be<br />

possible, as its primary purpose may not be solved<br />

● Reduc<strong>in</strong>g the circuit load capacity, 'C'