4047 Mono-stable : astable Multivibrator.pdf

4047 Mono-stable : astable Multivibrator.pdf

4047 Mono-stable : astable Multivibrator.pdf

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

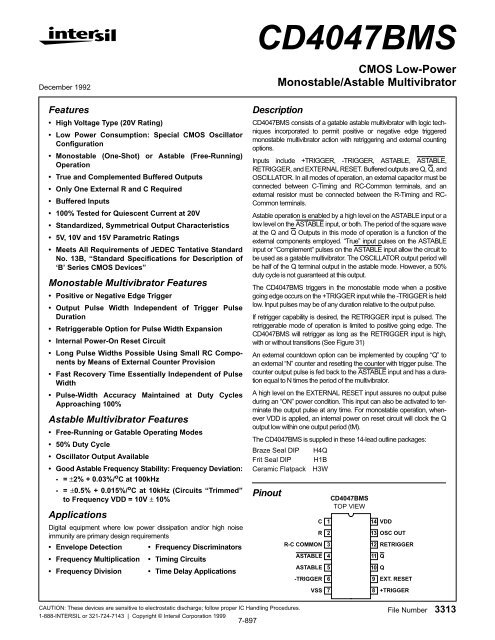

December 1992<br />

Features<br />

• High Voltage Type (20V Rating)<br />

• Low Power Consumption: Special CMOS Oscillator<br />

Configuration<br />

• <strong>Mono</strong><strong>stable</strong> (One-Shot) or A<strong>stable</strong> (Free-Running)<br />

Operation<br />

• True and Complemented Buffered Outputs<br />

• Only One External R and C Required<br />

• Buffered Inputs<br />

• 100% Tested for Quiescent Current at 20V<br />

• Standardized, Symmetrical Output Characteristics<br />

• 5V, 10V and 15V Parametric Ratings<br />

• Meets All Requirements of JEDEC Tentative Standard<br />

No. 13B, “Standard Specifications for Description of<br />

‘B’ Series CMOS Devices”<br />

<strong>Mono</strong><strong>stable</strong> <strong>Multivibrator</strong> Features<br />

• Positive or Negative Edge Trigger<br />

• Output Pulse Width Independent of Trigger Pulse<br />

Duration<br />

• Retriggerable Option for Pulse Width Expansion<br />

• Internal Power-On Reset Circuit<br />

• Long Pulse Widths Possible Using Small RC Components<br />

by Means of External Counter Provision<br />

• Fast Recovery Time Essentially Independent of Pulse<br />

Width<br />

• Pulse-Width Accuracy Maintained at Duty Cycles<br />

Approaching 100%<br />

A<strong>stable</strong> <strong>Multivibrator</strong> Features<br />

• Free-Running or Gatable Operating Modes<br />

• 50% Duty Cycle<br />

• Oscillator Output Available<br />

• Good A<strong>stable</strong> Frequency Stability: Frequency Deviation:<br />

- = ±2% + 0.03%/ oC at 100kHz<br />

- = ±0.5% + 0.015%/ oC at 10kHz (Circuits “Trimmed”<br />

to Frequency VDD = 10V ± 10%<br />

Applications<br />

Digital equipment where low power dissipation and/or high noise<br />

immunity are primary design requirements<br />

• Envelope Detection • Frequency Discriminators<br />

• Frequency Multiplication • Timing Circuits<br />

• Frequency Division • Time Delay Applications<br />

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.<br />

1-888-INTERSIL or 321-724-7143 | Copyright © Intersil Corporation 1999<br />

7-897<br />

CD<strong>4047</strong>BMS<br />

CMOS Low-Power<br />

<strong>Mono</strong><strong>stable</strong>/A<strong>stable</strong> <strong>Multivibrator</strong><br />

Description<br />

CD<strong>4047</strong>BMS consists of a gatable a<strong>stable</strong> multivibrator with logic techniques<br />

incorporated to permit positive or negative edge triggered<br />

mono<strong>stable</strong> multivibrator action with retriggering and external counting<br />

options.<br />

Inputs include +TRIGGER, -TRIGGER, ASTABLE, ASTABLE,<br />

RETRIGGER, and EXTERNAL RESET. Buffered outputs are Q, Q, and<br />

OSCILLATOR. In all modes of operation, an external capacitor must be<br />

connected between C-Timing and RC-Common terminals, and an<br />

external resistor must be connected between the R-Timing and RC-<br />

Common terminals.<br />

A<strong>stable</strong> operation is enabled by a high level on the ASTABLE input or a<br />

low level on the ASTABLE input, or both. The period of the square wave<br />

at the Q and Q Outputs in this mode of operation is a function of the<br />

external components employed. “True” input pulses on the ASTABLE<br />

input or “Complement” pulses on the ASTABLE input allow the circuit to<br />

be used as a gatable multivibrator. The OSCILLATOR output period will<br />

be half of the Q terminal output in the a<strong>stable</strong> mode. However, a 50%<br />

duty cycle is not guaranteed at this output.<br />

The CD<strong>4047</strong>BMS triggers in the mono<strong>stable</strong> mode when a positive<br />

going edge occurs on the +TRIGGER input while the -TRIGGER is held<br />

low. Input pulses may be of any duration relative to the output pulse.<br />

If retrigger capability is desired, the RETRIGGER input is pulsed. The<br />

retriggerable mode of operation is limited to positive going edge. The<br />

CD<strong>4047</strong>BMS will retrigger as long as the RETRIGGER input is high,<br />

with or without transitions (See Figure 31)<br />

An external countdown option can be implemented by coupling “Q” to<br />

an external “N” counter and resetting the counter with trigger pulse. The<br />

counter output pulse is fed back to the ASTABLE input and has a duration<br />

equal to N times the period of the multivibrator.<br />

A high level on the EXTERNAL RESET input assures no output pulse<br />

during an “ON” power condition. This input can also be activated to terminate<br />

the output pulse at any time. For mono<strong>stable</strong> operation, whenever<br />

VDD is applied, an internal power on reset circuit will clock the Q<br />

output low within one output period (tM).<br />

The CD<strong>4047</strong>BMS is supplied in these 14-lead outline packages:<br />

Braze Seal DIP H4Q<br />

Frit Seal DIP H1B<br />

Ceramic Flatpack H3W<br />

Pinout<br />

C 1<br />

R 2<br />

R-C COMMON 3<br />

ASTABLE 4<br />

ASTABLE 5<br />

-TRIGGER 6<br />

VSS 7<br />

CD<strong>4047</strong>BMS<br />

TOP VIEW<br />

14 VDD<br />

13 OSC OUT<br />

12 RETRIGGER<br />

11 Q<br />

10 Q<br />

9 EXT. RESET<br />

8 +TRIGGER<br />

File Number 3313

Specifications CD<strong>4047</strong>BMS<br />

Absolute Maximum Ratings Reliability Information<br />

DC Supply Voltage Range, (VDD) . . . . . . . . . . . . . . . -0.5V to +20V<br />

(Voltage Referenced to VSS Terminals)<br />

Input Voltage Range, All Inputs . . . . . . . . . . . . .-0.5V to VDD +0.5V<br />

DC Input Current, Any One Input . . . . . . . . . . . . . . . . . . . . . . . .±10mA<br />

Operating Temperature Range. . . . . . . . . . . . . . . . -55 o C to +125 o C<br />

Package Types D, F, K, H<br />

Storage Temperature Range (TSTG) . . . . . . . . . . . -65 o C to +150 o C<br />

Lead Temperature (During Soldering) . . . . . . . . . . . . . . . . . +265 o C<br />

At Distance 1/16 ± 1/32 Inch (1.59mm ± 0.79mm) from case for<br />

10s Maximum<br />

TABLE 1. DC ELECTRICAL PERFORMANCE CHARACTERISTICS<br />

7-898<br />

Thermal Resistance . . . . . . . . . . . . . . . . θ ja θ jc<br />

Ceramic DIP and FRIT Package . . . . . 80 o C/W 20 o C/W<br />

Flatpack Package . . . . . . . . . . . . . . . . 70 o C/W 20 o C/W<br />

Maximum Package Power Dissipation (PD) at +125 o C<br />

For TA = -55 o C to +100 o C (Package Type D, F, K) . . . . . . 500mW<br />

For TA = +100 o C to +125 o C (Package Type D, F, K) . . . . .Derate<br />

Linearity at 12mW/ o C to 200mW<br />

Device Dissipation per Output Transistor . . . . . . . . . . . . . . . 100mW<br />

For TA = Full Package Temperature Range (All Package Types)<br />

Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +175 o C<br />

GROUP A<br />

LIMITS<br />

PARAMETER SYMBOL CONDITIONS (NOTE 1) SUBGROUPS TEMPERATURE MIN MAX UNITS<br />

Supply Current IDD VDD = 20V, VIN = VDD or GND 1 +25 oC - 2 µA<br />

2 +125oC - 200 µA<br />

VDD = 18V, VIN = VDD or GND 3 -55oC - 2 µA<br />

Input Leakage Current IIL VIN = VDD or GND VDD = 20 1 +25o C -100 - nA<br />

2 +125oC -1000 - nA<br />

VDD = 18V 3 -55oC -100 - nA<br />

Input Leakage Current IIH VIN = VDD or GND VDD = 20 1 +25oC - 100 nA<br />

2 +125oC - 1000 nA<br />

VDD = 18V 3 -55oC - 100 nA<br />

Input Leakage Curent IIL VDD = 24V, VIN = 11V or GND 1 +25<br />

(Pin 3)<br />

oC -300 - nA<br />

2 +125oC -10 - µA<br />

Input Leakage Current IIH VDD = 26V, VIN = 13V or GND 1 +25<br />

(Pin 3)<br />

oC - 300 nA<br />

2 +125oC - 10 µA<br />

Output Voltage VOL15 VDD = 15V, No Load 1, 2, 3 +25oC, +125oC, -55oC - 50 mV<br />

Output Voltage VOH15 VDD = 15V, No Load (Note 3) 1, 2, 3 +25oC, +125oC, -55oC 14.95 - V<br />

Output Current (Sink)<br />

Q, Q, OSC Out<br />

IOL5 VDD = 5V, VOUT = 0.4V 1 +25oC 0.53 - mA<br />

Output Current (Sink)<br />

Q, Q, OSC Out<br />

Output Current (Sink)<br />

Q, Q, OSC Out<br />

Output Current (Source)<br />

Q, Q, OSC Out<br />

Output Current (Source)<br />

Q, Q, OSC Out<br />

Output Current (Source)<br />

Q, Q, OSC Out<br />

Output Current (Source)<br />

Q, Q, OSC Out<br />

IOL10 VDD = 10V, VOUT = 0.5V 1 +25 o C 1.4 - mA<br />

IOL15 VDD = 15V, VOUT = 1.5V 1 +25 o C 3.5 - mA<br />

IOH5A VDD = 5V, VOUT = 4.6V 1 +25 o C - -0.53 mA<br />

IOH5B VDD = 5V, VOUT = 2.5V 1 +25 o C - -1.8 mA<br />

IOH10 VDD = 10V, VOUT = 9.5V 1 +25 o C - -1.4 mA<br />

IOH15 VDD = 15V, VOUT = 13.5V 1 +25 o C - -3.5 mA<br />

Output Current (Sink) IOL5RC VDD = 5V, VOUT = 0.4V 1 +25oC 0.78 - mA<br />

Output Current (Sink) IOL10RC VDD = 10V, VOUT = 0.5V 1 +25oC 2.0 - mA<br />

Output Current (Sink) IOL15RC VDD = 15V, VOUT = 1.5V 1 +25 o C 5.2 - mA<br />

Output Current (Source) IOH5RC VDD = 5V, VOUT = 4.6V 1 +25 o C - -0.78 mA<br />

Output Current (Source) IOH10RC VDD = 10V, VOUT = 9.5V 1 +25 o C - -2 mA<br />

Output Current (Source) IOH15RC VDD = 15V, VOUT = 13.5V 1 +25 o C - -5.2 mA<br />

N Threshold Voltage VNTH VDD = 10V, ISS = -10µA 1 +25 o C -2.8 -0.7 V

Specifications CD<strong>4047</strong>BMS<br />

P Threshold Voltage VPTH VSS = 0V, IDD = 10µA 1 +25oC 0.7 2.8 V<br />

Functional F VDD = 2.8V, VIN = VDD or GND 7 +25oC VOH > VOL < V<br />

VDD = 20V, VIN = VDD or GND 7 +25<br />

VDD/2 VDD/2<br />

oC VDD = 18V, VIN = VDD or GND 8A +125oC VDD = 3V, VIN = VDD or GND 8B -55oC Input Voltage Low<br />

(Note 2)<br />

VIL VDD = 5V, VOH > 4.5V, VOL < 0.5V 1, 2, 3 +25oC, +125oC, -55oC - 1.5 V<br />

Input Voltage High<br />

(Note 2)<br />

Input Voltage Low<br />

(Note 2)<br />

Input Voltage High<br />

(Note 2)<br />

TABLE 1. DC ELECTRICAL PERFORMANCE CHARACTERISTICS (Continued)<br />

PARAMETER SYMBOL CONDITIONS (NOTE 1)<br />

VIH VDD = 5V, VOH > 4.5V, VOL < 0.5V 1, 2, 3 +25 o C, +125 o C, -55 o C 3.5 - V<br />

VIL VDD = 15V, VOH > 13.5V,<br />

VOL < 1.5V<br />

VIH VDD = 15V, VOH > 13.5V,<br />

VOL < 1.5V<br />

NOTES:<br />

1. All voltages referenced to device GND, 100% testing being implemented<br />

2. Go/No Go test with limits applied to inputs.<br />

3. For accuracy, voltage is measured differentially to VDD. Limit is 0.050V max..<br />

7-899<br />

GROUP A<br />

SUBGROUPS TEMPERATURE<br />

LIMITS<br />

MIN MAX<br />

1, 2, 3 +25 o C, +125 o C, -55 o C - 4 V<br />

1, 2, 3 +25 o C, +125 o C, -55 o C 11 - V<br />

TABLE 2. AC ELECTRICAL PERFORMANCE CHARACTERISTICS<br />

(NOTES 1, 2)<br />

GROUP A<br />

LIMITS<br />

PARAMETER SYMBOL CONDITIONS SUBGROUPS TEMPERATURE MIN MAX UNITS<br />

Propagation Delay TPLH1 VDD = 5V, VIN = VDD or GND 9 +25<br />

A<strong>stable</strong>, A<strong>stable</strong> to OSC<br />

oC - 400 ns<br />

10, 11 +125oC, -55oC - 540 ns<br />

Propagation Delay TPHL3 VDD = 5V, VIN = VDD or GND 9 +25<br />

Trigger to Q, Q<br />

TPLH3<br />

oC - 1000 ns<br />

10, 11 +125oC, -55oC - 1350 ns<br />

Propagation Delay TPLH2 VDD = 5V, VIN = VDD or GND 9 +25<br />

(Note 2)<br />

A<strong>stable</strong> or A<strong>stable</strong> to Q, Q<br />

TPLH2<br />

oC - 700 ns<br />

10, 11 +125oC, -55oC - 945 ns<br />

Propagation Delay TPHL4 VDD = 5V, VIN = VDD or GND 9 +25<br />

(Note 2)<br />

Retrigger to Q, Q<br />

TPLH4<br />

oC - 600 ns<br />

10, 11 +125oC, -55oC - 810 ns<br />

Propagation Delay TPLH5 VDD = 5V, VIN = VDD or GND 9 +25<br />

(Note 2)<br />

Reset to Q, Q<br />

TPLH5<br />

oC - 500 ns<br />

10, 11 +125o C, -55 o C - 675 ns<br />

Transition Time TTHL VDD = 5V, VIN = VDD or GND 9 +25<br />

TTLH<br />

o C - 200 ns<br />

10, 11 +125 o C, -55 o NOTES:<br />

C - 270 ns<br />

1. VDD = 5V, CL = 50pF, RL = 200K; input TR, TF < 20ns.<br />

2. -55 o C and +125 o C limits guaranteed, 100% testing being implemented.<br />

UNITS

Specifications CD<strong>4047</strong>BMS<br />

TABLE 3. ELECTRICAL PERFORMANCE CHARACTERISTICS<br />

PARAMETER SYMBOL CONDITIONS NOTES TEMPERATURE MIN MAX UNITS<br />

Supply Current IDD VDD = 5V, VIN = VDD or GND 1, 2 -55oC, +25oC - 1 µA<br />

+125 o C - 30 µA<br />

VDD = 10V, VIN = VDD or GND 1, 2 -55 o C, +25 o C - 2 µA<br />

+125 oC - 60 µA<br />

VDD = 15V, VIN = VDD or GND 1, 2 -55oC, +25oC - 2 µA<br />

+125oC - 120 µA<br />

Output Voltage VOL VDD = 5V, No Load 1, 2 +25 oC, +125oC, -55o C<br />

- 50 mV<br />

Output Voltage VOL VDD = 10V, No Load 1, 2 +25 o C, +125 o C,<br />

-55 o C<br />

Output Voltage VOH VDD = 5V, No Load 1, 2 +25 o C, +125 o C,<br />

-55 o C<br />

Output Voltage VOH VDD = 10V, No Load 1, 2 +25 o C, +125 o C,<br />

-55 o C<br />

7-900<br />

LIMITS<br />

- 50 mV<br />

4.95 - V<br />

9.95 - V<br />

Output Current (Sink) IOL5 VDD = 5V, VOUT = 0.4V 1, 2 +125 oC 0.36 - mA<br />

-55oC 0.64 - mA<br />

Output Current (Sink) IOL10 VDD = 10V, VOUT = 0.5V 1, 2 +125 o C 0.9 - mA<br />

-55 oC 1.6 - mA<br />

Output Current (Sink) IOL15 VDD = 15V, VOUT = 1.5V 1, 2 +125oC 2.4 - mA<br />

-55 oC 4.2 - mA<br />

Output Current (Source) IOH5A VDD = 5V, VOUT = 4.6V 1, 2 +125oC - -0.36 mA<br />

-55 o C - -0.64 mA<br />

Output Current (Source) IOH5B VDD = 5V, VOUT = 2.5V 1, 2 +125 oC - -1.15 mA<br />

-55oC - -2.0 mA<br />

Output Current (Source) IOH10 VDD = 10V, VOUT = 9.5V 1, 2 +125 oC - -0.9 mA<br />

-55oC - -1.6 mA<br />

Output Current (Source) IOH15 VDD =15V, VOUT = 13.5V 1, 2 +125 o C - -2.4 mA<br />

-55 oC - -4.2 mA<br />

Input Voltage Low VIL VDD = 10V, VOH > 9V, VOL < 1V 1, 2 +25oC, +125oC, -55oC - 3 V<br />

Input Voltage High VIH VDD = 10V, VOH > 9V, VOL < 1V 1, 2 +25 o C, +125 o C,<br />

-55 o C<br />

Propagation Delay<br />

A<strong>stable</strong>, A<strong>stable</strong> to OSC<br />

Propagation Delay<br />

A<strong>stable</strong> or A<strong>stable</strong> to Q, Q<br />

Propagation Delay<br />

Trigger to Q, Q<br />

Propagation Delay<br />

Retrigger to Q, Q<br />

Propagation Delay<br />

Reset to Q, Q<br />

+7 - V<br />

TPLH1 VDD = 10V 1, 2, 3 +25oC - 200 ns<br />

VDD = 15V 1, 2, 3 +25oC - 160 ns<br />

TPLH2<br />

TPHL2<br />

TPHL3<br />

TPLH3<br />

TPHL4<br />

TPLH4<br />

TPLH5<br />

TPLH5<br />

Transition Time TTHL<br />

TTLH<br />

VDD = 10V 1, 2, 3 +25oC - 350 ns<br />

VDD = 15V 1, 2, 3 +25o C - 250 ns<br />

VDD = 10V 1, 2, 3 +25 o C - 450 ns<br />

VDD = 15V 1, 2, 3 +25oC - 300 ns<br />

VDD = 10V 1, 2, 3 +25oC - 300 ns<br />

VDD = 15V 1, 2, 3 +25oC - 200 ns<br />

VDD = 10V 1, 2, 3 +25 o C - 200 ns<br />

VDD = 15V 1, 2, 3 +25o C - 140 ns<br />

VDD = 10V 1, 2, 3 +25 o C - 100 ns<br />

VDD = 15V 1, 2, 3 +25oC - 80 ns

Q or Q Deviation from<br />

50% Duty Factor<br />

Minimum Pulse Width<br />

+ Trigger<br />

- Trigger<br />

Minimum Pulse Width<br />

Reset<br />

Specifications CD<strong>4047</strong>BMS<br />

TABLE 3. ELECTRICAL PERFORMANCE CHARACTERISTICS (Continued)<br />

PARAMETER SYMBOL CONDITIONS NOTES TEMPERATURE<br />

QD VDD = 5V 1, 2, 3 +25oC - ±1 %<br />

VDD = 10V 1, 2, 3 +25 o C - ±1 %<br />

VDD = 15V 1, 2, 3 +25 o C - ±0.5 %<br />

TW VDD = 5V 1, 2, 3 +25 oC - 400 ns<br />

VDD = 10V 1, 2, 3 +25oC - 160 ns<br />

VDD = 15V 1, 2, 3 +25oC - 100 ns<br />

TW VDD = 5V 1, 2, 3 +25 oC - 200 ns<br />

VDD = 10V 1, 2, 3 +25o C - 100 ns<br />

VDD = 15V 1, 2, 3 +25 o C - 60 ns<br />

Minimum Retrigger Pulse TW VDD = 5V 1, 2, 3 +25<br />

Width<br />

oC - 600 ns<br />

VDD = 10V 1, 2, 3 +25 o C - 230 ns<br />

VDD = 15V 1, 2, 3 +25 o C - 150 ns<br />

Input Capacitance CIN Any Input 1, 2 +25o NOTES:<br />

C - 7.7 pF<br />

1. All voltages referenced to device GND.<br />

2. The parameters listed on Table 3 are controlled via design or process and are not directly tested. These parameters are characterized<br />

on initial design release and upon design changes which would affect these characteristics.<br />

3. CL = 50pF, RL = 200K, Input TR, TF < 20ns.<br />

TABLE 4. POST IRRADIATION ELECTRICAL PERFORMANCE CHARACTERISTICS<br />

PARAMETER SYMBOL CONDITIONS NOTES TEMPERATURE MIN MAX UNITS<br />

Supply Current IDD VDD = 20V, VIN = VDD or GND 1, 4 +25 oC - 7.5 µA<br />

N Threshold Voltage VNTH VDD = 10V, ISS = -10µA 1, 4 +25oC -2.8 -0.2 V<br />

N Threshold Voltage<br />

Delta<br />

∆VTN VDD = 10V, ISS = -10µA 1, 4 +25oC - ±1 V<br />

7-901<br />

LIMITS<br />

P Threshold Voltage VTP VSS = 0V, IDD = 10µA 1, 4 +25oC 0.2 2.8 V<br />

P Threshold Voltage<br />

Delta<br />

∆VTP VSS = 0V, IDD = 10µA 1, 4 +25oC - ±1 V<br />

Functional F VDD = 18V, VIN = VDD or GND 1 +25oC VOH > VOL <<br />

VDD = 3V, VIN = VDD or GND<br />

VDD/2 VDD/2<br />

Propagation Delay Time TPHL VDD = 5V 1, 2, 3, 4 +25<br />

TPLH<br />

oC - 1.35 x<br />

+25oC Limit<br />

NOTES: 1. All voltages referenced to device GND.<br />

2. CL = 50pF, RL = 200K, Input TR, TF < 20ns.<br />

3. See Table 2 for +25oC limit.<br />

4. Read and Record<br />

TABLE 5. BURN-IN AND LIFE TEST DELTA PARAMETERS +25 O C<br />

PARAMETER SYMBOL DELTA LIMIT<br />

Supply Current - MSI-1 IDD ± 0.2µA<br />

Output Current (Sink) IOL5 ± 20% x Pre-Test Reading<br />

Output Current (Source) IOH5A ± 20% x Pre-Test Reading<br />

LIMITS<br />

MIN MAX<br />

UNITS<br />

V<br />

ns

Specifications CD<strong>4047</strong>BMS<br />

TABLE 6. APPLICABLE SUBGROUPS<br />

CONFORMANCE GROUP<br />

MIL-STD-883<br />

METHOD GROUP A SUBGROUPS READ AND RECORD<br />

Initial Test (Pre Burn-In) 100% 5004 1, 7, 9 IDD, IOL5, IOH5A<br />

Interim Test 1 (Post Burn-In) 100% 5004 1, 7, 9 IDD, IOL5, IOH5A<br />

Interim Test 2 (Post Burn-In) 100% 5004 1, 7, 9 IDD, IOL5, IOH5A<br />

PDA (Note 1) 100% 5004 1, 7, 9, Deltas<br />

Interim Test 3 (Post Burn-In) 100% 5004 1, 7, 9 IDD, IOL5, IOH5A<br />

PDA (Note 1) 100% 5004 1, 7, 9, Deltas<br />

Final Test 100% 5004 2, 3, 8A, 8B, 10, 11<br />

Group A Sample 5005 1, 2, 3, 7, 8A, 8B, 9, 10, 11<br />

Group B Subgroup B-5 Sample 5005 1, 2, 3, 7, 8A, 8B, 9, 10, 11, Deltas Subgroups 1, 2, 3, 9, 10, 11<br />

Subgroup B-6 Sample 5005 1, 7, 9<br />

Group D Sample 5005 1, 2, 3, 8A, 8B, 9 Subgroups 1, 2 3<br />

NOTE: 1. 5% Parameteric, 3% Functional; Cumulative for Static 1 and 2.<br />

TABLE 7. TOTAL DOSE IRRADIATION<br />

MIL-STD-883<br />

TEST READ AND RECORD<br />

CONFORMANCE GROUPS METHOD PRE-IRRAD POST-IRRAD PRE-IRRAD POST-IRRAD<br />

Group E Subgroup 2 5005 1, 7, 9 Table 4 1, 9 Table 4<br />

TABLE 8. BURN-IN AND IRRADIATION TEST CONNECTIONS<br />

FUNCTION OPEN GROUND VDD 9V ± -0.5V<br />

50kHz 25kHz<br />

Static Burn-In 1<br />

Note 1<br />

1, 2, 10, 11, 13 3-9, 12 14<br />

Static Burn-In 2<br />

Note 1<br />

1, 2, 10, 11, 13 7 3-6, 8, 9, 12, 14<br />

Dynamic Burn-<br />

In Note 1<br />

- 7, 9, 12 4, 5, 14 1, 2, 10, 11, 13 6, 8 3<br />

Irradiation<br />

Note 2<br />

NOTE:<br />

1, 2, 10, 11, 13 7 3-6, 8, 9, 12, 14<br />

1. Each pin except VDD and GND will have a series resistor of 10K ± 5%, VDD = 18V ± 0.5V<br />

2. Each pin except VDD and GND will have a series resistor of 47K ± 5%; Group E, Subgroup 2, sample size is 4 dice/wafer, 0 failures,<br />

VDD = 10V ± 0.5V<br />

7-902<br />

OSCILLATOR

CD<strong>4047</strong>BMS<br />

TABLE 9. FUNCTIONAL TERMINAL CONNECTIONS<br />

In all cases External resistor between terminals 2 and 3 (Note 1)<br />

External capacitor between terminals 1 and 3 (Note 1)<br />

TERMINAL CONNECTIONS OUTPUT PULSE OUTPUT PERIOD OR PULSE<br />

FUNCTION<br />

ASTABLE MULTIVIBRATOR<br />

TO VDD TO VSS INPUT TO FROM<br />

WIDTH<br />

Free Running 4, 5, 6, 14 7, 8, 9, 12 - 10, 11, 13 TA (10, 11) = 4.40 RC<br />

True Gating 4, 6, 14 7, 8, 9, 12 5 10, 11, 13 TA (13) = 2.20 RC (Note 2)<br />

Complement Gating<br />

MONOSTABLE MULTIVIBRATOR<br />

6, 14 5, 7, 8, 9, 12 4 10, 11, 13<br />

Positive Edge Trigger 4, 14 5, 6, 7, 9, 12 8 10, 11 tM (10, 11) = 2.48 RC<br />

Negative Edge Trigger 4, 8, 14 5, 7, 9, 12 6 10, 11<br />

Retriggerable 4, 14 5, 6, 7, 9 8, 12 10, 11<br />

External Countdown (Note 3)<br />

NOTES:<br />

1. See text.<br />

14 5, 6, 7, 8, 9, 12 - 10, 11<br />

2. First positive 1 / 2 cycle pulse width = 2.48 RC. See note follow <strong>Mono</strong><strong>stable</strong> Mode Design Information.<br />

3. Input Pulse to Reset of External Counting Chip External Counting Chip Output to Terminal 4.<br />

Logic Diagrams<br />

5<br />

4<br />

6<br />

8<br />

12<br />

9<br />

ASTABLE<br />

ASTABLE<br />

-TRIGGER<br />

+TRIGGER<br />

RETRIGGER<br />

EXTERNAL<br />

RESET<br />

ASTABLE<br />

GATE<br />

CONTROL<br />

MONOSTABLE<br />

CONTROL<br />

C-TIMING<br />

RC<br />

COMMON<br />

3<br />

C<br />

LOW POWER<br />

ASTABLE<br />

MULTIVIBRATOR<br />

RETRIGGER<br />

CONTROL<br />

FIGURE 1. CD<strong>4047</strong>BMS LOGIC BLOCK DIAGRAM<br />

1<br />

7-903<br />

R<br />

2<br />

R-TIMING<br />

OSCILLATOR OUT<br />

FREQUENCY<br />

DIVIDER (÷2)<br />

Q<br />

Q<br />

13<br />

10<br />

11

Logic Diagrams (Continued)<br />

*<br />

ASTABLE 5<br />

*<br />

ASTABLE 4<br />

*<br />

+TRIGGER 8<br />

*<br />

-TRIGGER 6<br />

VDD<br />

VSS<br />

EXTERNAL<br />

RESET<br />

14<br />

7<br />

*<br />

9<br />

* INPUTS PROTECTED<br />

BY CMOS<br />

PROTECTION<br />

NETWORK<br />

CL<br />

CL<br />

S<br />

D Q<br />

Q<br />

R<br />

FF2, FF4<br />

CL<br />

CL<br />

VDD<br />

VDD<br />

VSS<br />

D Q<br />

FF1<br />

D Q<br />

CL<br />

CL<br />

R1 R2<br />

R1 R2<br />

FF1, FF3<br />

D<br />

CD<strong>4047</strong>BMS<br />

*<br />

RETRIGGER 12<br />

VSS<br />

FIGURE 2. CD<strong>4047</strong>BMS LOGIC DIAGRAM<br />

CL<br />

p<br />

n<br />

CL<br />

(a)<br />

(b)<br />

FIGURE 3. DETAIL LOGIC DIAGRAM FOR FLIP-FLOPS FF1 AND FF3 (a) AND FOR FLIP-FLOPS FF2 AND FF4 (b)<br />

7-904<br />

VDD<br />

S<br />

D Q<br />

FF2<br />

CL<br />

CL Q<br />

R<br />

3 RC<br />

**<br />

COMMON<br />

CAUTION: Terminal 3 is more sensitive<br />

to static electrical discharge. Extra<br />

handling precautions are recommended.<br />

D<br />

S<br />

CL<br />

p<br />

n<br />

CL<br />

CL<br />

p<br />

n<br />

CL<br />

R<br />

CL<br />

p<br />

n<br />

CL<br />

R1 R2<br />

CL<br />

p<br />

n<br />

CL<br />

CL<br />

p<br />

n<br />

CL<br />

D Q<br />

FF3<br />

CL<br />

CL<br />

R1 R2<br />

R2 R1<br />

R<br />

CL<br />

p<br />

n<br />

CL<br />

CTC<br />

S<br />

D Q<br />

FF4<br />

CL<br />

CL<br />

R<br />

1<br />

** SPECIAL<br />

RC COMMON<br />

PROTECTION<br />

NETWORK<br />

Q<br />

S<br />

CL<br />

p<br />

n<br />

CL<br />

2 RTC<br />

Q<br />

Q<br />

OSC<br />

OUT<br />

13<br />

10<br />

11<br />

VDD<br />

VSS<br />

Q<br />

Q

Typical Performance Characteristics<br />

OUTPUT LOW (SINK) CURRENT (IOL) (mA)<br />

30<br />

25<br />

20<br />

15<br />

10<br />

5<br />

AMBIENT TEMPERATURE (T A ) = +25 o C<br />

GATE-TO-SOURCE VOLTAGE (VGS) = 15V<br />

5V<br />

10V<br />

0 5 10 15<br />

DRAIN-TO-SOURCE VOLTAGE (VDS) (V)<br />

FIGURE 4. TYPICAL OUTPUT LOW (SINK) CURRENT<br />

CHARACTERISTICS<br />

PROPAGATION DELAY TIME (t PHL , t PLH) (ns)<br />

AMBIENT TEMPERATURE (T A ) = +25 o C<br />

FIGURE 6. TYP. OUTPUT HIGH (SOURCE) CURRENT<br />

CHARACTERISTICS<br />

400<br />

300<br />

200<br />

100<br />

GATE-TO-SOURCE VOLTAGE (VGS) = -5V<br />

0<br />

DRAIN-TO-SOURCE VOLTAGE (VDS) (V)<br />

-15 -10 -5<br />

-15V<br />

-10V<br />

0<br />

0<br />

FIGURE 8. TYP. PROPAGATION DELAY TIME AS A FUNCTION OF<br />

LOAD CAPACITANCE (ASTABLE, ASTABLE TO Q, Q)<br />

CD<strong>4047</strong>BMS<br />

-2.5<br />

-5<br />

-7.5<br />

-10<br />

-12.5<br />

-15<br />

SUPPLY VOLTAGE (VDD) = 5V<br />

10V<br />

15V<br />

AMBIENT TEMPERATURE (T A ) = +25 o C<br />

20 40 60 80 100<br />

LOAD CAPACITANCE (CL) (pF)<br />

OUTPUT HIGH (SOURCE) CURRENT (IOH) (mA)<br />

PROPAGATION DELAY TIME (t PHL , t PLH ) (ns)<br />

7-905<br />

OUTPUT LOW (SINK) CURRENT (IOL) (mA)<br />

15.0<br />

12.5<br />

10.0<br />

7.5<br />

5.0<br />

2.5<br />

AMBIENT TEMPERATURE (T A ) = +25 o C<br />

GATE-TO-SOURCE VOLTAGE (VGS) = 15V<br />

5V<br />

10V<br />

0 5 10 15<br />

DRAIN-TO-SOURCE VOLTAGE (VDS) (V)<br />

FIGURE 5. MINIMUM OUTPUT LOW (SINK) CURRENT<br />

CHARACTERISTICS<br />

DRAIN-TO-SOURCE VOLTAGE (VDS) (V)<br />

-15 -10 -5<br />

AMBIENT TEMPERATURE (T A ) = +25 o C<br />

GATE-TO-SOURCE VOLTAGE (VGS) = -5V<br />

-15V<br />

-10V<br />

0<br />

0<br />

FIGURE 7. MINIMUM OUTPUT HIGH (SOURCE) CURRENT<br />

CHARACTERISTICS<br />

600<br />

400<br />

200<br />

0<br />

AMBIENT TEMPERATURE (T A ) = +25 o C<br />

SUPPLY VOLTAGE (VDD) = 5V<br />

10V<br />

15V<br />

FIGURE 9. TYP. PROPAGATION DELAY TIME AS A FUNCTION<br />

OF LOAD CAPACITANCE (+ OR - TRIGGER TO Q, Q)<br />

-2.5<br />

-5<br />

-7.5<br />

OUTPUT HIGH (SOURCE) CURRENT (IOH) (mA)<br />

20 40 60 80 100<br />

LOAD CAPACITANCE (CL) (pF)

FIGURE 10. TYP. TRANSITION TIME AS A FUNCTION OF LOAD<br />

CAPACITANCE<br />

FIGURE 12. TYP. ASTABLE OSCILLATOR OR Q, Q PERIOD<br />

ACCURACY vs SUPPLY VOLTAGE<br />

FIGURE 14. TYP. ASTABLE OSCILLATOR OR Q, Q PERIOD<br />

ACCURACY vs AMBIENT TEMPERATURE (ULTRA<br />

LOW FREQ.)<br />

CD<strong>4047</strong>BMS<br />

Typical Performance Characteristics (Continued)<br />

TRANSITION TIME (fTHL, fTLH) (ns)<br />

PERIOD ACCURACY (%)<br />

PERIOD ACCURACY (%)<br />

200<br />

150<br />

100<br />

50<br />

AMBIENT TEMPERATURE (T A ) = +25 o C<br />

SUPPLY VOLTAGE (VDD) = 5V<br />

0<br />

0 20 40 60 80 100<br />

LOAD CAPACITANCE (CL) (pF)<br />

4<br />

3<br />

2<br />

1<br />

0<br />

-1<br />

-2<br />

-3<br />

-4<br />

AMBIENT TEMPERATURE (T A ) = +25 o C<br />

CX = 0.01µF<br />

100kΩ<br />

RX = 1MΩ<br />

10V<br />

15V<br />

0 2 4 6 8 10 12 14 16 18 20<br />

SUPPLY VOLTAGE (VDD) (V)<br />

1 CX = 1µF<br />

RX = 1MΩ<br />

0<br />

-1<br />

-2<br />

10MΩ<br />

10kΩ<br />

SUPPLY VOLTAGE (VDD) = 5V<br />

10V, 15V<br />

10MΩ<br />

10kΩ<br />

1MΩ<br />

100kΩ<br />

10V, 15V<br />

-55 -15 25 65 105 145<br />

AMBIENT TEMPERATURE (TA ) ( o -3<br />

C)<br />

5V<br />

7-906<br />

PERIOD ACCURACY (%)<br />

4<br />

3<br />

2<br />

1<br />

0<br />

-1<br />

AMBIENT TEMPERATURE (T A ) = +25 o C<br />

CX = 1µF<br />

10MΩ<br />

1MΩ AND 100kΩ<br />

10kΩ<br />

10MΩ<br />

-2<br />

-3<br />

RX = 1MΩ AND<br />

100kΩ<br />

-4<br />

10kΩ<br />

0 2 4 6 8 10 12 14 16 18 20<br />

SUPPLY VOLTAGE (VDD) (V)<br />

FIGURE 11. TYP. ASTABLE OSCILLATOR OR Q, Q PERIOD<br />

ACCURACY vs SUPPLY VOLTAGE<br />

PERIOD ACCURACY (%)<br />

4<br />

3<br />

2<br />

1<br />

0<br />

-1<br />

-2<br />

AMBIENT TEMPERATURE (T A ) = +25 o C<br />

CX = 1000pF<br />

RX = 1MΩ AND<br />

10kΩ<br />

100kΩ<br />

10kΩ<br />

1MΩ AND<br />

10kΩ 10MΩ<br />

-3<br />

10kΩ<br />

-4<br />

0 2 4 6 8 10 12 14 16 18 20<br />

SUPPLY VOLTAGE (VDD) (V)<br />

FIGURE 13. TYP. ASTABLE OSCILLATOR OR Q, Q PERIOD<br />

ACCURACY vs SUPPLY VOLTAGE<br />

PERIOD ACCURACY (%)<br />

2<br />

1<br />

0<br />

-1<br />

-2<br />

-55<br />

CX = 0.1µF<br />

RX = 1MΩ<br />

5V<br />

10V<br />

15V<br />

SUPPLY VOLTAGE (VDD) = 5V<br />

15V<br />

10V<br />

AMBIENT TEMPERATURE (TA ) ( o -15 25 65 105 145<br />

C)<br />

FIGURE 15. TYP. ASTABLE OSCILLATOR OR Q, Q PERIOD<br />

ACCURACY vs AMBIENT TEMPERATURE (LOW<br />

FREQ.)

FIGURE 16. TYP. ASTABLE OSCILLATOR OR Q, Q PERIOD<br />

ACCURACY vs AMBIENT TEMPERATURE (MEDIUM<br />

FREQ.)<br />

FIGURE 18. TYPICAL ASTABLE OSCILLATOR OR Q, Q PERIOD<br />

ACCURACY vs AMBIENT TEMPERATURE<br />

FIGURE 20. TYPICAL OUTPUT PULSE WIDTH VARIATIONS vs<br />

SUPPLY VOLTAGE<br />

CD<strong>4047</strong>BMS<br />

Typical Performance Characteristics (Continued)<br />

PERIOD ACCURACY (%)<br />

PERIOD ACCURACY (%)<br />

OUTPUT PULSE-WIDTH VARIATION (%)<br />

2<br />

1<br />

0<br />

-1<br />

-2<br />

CX = 0.01µF<br />

RX = 100kΩ<br />

5V AND 10V<br />

15V<br />

SUPPLY VOLTAGE (VDD) = 5V, 10V<br />

15V<br />

-55 -15 25 65 105 145<br />

AMBIENT TEMPERATURE (T A ) ( o C)<br />

20<br />

10<br />

0<br />

-10<br />

-55 -15 25 65 105 145<br />

AMBIENT TEMPERATURE (T A ) ( o C)<br />

8<br />

6<br />

4<br />

2<br />

0<br />

-2<br />

-4<br />

-6<br />

-8<br />

RX = 10kΩ<br />

SUPPLY VOLTAGE (VDD) = 5V<br />

0.01µF, 0.1µF, 1µF<br />

0.001µF<br />

CX = 100pF<br />

AMBIENT TEMPERATURE (T A ) = +25 o C<br />

CX = 0.1µF<br />

10MΩ<br />

RX = 10kΩ, 100kΩ, 1MΩ<br />

100pF<br />

0.001µF<br />

0.01µF, 0.1µF, 1µF<br />

10kΩ, 100kΩ, 1MΩ AND 10MΩ<br />

0 5 10 15 20 25<br />

SUPPLY VOLTAGE (VDD) (V)<br />

7-907<br />

PERIOD ACCURACY (%)<br />

12<br />

10<br />

8<br />

6<br />

4<br />

2<br />

0<br />

-2<br />

CX = 1000pF<br />

RX = 10kΩ<br />

10V AND 15V<br />

5V<br />

SUPPLY VOLTAGE (VDD) = 5V<br />

10V, 15V<br />

-55 -15 25 65 105 145<br />

AMBIENT TEMPERATURE (TA ) ( o -4<br />

-35 -5 45 85 125<br />

C)<br />

FIGURE 17. TYP. ASTABLE OSCILLATOR OR Q, Q PERIOD<br />

ACCURACY vs AMBIENT TEMPERATURE (HIGH<br />

FREQ.)<br />

OUTPUT PULSE-WIDTH VARIATION (%)<br />

8<br />

6<br />

4<br />

2<br />

0<br />

-2<br />

-4<br />

-6<br />

-8<br />

AMBIENT TEMPERATURE (T A ) = +25 o C<br />

CX = 1µF<br />

10kΩ<br />

1kΩ<br />

RX = 100kΩ, 1MΩ, 10MΩ<br />

100kΩ<br />

10kΩ, 1MΩ AND 10MΩ<br />

1kΩ<br />

0 5 10 15 20 25<br />

SUPPLY VOLTAGE (VDD) (V)<br />

FIGURE 19. TYPICAL OUTPUT PULSE WIDTH VARIATIONS vs<br />

SUPPLY VOLTAGE<br />

OUTPUT PULSE-WIDTH VARIATION (%)<br />

8<br />

6<br />

4<br />

2<br />

0<br />

-2<br />

-4<br />

-6<br />

-8<br />

AMBIENT TEMPERATURE (T A ) = +25 o C<br />

CX = 1000pF<br />

RX = 1MΩ AND 10Ω<br />

100kΩ<br />

10kΩ<br />

0 5 10 15 20 25<br />

SUPPLY VOLTAGE (VDD) (V)<br />

FIGURE 21. TYPICAL OUTPUT PULSE WIDTH VARIATIONS vs<br />

SUPPLY VOLTAGE

FIGURE 22. TYPICAL OUTPUT PULSE WIDTH VARIATIONS vs<br />

AMBIENT TEMPERATURE<br />

FIGURE 24. TYPICAL OUTPUT PULSE WIDTH VARIATIONS vs<br />

AMBIENT TEMPERATURE<br />

FIGURE 26. TYPICAL POWER DISSIPATION vs OUTPUT<br />

FREQUENCY (VDD = 5V)<br />

CD<strong>4047</strong>BMS<br />

Typical Performance Characteristics (Continued)<br />

OUTPUT PULSE-WIDTH VARIATION (%)<br />

OUTPUT PULSE-WIDTH VARIATION (%)<br />

POWER DISSIPATION (PD) (µW)<br />

8<br />

6<br />

4<br />

2<br />

0<br />

-2<br />

-4<br />

-6<br />

RX = 100kΩ<br />

SUPPLY VOLTAGE (VDD) = 5V<br />

0.001µF<br />

0.1µF<br />

0.01µF<br />

0.1µF<br />

0.01µF<br />

-8<br />

-55 -15 25 65 105 145<br />

AMBIENT TEMPERATURE (TA ) ( o 0.001µF<br />

-35 5 45 85 125<br />

C)<br />

4<br />

2<br />

0<br />

-2<br />

-4<br />

-6<br />

-8<br />

-10<br />

CX = 1000pF<br />

SUPPLY VOLTAGE (VDD) = 5V OR 10V<br />

-55 -15 25 65 105 145<br />

AMBIENT TEMPERATURE (TA ) ( o -12<br />

-35 5 45 85 125<br />

C)<br />

10 5<br />

10 4<br />

10 3<br />

10 2<br />

10 1<br />

10 0<br />

100kΩ<br />

10kΩ<br />

10MΩ<br />

RX = 1MΩ<br />

ASTABLE MODE<br />

SUPPLY VOLTAGE (VDD) = 5V<br />

C = 0.1µF<br />

C = 0.01µF<br />

C =1000pF<br />

10MΩ<br />

10kΩ<br />

100kΩ<br />

1MΩ<br />

10 -1 10 0 10 1 10 2 10 3 10 4 10 5 10 6<br />

Q OR Q FREQUENCY (F) (Hz)<br />

C =100pF<br />

C =10pF<br />

7-908<br />

OUTPUT PULSE-WIDTH VARIATION (%)<br />

RX = 100kΩ<br />

SUPPLY VOLTAGE (VDD) = 10V OR 15V<br />

-12<br />

-50<br />

AMBIENT TEMPERATURE (TA ) ( o 10<br />

8<br />

6<br />

4<br />

CX = 100pF<br />

2<br />

0.01µF<br />

0<br />

-2<br />

-4<br />

0.1µF, 0.01µF<br />

-6<br />

-8<br />

0.1µF AND 0.001µF<br />

0.001µF<br />

-10<br />

100pF<br />

-35 -15 5 25 45 65 85 105 125 145<br />

C)<br />

FIGURE 23. TYPICAL OUTPUT PULSE WIDTH VARIATIONS vs<br />

AMBIENT TEMPERATURE<br />

OUTPUT PULSE-WIDTH VARIATION (%)<br />

4<br />

2<br />

0<br />

-2<br />

-4<br />

-6<br />

-8<br />

-10<br />

-12<br />

-50<br />

10MΩ<br />

RX = 1MΩ<br />

10kΩ<br />

CX = 1000pF<br />

SUPPLY VOLTAGE (VDD) = 15V<br />

100kΩ<br />

10MΩ<br />

10kΩ<br />

100kΩ<br />

AMBIENT TEMPERATURE (TA ) ( o -35 -15 5 25 45 65 85 105 125 145<br />

C)<br />

FIGURE 25. TYPICAL OUTPUT PULSE WIDTH VARIATIONS vs<br />

AMBIENT TEMPERATURE<br />

POWER DISSIPATION (PD) (µW)<br />

10 6<br />

10 5<br />

10 4<br />

10 3<br />

10 2<br />

10 1<br />

ASTABLE MODE<br />

SUPPLY VOLTAGE (VDD) = 10V<br />

C = 0.1µF<br />

C = 0.01µF<br />

C =1000pF<br />

FIGURE 27. TYPICAL POWER DISSIPATION vs OUTPUT<br />

FREQUENCY (VDD = 10V)<br />

1MΩ<br />

10 -1 10 0 10 1 10 2 10 3 10 4 10 5 10 6<br />

Q OR Q FREQUENCY (F) (Hz)<br />

C =100pF<br />

C =10pF

CD<strong>4047</strong>BMS<br />

Typical Performance Characteristics (Continued)<br />

POWER DISSIPATION (PD) (µW)<br />

10 5<br />

10 4<br />

10 3<br />

10 2<br />

ASTABLE MODE<br />

SUPPLY VOLTAGE (VDD) = 15V<br />

C = 0.1µF<br />

C =1000pF<br />

C = 0.01µF<br />

10 -1 10 0 10 1 10 2 10 3 10 4 10 5 10 6<br />

Q OR Q FREQUENCY (F) (Hz)<br />

FIGURE 28. TYPICAL POWER DISSIPATION vs OUTPUT FREQUENCY (VDD = 15V)<br />

A<strong>stable</strong> Mode Design Information<br />

Unit-to-Unit Transfer Voltage Variations<br />

The following analysis presents variations from unit to unit as<br />

a function of transfer voltage (VTR) shift (33%-67% VDD) for<br />

free running (a<strong>stable</strong>) operation.<br />

TERMINAL 13<br />

TERMINAL 10<br />

FIGURE 29. ASTABLE MODE WAVEFORMS<br />

t1 = -RC In<br />

t2 = -RC In<br />

VTR<br />

;<br />

VDD + VTR<br />

typically, t1 = 1.1RC<br />

VDD - VTR ;<br />

2VDD - VTR<br />

typically, t2 = 1.1RC<br />

tA = 2(t1 + t2)<br />

(VTR)(VDD - VTR)<br />

= -2RC In<br />

(VDD + VTR)(2VDD - VTR)<br />

Typ:<br />

Min:<br />

Max:<br />

VTR = 0.5VDD<br />

VTR = 0.33VDD<br />

VTR = 0.67VDD<br />

t1 t2 t1 t2<br />

t A /2 t A /2<br />

t A = 4.40RC<br />

t A = 4.62RC<br />

t A = 4.62RC<br />

thus if tA = 4.40RC is used, the variation will be +5%, -0%<br />

due to variations in transfer voltage.<br />

Variations Due to VDD and Temperature Changes<br />

In addition to variations from unit to unit, the a<strong>stable</strong> period<br />

varies with VDD and temperature, Typical variations are presented<br />

in graphical form in Figures 11 to 18 with 10V as reference<br />

for voltage variations curves and +25 o C as reference<br />

for temperature variations curves.<br />

t A<br />

7-909<br />

C =100pF<br />

C =10pF<br />

<strong>Mono</strong><strong>stable</strong> Mode Design Information<br />

The following analysis presents variations from unit to unit as a<br />

function of transfer voltage (VTR) shift (33% - 67% VDD) for<br />

one shot (mono<strong>stable</strong>) operation.<br />

TERMINAL 8<br />

TERMINAL 13<br />

TERMINAL 10<br />

FIGURE 30. MONOSTABLE WAVEFORMS<br />

t1´ = -RC In<br />

VTR<br />

;<br />

2VDD<br />

typically, t1´ = 1.38RC<br />

tM = (t1´ + t2)<br />

(VTR)(VDD - VTR)<br />

tM = -RC In<br />

(2VDD - VTR)(2VDD)<br />

where tM = <strong>Mono</strong><strong>stable</strong> mode pulse width.<br />

Values for tM are as follows:<br />

Typ:<br />

Min:<br />

Max:<br />

VTR = 0.5VDD<br />

VTR = 0.33VDD<br />

VTR = 0.67VDD<br />

t1´ t2 t1´ t2<br />

tM tM<br />

tM = 2.48RC<br />

tM = 2.71RC<br />

tM = 2.48RC<br />

thus if tM = 2.48RC<br />

is used, the variation will be +9.3%,<br />

-0% due to variations in transfer voltage.<br />

NOTES:<br />

1. In the a<strong>stable</strong> mode, the first positive half cycle has a duration of<br />

tM; succeeding durations are tA /s.<br />

2. In addition to variations from unit to unit, the mono<strong>stable</strong> pulse<br />

width varies with VDD and temperature. These variations are<br />

presented in graphical form in Figures 19 to 26 with 10V as reference<br />

for voltage variation curves and +25 o C as reference for<br />

temperature variation curves.

Retrigger Mode Operation<br />

The CD<strong>4047</strong>BMS can be used in the retrigger mode to extend<br />

the output pulse duration, or to compare the frequency of an<br />

input signal with that of the internal oscillator. In the retrigger<br />

mode the input pulse is applied to terminal 12, and the output is<br />

taken from terminal 10 or 11. As shown in Figure 31 normal<br />

mono<strong>stable</strong> action is obtained when one retrigger pulse is<br />

applied. Extended pulse duration is obtained when more than<br />

one pulse is applied.<br />

For two input pulses, tRE = t1´ + t1 + 2t2. For more than two<br />

pulses, the output pulse width is an integral number of time periods,<br />

with the first time period being t1´ + t2, typically, 2.48RC, and<br />

all subsequent time periods being t1 + t2, typically, 2.2RC.<br />

External Counter Option<br />

Time tM can be extended by any amount with the use of external<br />

counting circuitry. Advantages include digitally controlled pulse<br />

duration, small timing capacitors for long time periods, and<br />

extremely fast recovery time. A typical implementation is shown<br />

in Figure 32. The pulse duration at the output is<br />

text = (N - 1) (t A ) + (tM + t A /2)<br />

where text = pulse duration of the circuitry, and N is the number<br />

of counts used.<br />

AST<br />

CD<strong>4047</strong>BMS<br />

Q<br />

INPUT<br />

PULSE<br />

CL<br />

CD4017BMS<br />

R<br />

11<br />

FIGURE 32. IMPLEMENTATION OF EXTERNAL COUNTER OPTION<br />

Timing Component Limitations<br />

OUT<br />

The capacitor used in the circuit should be non polarized and<br />

have low leakage (i.e. the parallel resistance of the capacitor<br />

should be at least an order of magnitude greater than the external<br />

resistor used). There is no upper or lower limit for either R or<br />

C value to maintain oscillation.<br />

+TRIGGER &<br />

RETRIGGER<br />

TERMINALS<br />

8 & 12<br />

OSC OUTPUT<br />

TERMINAL 13<br />

Q OUTPUT<br />

TERMINAL 10<br />

t1´ t2<br />

tRE<br />

12<br />

OPTIONAL<br />

BUFFER<br />

TEXT<br />

t1´ t2 t1´ t2<br />

tRE<br />

CD<strong>4047</strong>BMS<br />

7-910<br />

However, in consideration of accuracy, C must be much larger<br />

than the inherent stray capacitance in the system (unless this<br />

capacitance can be measured and taken into account). R must<br />

be much larger than the CMOS “ON” resistance in series with<br />

it, which typically is hundreds of Ω. In addition, with very large<br />

values of R, some short term instability with respect to time may<br />

be noted.<br />

The recommended values for these components to maintain<br />

agreement with previously calculated formulas without trimming<br />

should be:<br />

C ≥ 100pF, up to any practical value, for a<strong>stable</strong> modes;<br />

C ≥ 1000pF, up to any practical value for mono<strong>stable</strong> modes.<br />

10kΩ≤ R ≤ 1MΩ<br />

Power Consumption<br />

In the standby mode (<strong>Mono</strong><strong>stable</strong> or A<strong>stable</strong>), power dissipation<br />

will be a function of leakage current in the circuit, as shown<br />

in the static electrical characteristics. For dynamic operation,<br />

the power needed to charge the external timing capacitor C is<br />

given by the following formula:<br />

A<strong>stable</strong> Mode:<br />

<strong>Mono</strong><strong>stable</strong> Mode:<br />

P = 2CV 2 f. (Output at terminal No. 13)<br />

P = 4CV 2 f. (Output at terminal Nos. 10 and 11)<br />

P = (2.9CV2 ) (Duty Cycle)<br />

T<br />

(Output at terminal Nos. 10 to 11)<br />

FIGURE 31. RETRIGGER MODE WAVEFORMS<br />

The circuit is designed so that most of the total power is consumed<br />

in the external components. In practice, the lower the<br />

values of frequency and voltage used, the closer the actual<br />

power dissipation will be to the calculated value.<br />

Because the power dissipation does not depend on R, a<br />

design for minimum power dissipation would be a small value<br />

of C. The value of R would depend on the desired period<br />

(within the limitations discussed above). See Figures 26, 27,<br />

and 28 for typical power consumption in a<strong>stable</strong> mode.<br />

t1´ t2 t1´ t2 t1´ t2 t1´ t2<br />

tRE<br />

t1´ t2 t1´ t2 t1´ t2<br />

tRE

Chip Dimensions and Pad Layout<br />

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.<br />

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without<br />

notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate<br />

and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which<br />

may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.<br />

For information regarding Intersil Corporation and its products, see web site http://www.intersil.com<br />

Sales Office Headquarters<br />

NORTH AMERICA<br />

Intersil Corporation<br />

P. O. Box 883, Mail Stop 53-204<br />

Melbourne, FL 32902<br />

TEL: (321) 724-7000<br />

FAX: (321) 724-7240<br />

CD<strong>4047</strong>BMS<br />

Dimensions in parenthesis are in millimeters and are<br />

derived from the basic inch dimensions as indicated.<br />

Grid graduations are in mils (10 -3 inch).<br />

METALLIZATION: Thickness: 11kÅ − 14kÅ, AL.<br />

PASSIVATION: 10.4kÅ - 15.6kÅ, Silane<br />

BOND PADS: 0.004 inches X 0.004 inches MIN<br />

DIE THICKNESS: 0.0198 inches - 0.0218 inches<br />

EUROPE<br />

Intersil SA<br />

Mercure Center<br />

100, Rue de la Fusee<br />

1130 Brussels, Belgium<br />

TEL: (32) 2.724.2111<br />

FAX: (32) 2.724.22.05<br />

911<br />

ASIA<br />

Intersil (Taiwan) Ltd.<br />

Taiwan Limited<br />

7F-6, No. 101 Fu Hsing North Road<br />

Taipei, Taiwan<br />

Republic of China<br />

TEL: (886) 2 2716 9310<br />

FAX: (886) 2 2715 3029