Note: Please refer to ASIX Multi-Port Ethernet Controller Application ...

Note: Please refer to ASIX Multi-Port Ethernet Controller Application ...

Note: Please refer to ASIX Multi-Port Ethernet Controller Application ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

8<br />

2<br />

1<br />

7<br />

6<br />

5<br />

4<br />

3<br />

2<br />

1<br />

D<br />

C<br />

B<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

FRAME#<br />

IRDY#<br />

P2 PCI_CLK<br />

P2 RESETN<br />

P2 PERR#<br />

P2 SERR#<br />

P2 PAR<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

P2<br />

IDSEL<br />

C/BE0#<br />

C/BE1#<br />

C/BE2#<br />

C/BE3#<br />

INT<br />

PME<br />

P0_RXIN<br />

P0_RXIP<br />

P0_TXON<br />

P0_TXOP<br />

P1_RXIN<br />

P1_RXIP<br />

P1_TXON<br />

P1_TXOP<br />

EECS<br />

EESK<br />

EEDIO<br />

VCC33<br />

AD0<br />

AD1<br />

AD2<br />

AD3<br />

AD4<br />

AD5<br />

AD6<br />

AD7<br />

AD8<br />

AD9<br />

AD10<br />

AD11<br />

AD12<br />

AD13<br />

AD14<br />

AD15<br />

AD16<br />

AD17<br />

AD18<br />

AD19<br />

AD20<br />

AD21<br />

AD22<br />

AD23<br />

AD24<br />

AD25<br />

AD26<br />

AD27<br />

AD28<br />

AD29<br />

AD30<br />

AD31<br />

GNT#<br />

REQ#<br />

P2 TRDY#<br />

P2 DEVSEL#<br />

P2 STOP#<br />

P4 MII0_TXD0<br />

P4 MII0_TXD1<br />

P4 MII0_TXD2<br />

P4 MII1_TXD0<br />

P4 MII1_TXD1<br />

P4 MII1_TXD2<br />

P4<br />

P4<br />

P4<br />

P4<br />

P4<br />

P4<br />

P4<br />

P4<br />

P5<br />

P5<br />

P5<br />

P5<br />

P5<br />

P4,5<br />

VCC5P<br />

3.3VAUX<br />

P5 VCC33-18<br />

P4,5 VCC33A<br />

P5 VCC18<br />

P5 VCC18A<br />

P2,4,5 GND<br />

AD0<br />

AD1<br />

AD2<br />

AD3<br />

AD4<br />

AD5<br />

AD6<br />

AD7<br />

AD8<br />

AD9<br />

AD10<br />

AD11<br />

AD12<br />

AD13<br />

AD14<br />

AD15<br />

AD16<br />

AD17<br />

AD18<br />

AD19<br />

AD20<br />

AD21<br />

AD22<br />

AD23<br />

AD24<br />

AD25<br />

AD26<br />

AD27<br />

AD28<br />

AD29<br />

AD30<br />

AD31<br />

FRAME#<br />

IRDY#<br />

PCI_CLK<br />

RESETN<br />

PERR#<br />

SERR#<br />

PAR<br />

IDSEL<br />

C/BE0#<br />

C/BE1#<br />

C/BE2#<br />

C/BE3#<br />

INT<br />

PME<br />

GNT#<br />

REQ#<br />

TRDY#<br />

DEVSEL#<br />

STOP#<br />

MII0_TXD0<br />

MII0_TXD1<br />

MII0_TXD2<br />

MII1_TXD0<br />

MII1_TXD1<br />

MII1_TXD2<br />

P0_RXIN<br />

P0_RXIP<br />

P0_TXON<br />

P0_TXOP<br />

P1_RXIN<br />

P1_RXIP<br />

P1_TXON<br />

P1_TXOP<br />

EECS<br />

EESK<br />

EEDIO<br />

VCC5P<br />

3.3VAUX<br />

VCC33<br />

VCC33-18<br />

VCC33A<br />

VCC18<br />

VCC18A<br />

GND<br />

VCC33<br />

GND<br />

GND<br />

MII0_RX_COL<br />

MII0_RXD2<br />

MII0_RXD0<br />

MII0_RX_CLK<br />

MII0_TX_EN<br />

MII0_TXD1<br />

MII0_TXD3<br />

MII0_MDIO<br />

GND<br />

25MHz +- 30ppm Crystal *<strong>Note</strong>3-1<br />

for <strong>Port</strong> 0/<strong>Port</strong> 1 <strong>Ethernet</strong> I/F<br />

P0_XTLP<br />

C6<br />

27pF<br />

50MHz Reference Clock Circuit<br />

for RMII/Reverse-RMII Modes<br />

Optional<br />

VCC18<br />

MII0 Interface Connec<strong>to</strong>r<br />

Optional<br />

J2<br />

MII1_TX_CLK<br />

P0_XTLN<br />

C7<br />

27pF<br />

6<br />

7<br />

8<br />

9<br />

10<br />

11<br />

14<br />

MII0_TXD3<br />

MII0_TXD2<br />

MII0_TXD1<br />

MII0_TXD0<br />

MII0_TX_EN<br />

MII0_TX_CLK<br />

MII0_RX_CLK<br />

MII0_RXD3<br />

MII0_RXD2<br />

MII0_RXD1<br />

MII0_RXD0<br />

MII0_RX_DV<br />

MII0_RX_CLK<br />

MII0_TX_CLK<br />

MII1_RX_CLK<br />

J2 HEADER Table MII0 Interface<br />

AX88742 J2<br />

Reverse<br />

PIN PIN MII Mode MII Mode RMII Mode<br />

123<br />

122<br />

121<br />

120<br />

113<br />

112<br />

70<br />

C32<br />

NC,0.1uF<br />

4<br />

1<br />

OSC1<br />

VDD<br />

E/D<br />

NC,50.000MHz<br />

R32<br />

Y1<br />

O/P 3<br />

GND 2<br />

1M<br />

25.000MHz<br />

R14<br />

*<strong>Note</strong>3-5/*<strong>Note</strong>3-6<br />

24<br />

22<br />

20<br />

18<br />

16<br />

14<br />

12<br />

10<br />

8<br />

6<br />

4<br />

2<br />

C33<br />

10uF<br />

R33 0,0805<br />

C31<br />

0.1uF<br />

R13<br />

NC,0<br />

*<strong>Note</strong>3-8<br />

NC,HEADER 12X2<br />

23 GND<br />

21 MII0_RX_CRS<br />

19 MII0_RXD3<br />

17 MII0_RXD1<br />

15 MII0_RX_DV<br />

13<br />

11 MII0_TX_CLK<br />

9 MII0_TXD0<br />

7 MII0_TXD2<br />

5 MII0_MDC<br />

3 GND<br />

1 GND<br />

J3<br />

NC,HEADER 2<br />

NC,0<br />

*<strong>Note</strong>3-3<br />

VCC33<br />

L1<br />

NC,PBY160808T-110Y-S<br />

VCC33-18<br />

L4<br />

NC,PBY160808T-110Y-S<br />

NC<br />

NC<br />

MII0_TXD1<br />

MII0_TXD0<br />

MII0_TX_EN<br />

MII0_REFCLKO<br />

MII0_REFCLK<br />

C29<br />

10uF<br />

*<strong>Note</strong>3-2<br />

3.3VAUX<br />

MII1_TXD3<br />

Reverse<br />

RMII Mode<br />

NC<br />

NC<br />

*<strong>Note</strong>3-9<br />

*<strong>Note</strong>3-4<br />

C30<br />

0.1uF<br />

MII0_RXD1<br />

MII0_RXD0<br />

MII0_CRSDV<br />

R40<br />

12.1 K 1%<br />

R39<br />

12.1 K 1%<br />

MII0_REFCLKO<br />

MII0_REFCLK<br />

R47<br />

4.7K<br />

R17<br />

4.7K<br />

R44 0,0805<br />

GND<br />

P0_TXON<br />

P0_TXOP<br />

P0_RXIN<br />

P0_RXIP<br />

P0_XTLN<br />

P0_XTLP<br />

P1_TXON<br />

P1_TXOP<br />

P1_RXIN<br />

P1_RXIP<br />

MII0_MDIO<br />

MII0_MDC<br />

MII0_RX_CLK<br />

MII0_RX_DV<br />

MII0_RXD0<br />

MII0_RXD1<br />

MII0_RXD2<br />

MII0_RXD3<br />

MII0_RX_CRS<br />

MII0_RX_COL<br />

MII0_TX_CLK<br />

MII0_TX_EN<br />

MII0_TXD0<br />

MII0_TXD1<br />

MII0_TXD2<br />

MII0_TXD3<br />

MII1_MDIO<br />

MII1_MDC<br />

MII1_RX_CLK<br />

MII1_RX_DV<br />

MII1_RXD0<br />

MII1_RXD1<br />

MII1_RXD2<br />

MII1_RXD3<br />

MII1_RX_CRS<br />

MII1_RX_COL<br />

MII1_TX_CLK<br />

MII1_TX_EN<br />

MII1_TXD0<br />

MII1_TXD1<br />

MII1_TXD2<br />

46<br />

47<br />

48<br />

49<br />

44<br />

43<br />

31<br />

VCC33<br />

VCC33<br />

VCC33<br />

VCC18<br />

VCC18<br />

VCC18<br />

VCC18<br />

VCC18-S<br />

VCC33-S<br />

VCC33A<br />

VCC33A<br />

VCC18A<br />

VCC18A<br />

VCC18A<br />

VCC18A<br />

7<br />

18<br />

1<br />

13<br />

14<br />

24<br />

25<br />

45<br />

72<br />

106<br />

128<br />

MII1 Interface Connec<strong>to</strong>r<br />

Optional<br />

2<br />

3<br />

5<br />

6<br />

9<br />

11<br />

12<br />

23<br />

22<br />

20<br />

19<br />

16<br />

107<br />

108<br />

70<br />

71<br />

91<br />

92<br />

96<br />

97<br />

100<br />

101<br />

112<br />

113<br />

120<br />

121<br />

122<br />

123<br />

29<br />

30<br />

31<br />

34<br />

35<br />

36<br />

37<br />

38<br />

32<br />

33<br />

43<br />

44<br />

49<br />

48<br />

47<br />

46<br />

42<br />

78<br />

105<br />

53<br />

65<br />

87<br />

118<br />

27<br />

26<br />

8<br />

17<br />

10<br />

15<br />

21<br />

4<br />

GND<br />

GND<br />

MII1_RX_COL<br />

MII1_RXD2<br />

MII1_RXD0<br />

MII1_RX_CLK<br />

MII1_TX_EN<br />

MII1_TXD1<br />

MII1_TXD3<br />

MII1_MDIO<br />

GND<br />

U4<br />

P0_TXON<br />

P0_TXOP<br />

P0_RXIN<br />

P0_RXIP<br />

P0_RSET_BG<br />

P0_XTLN<br />

P0_XTLP<br />

P1_TXON<br />

P1_TXOP<br />

P1_RXIN<br />

P1_RXIP<br />

P1_RSET_BG<br />

MII0_MDIO<br />

MII0_MDC<br />

MII0_RX_CLK<br />

MII0_RX_DV<br />

MII0_RXD0<br />

MII0_RXD1<br />

MII0_RXD2<br />

MII0_RXD3<br />

MII0_RX_CRS<br />

MII0_RX_COL<br />

MII0_TX_CLK<br />

MII0_TX_EN<br />

MII0_TXD0<br />

MII0_TXD1<br />

MII0_TXD2<br />

MII0_TXD3<br />

MII1_MDIO<br />

MII1_MDC<br />

MII1_RX_CLK<br />

MII1_RX_DV<br />

MII1_RXD0<br />

MII1_RXD1<br />

MII1_RXD2<br />

MII1_RXD3<br />

MII1_RX_CRS<br />

MII1_RX_COL<br />

MII1_TX_CLK<br />

MII1_TX_EN<br />

MII1_TXD0<br />

MII1_TXD1<br />

MII1_TXD2<br />

MII1_TXD3<br />

VCC3IO<br />

VCC3IO<br />

VCC3IO<br />

VCCK<br />

VCCK<br />

VCCK<br />

VCCK<br />

V18<br />

VCCAH<br />

P0_VCC33A<br />

P1_VCC33A<br />

P0_VCC18A<br />

P1_VCC18A<br />

P1_VCC18A<br />

P0_VCC18A<br />

P0_GND33A<br />

P1_GND33A<br />

P0_GND18A<br />

P0_GND18A<br />

P1_GND18A<br />

P1_GND18A<br />

GNDA<br />

GND<br />

GND<br />

GND<br />

GND<br />

E-PAD<br />

J1<br />

24<br />

22<br />

20<br />

18<br />

16<br />

14<br />

12<br />

10<br />

8<br />

6<br />

4<br />

2<br />

AX88742<br />

PCI I/F<br />

AX88742<br />

*<strong>Note</strong>3-8<br />

NC,HEADER 12X2<br />

23 GND<br />

21 MII1_RX_CRS<br />

19 MII1_RXD3<br />

17 MII1_RXD1<br />

15 MII1_RX_DV<br />

13<br />

11 MII1_TX_CLK<br />

9 MII1_TXD0<br />

7 MII1_TXD2<br />

5 MII1_MDC<br />

3 GND<br />

1 GND<br />

AD0<br />

AD1<br />

AD2<br />

AD3<br />

AD4<br />

AD5<br />

AD6<br />

AD7<br />

AD8<br />

AD9<br />

AD10<br />

AD11<br />

AD12<br />

AD13<br />

AD14<br />

AD15<br />

AD16<br />

AD17<br />

AD18<br />

AD19<br />

AD20<br />

AD21<br />

AD22<br />

AD23<br />

AD24<br />

AD25<br />

AD26<br />

AD27<br />

AD28<br />

AD29<br />

AD30<br />

AD31<br />

6<br />

7<br />

8<br />

9<br />

10<br />

11<br />

14<br />

MII1_TXD3<br />

MII1_TXD2<br />

MII1_TXD1<br />

MII1_TXD0<br />

MII1_TX_EN<br />

MII1_TX_CLK<br />

MII1_RX_CLK<br />

MII1_RXD3<br />

MII1_RXD2<br />

MII1_RXD1<br />

MII1_RXD0<br />

MII1_RX_DV<br />

MII1_RX_CLK<br />

MII1_TX_CLK<br />

RST_N 28<br />

MODE2<br />

MODE1<br />

MODE0<br />

NC<br />

NC<br />

AD0<br />

AD1<br />

AD2<br />

AD3<br />

AD4<br />

AD5<br />

AD6<br />

AD7<br />

AD8<br />

AD9<br />

AD10<br />

AD11<br />

AD12<br />

AD13<br />

AD14<br />

AD15<br />

AD16<br />

AD17<br />

AD18<br />

AD19<br />

AD20<br />

AD21<br />

AD22<br />

AD23<br />

AD24<br />

AD25<br />

AD26<br />

AD27<br />

AD28<br />

AD29<br />

AD30<br />

AD31<br />

FRAME#<br />

IRDY#<br />

PCI_CLK<br />

RESETN<br />

PERR#<br />

SERR#<br />

PAR<br />

IDSEL<br />

C/BE0#<br />

C/BE1#<br />

C/BE2#<br />

C/BE3#<br />

INT<br />

ISOLATE<br />

PME<br />

GNT#<br />

REQ#<br />

TRDY#<br />

DEVSEL#<br />

STOP#<br />

EECS<br />

EESK<br />

EEDIO<br />

MODE2<br />

MODE1<br />

MODE0<br />

J1 HEADER Table MII1 Interface<br />

AX88742 J1<br />

Reverse<br />

PIN PIN MII Mode MII Mode RMII Mode<br />

GNT<br />

119<br />

117<br />

116<br />

115<br />

114<br />

104<br />

103<br />

102<br />

90<br />

89<br />

88<br />

86<br />

85<br />

81<br />

80<br />

79<br />

77<br />

76<br />

75<br />

74<br />

73<br />

69<br />

68<br />

67<br />

63<br />

62<br />

58<br />

57<br />

56<br />

52<br />

51<br />

50<br />

FRAME 83<br />

IRDY 84<br />

PCI_CLK 124<br />

PERR 98<br />

SERR 99<br />

PAR 109<br />

IDSEL<br />

CBE0<br />

CBE1<br />

CBE2<br />

CBE3<br />

INT<br />

66<br />

111<br />

110<br />

82<br />

64<br />

61<br />

ISOLATE 60<br />

PME 59<br />

55<br />

REQ 54<br />

TRDY 93<br />

DEVSEL<br />

94<br />

STOP 95<br />

CS 127<br />

SK 125<br />

DIO 126<br />

41<br />

40<br />

39<br />

MII1_TXD1<br />

MII1_TXD0<br />

MII1_TX_EN<br />

MII1_REFCLKO<br />

MII1_REFCLK<br />

R38<br />

4.7K<br />

VCC5P<br />

VCC33<br />

*<strong>Note</strong>3-7<br />

Reverse<br />

RMII Mode<br />

NC<br />

NC<br />

R43<br />

6.8K<br />

R42<br />

15K<br />

MII1_RXD1<br />

MII1_RXD0<br />

MII1_CRSDV<br />

R41<br />

4.7K<br />

R37<br />

4.7K<br />

MII1_REFCLKO<br />

MII1_REFCLK<br />

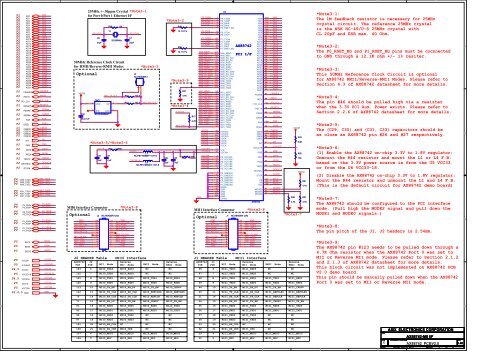

*<strong>Note</strong>3-1:<br />

The 1M feedback resis<strong>to</strong>r is necessary for 25MHz<br />

crystal circuit. The <strong>refer</strong>ence 25MHz crystal<br />

is the NSK HC-49/U-S 25MHz crystal with<br />

CL 20pF and ESR max. 40 Ohm.<br />

*<strong>Note</strong>3-2:<br />

The P0_RSET_BG and P1_RSET_BG pins must be cocnnected<br />

<strong>to</strong> GND through a 12.1K ohm +/- 1% resiter.<br />

*<strong>Note</strong>3-3:<br />

This 50MHz Reference Clock Circuit is optional<br />

for AX88742 RMII/Reverse-RMII Modes. <strong>Please</strong> <strong>refer</strong> <strong>to</strong><br />

Section 4.3 of AX88742 datasheet for more details.<br />

*<strong>Note</strong>3-4:<br />

The pin #46 should be pulled high via a resister<br />

when the 3.3V PCI Aux. Power exists. <strong>Please</strong> <strong>refer</strong> <strong>to</strong><br />

Section 2.2.6 of AX88742 datasheet for more details.<br />

*<strong>Note</strong>3-5:<br />

The (C29, C30) and (C31, C33) capaci<strong>to</strong>rs should be<br />

as close as AX88742 pin #26 and #27 respectively.<br />

*<strong>Note</strong>3-6:<br />

(1) Enable the AX88742 on-chip 3.3V <strong>to</strong> 1.8V regula<strong>to</strong>r:<br />

Unmount the R44 resis<strong>to</strong>r and mount the L1 or L4 F.B.<br />

based on the 3.3V power source is from the U5 VCC33<br />

or from the U6 VCC33-18.<br />

(2) Disable the AX88742 on-chip 3.3V <strong>to</strong> 1.8V regula<strong>to</strong>r:<br />

Mount the R44 resis<strong>to</strong>r and unmount the L1 and L4 F.B.<br />

(This is the default circuit for AX88742 demo board)<br />

*<strong>Note</strong>3-7:<br />

The AX88742 should be configured <strong>to</strong> the PCI interface<br />

mode. (Pull high the MODE2 signal and pull down the<br />

MODE1 and MODE0 signals.)<br />

*<strong>Note</strong>3-8:<br />

The pin pitch of the J1, J2 headers is 2.54mm.<br />

*<strong>Note</strong>3-9:<br />

The AX88742 pin #123 needs <strong>to</strong> be pulled down through a<br />

4.7K Ohm resis<strong>to</strong>r when the AX88742 <strong>Port</strong> 0 was set <strong>to</strong><br />

MII or Reverse MII mode. <strong>Please</strong> <strong>refer</strong> <strong>to</strong> Section 2.1.2<br />

and 2.1.3 of AX88742 datasheet for more details.<br />

This block circuit was not implemented on AX88742 PCB<br />

V2.0 demo board.<br />

This pin should be manually pulled down when the AX88742<br />

<strong>Port</strong> 0 was set <strong>to</strong> MII or Reverse MII mode.<br />

D<br />

C<br />

B<br />

71<br />

15 MII0_RX_DV MII0_TX_EN<br />

MII0_CRSDV<br />

MII0_TX_EN<br />

34<br />

15 MII1_RX_DV MII1_TX_EN<br />

MII1_CRSDV<br />

MII1_TX_EN<br />

A<br />

91<br />

16 MII0_RXD0 MII0_TXD0<br />

MII0_RXD0<br />

MII0_TXD0<br />

35<br />

16 MII1_RXD0 MII1_TXD0<br />

MII1_RXD0<br />

MII1_TXD0<br />

A<br />

92<br />

17 MII0_RXD1 MII0_TXD1<br />

MII0_RXD1<br />

MII0_TXD1<br />

36<br />

17 MII1_RXD1 MII1_TXD1<br />

MII1_RXD1<br />

MII1_TXD1<br />

96<br />

18 MII0_RXD2 MII0_TXD2 NC<br />

NC<br />

37<br />

18 MII1_RXD2 MII1_TXD2 NC<br />

NC<br />

97<br />

19 MII0_RXD3 MII0_TXD3 NC<br />

NC<br />

38<br />

19 MII1_RXD3 MII1_TXD3 NC<br />

NC<br />

101<br />

20<br />

MII0_RX_COL<br />

NC<br />

NC<br />

NC<br />

33<br />

20<br />

MII1_RX_COL<br />

NC<br />

NC<br />

NC<br />

8<br />

100<br />

107<br />

108<br />

4<br />

5<br />

7<br />

21<br />

MII0_RX_CRS<br />

MII0_CRS<br />

MII0_MDIO MII0_MDIO MII0_MDIO MII0_MDIO<br />

MII0_MDC MII0_MDC MII0_MDC MII0_MDC<br />

NC<br />

6<br />

NC<br />

32<br />

29<br />

30<br />

5<br />

21<br />

4<br />

5<br />

MII1_RX_CRS<br />

MII1_CRS<br />

MII1_MDIO MII1_MDIO MII1_MDIO MII1_MDIO<br />

MII1_MDC MII1_MDC MII1_MDC MII1_MDC<br />

4<br />

NC<br />

NC<br />

3<br />

2<br />

Title<br />

<strong>ASIX</strong> ELECTRONICS CORPORATION<br />

AX88742-MII I/F<br />

Size Document Number Rev<br />

C<br />

1.40<br />

AX88742_PCBV2.0<br />

Sunday, April 04, 2010<br />

Date: Sheet of<br />

3 6<br />

1

![P-CAD EDA - [Sheet1]](https://img.yumpu.com/49470492/1/190x115/p-cad-eda-sheet1.jpg?quality=85)