Digital Current Control of a Voltage Source Converter With Active ...

Digital Current Control of a Voltage Source Converter With Active ...

Digital Current Control of a Voltage Source Converter With Active ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

1364 IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 21, NO. 5, SEPTEMBER 2006<br />

<strong>Digital</strong> <strong>Current</strong> <strong>Control</strong> <strong>of</strong> a <strong>Voltage</strong> <strong>Source</strong> <strong>Converter</strong><br />

<strong>With</strong> <strong>Active</strong> Damping <strong>of</strong> LCL Resonance<br />

Eric Wu, Member, IEEE, and Peter W. Lehn, Senior Member, IEEE<br />

Abstract—Inductance–capacitor–inductance (LCL)-filters installed<br />

at converter outputs <strong>of</strong>fer higher harmonic attenuation<br />

than L-filters, but careful design is required to damp LCL resonance,<br />

which can cause poorly damped oscillations and even<br />

instability. A new topology is presented for a discrete-time current<br />

controller which damps this resonance, combining deadbeat<br />

current control with optimal state-feedback pole assignment. By<br />

separating the state feedback gains into deadbeat and damping<br />

feedback loops, transient overcurrent protection is realizable while<br />

preserving the desired pole locations. Moreover, the controller is<br />

shown to be robust to parameter uncertainty in the grid inductance.<br />

Experimental tests verify that fast well-damped transient<br />

response and overcurrent protection is possible at low switching<br />

frequencies relative to the resonant frequency.<br />

Index Terms—Electromagnetic interference (EMI), inductance–capacitor–inductance<br />

(LCL)-filter, voltage source converters<br />

(VSCs).<br />

I. INTRODUCTION<br />

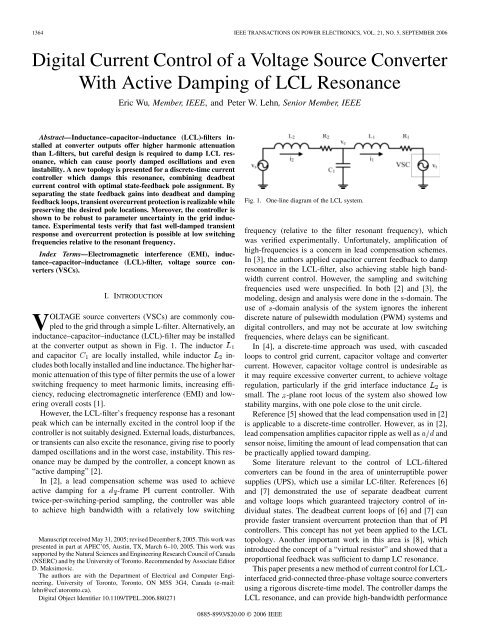

VOLTAGE source converters (VSCs) are commonly coupled<br />

to the grid through a simple L-filter. Alternatively, an<br />

inductance–capacitor–inductance (LCL)-filter may be installed<br />

at the converter output as shown in Fig. 1. The inductor<br />

and capacitor are locally installed, while inductor includes<br />

both locally installed and line inductance. The higher harmonic<br />

attenuation <strong>of</strong> this type <strong>of</strong> filter permits the use <strong>of</strong> a lower<br />

switching frequency to meet harmonic limits, increasing efficiency,<br />

reducing electromagnetic interference (EMI) and lowering<br />

overall costs [1].<br />

However, the LCL-filter’s frequency response has a resonant<br />

peak which can be internally excited in the control loop if the<br />

controller is not suitably designed. External loads, disturbances,<br />

or transients can also excite the resonance, giving rise to poorly<br />

damped oscillations and in the worst case, instability. This resonance<br />

may be damped by the controller, a concept known as<br />

“active damping” [2].<br />

In [2], a lead compensation scheme was used to achieve<br />

active damping for a -frame PI current controller. <strong>With</strong><br />

twice-per-switching-period sampling, the controller was able<br />

to achieve high bandwidth with a relatively low switching<br />

Manuscript received May 31, 2005; revised December 8, 2005. This work was<br />

presented in part at APEC’05, Austin, TX, March 6–10, 2005. This work was<br />

supported by the Natural Sciences and Engineering Research Council <strong>of</strong> Canada<br />

(NSERC) and by the University <strong>of</strong> Toronto. Recommended by Associate Editor<br />

D. Maksimovic.<br />

The authors are with the Department <strong>of</strong> Electrical and Computer Engineering,<br />

University <strong>of</strong> Toronto, Toronto, ON M5S 3G4, Canada (e-mail:<br />

lehn@ecf.utoronto.ca).<br />

<strong>Digital</strong> Object Identifier 10.1109/TPEL.2006.880271<br />

Fig. 1. One-line diagram <strong>of</strong> the LCL system.<br />

frequency (relative to the filter resonant frequency), which<br />

was verified experimentally. Unfortunately, amplification <strong>of</strong><br />

high-frequencies is a concern in lead compensation schemes.<br />

In [3], the authors applied capacitor current feedback to damp<br />

resonance in the LCL-filter, also achieving stable high bandwidth<br />

current control. However, the sampling and switching<br />

frequencies used were unspecified. In both [2] and [3], the<br />

modeling, design and analysis were done in the s-domain. The<br />

use <strong>of</strong> -domain analysis <strong>of</strong> the system ignores the inherent<br />

discrete nature <strong>of</strong> pulsewidth modulation (PWM) systems and<br />

digital controllers, and may not be accurate at low switching<br />

frequencies, where delays can be significant.<br />

In [4], a discrete-time approach was used, with cascaded<br />

loops to control grid current, capacitor voltage and converter<br />

current. However, capacitor voltage control is undesirable as<br />

it may require excessive converter current, to achieve voltage<br />

regulation, particularly if the grid interface inductance is<br />

small. The -plane root locus <strong>of</strong> the system also showed low<br />

stability margins, with one pole close to the unit circle.<br />

Reference [5] showed that the lead compensation used in [2]<br />

is applicable to a discrete-time controller. However, as in [2],<br />

lead compensation amplifies capacitor ripple as well as and<br />

sensor noise, limiting the amount <strong>of</strong> lead compensation that can<br />

be practically applied toward damping.<br />

Some literature relevant to the control <strong>of</strong> LCL-filtered<br />

converters can be found in the area <strong>of</strong> uninterruptible power<br />

supplies (UPS), which use a similar LC-filter. References [6]<br />

and [7] demonstrated the use <strong>of</strong> separate deadbeat current<br />

and voltage loops which guaranteed trajectory control <strong>of</strong> individual<br />

states. The deadbeat current loops <strong>of</strong> [6] and [7] can<br />

provide faster transient overcurrent protection than that <strong>of</strong> PI<br />

controllers. This concept has not yet been applied to the LCL<br />

topology. Another important work in this area is [8], which<br />

introduced the concept <strong>of</strong> a “virtual resistor” and showed that a<br />

proportional feedback was sufficient to damp LC resonance.<br />

This paper presents a new method <strong>of</strong> current control for LCLinterfaced<br />

grid-connected three-phase voltage source converters<br />

using a rigorous discrete-time model. The controller damps the<br />

LCL resonance, and can provide high-bandwidth performance<br />

0885-8993/$20.00 © 2006 IEEE

WU AND LEHN: DIGITAL CURRENT CONTROL OF A VOLTAGE SOURCE CONVERTER 1365<br />

at relatively low switching frequencies. This new system allows<br />

for the flexible, systematic design approach <strong>of</strong> pole assignment<br />

while retaining control <strong>of</strong> the current trajectory, providing transient<br />

overcurrent protection even when the controller’s overall<br />

performance criteria cannot be met [9].<br />

II. SYSTEM MODELING<br />

Assuming that the impedances <strong>of</strong> the three-phase system <strong>of</strong><br />

Fig. 1 are balanced, the differential equations governing the<br />

three-phase voltage and current vectors are<br />

The three-phase vectors , , , , and<br />

in (1)–(3) can be replaced by complex space vectors , ,<br />

, , and in the form by applying<br />

the amplitude-invariant Clarke transformation<br />

(1)<br />

(2)<br />

(3)<br />

(4)<br />

Fig. 2. SPWM with twice-per-period sampling.<br />

The PWM pattern generator generates independent gating<br />

waveforms for each leg <strong>of</strong> the three-phase converter as shown<br />

in Fig. 2.<br />

<strong>With</strong> a symmetrical carrier, the desired average terminal<br />

voltage can be reached over half <strong>of</strong> a switching period ,<br />

during which the voltage command is held and compared to the<br />

triangular carrier to calculate the duty cycle. Hence sampling<br />

occurs twice per switching period at frequency 1 .In<br />

order to accurately model the behavior <strong>of</strong> the PWM pattern generator<br />

and the digital controller, the differential equations are<br />

discretized by the zero-order hold method. The discrete-time<br />

state-space model is given by [10]<br />

and assuming no zero-sequence currents.<br />

The space-vectors may then be projected onto complex variables<br />

in the synchronously rotating -frame<br />

by performing the substitution<br />

on each<br />

space vector, with synchronous frequency . Assuming<br />

0, the complex -frame differential equations are then<br />

given by<br />

where<br />

(9)<br />

(5)<br />

(6)<br />

(7)<br />

The subscripts will henceforth be dropped for convenience.<br />

Equations (5)–(7) can be now written in state-space form as<br />

(8)<br />

where<br />

Due to finite computation time, the voltage command calculated<br />

during the present timestep must be requested by the controller<br />

during the next timestep. This behavior is modeled as a<br />

one-timestep delay between the converter voltage command<br />

and the terminal voltage<br />

(10)<br />

Considering as a state and as a new input, this delay may<br />

be incorporated into the model by rearranging the state equation<br />

[11]. The augmented state model is then given by<br />

(11)<br />

(12)<br />

where

1366 IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 21, NO. 5, SEPTEMBER 2006<br />

Fig. 3.<br />

Proposed complex current controller.<br />

Fig. 4. Equivalent control diagram.<br />

This complex-valued discrete-time state model will be used in<br />

the control design and analysis which follows.<br />

III. CONTROL DESIGN<br />

The control design and analysis have been performed using<br />

the complex state model, eliminating the redundancy between<br />

d and axes and the need to explicitly decouple them. The<br />

proposed control structure is shown in Fig. 3. At its core is a<br />

deadbeat current controller, which provides transient overcurrent<br />

protection. The deadbeat current reference is the difference<br />

<strong>of</strong> the output <strong>of</strong> the integrator , which ensures zero<br />

steady-state error, and feedback current which incrementally<br />

modifies the reference to provide damping without controlling<br />

the capacitor voltage.<br />

A. Deadbeat <strong>Current</strong> <strong>Control</strong>ler<br />

The deadbeat current controller is designed such that<br />

reaches its reference in a fixed, finite number <strong>of</strong> timesteps,<br />

without overshoot. Since the current trajectory is controlled,<br />

transient overcurrent protection can be guaranteed by placing a<br />

limiter on the deadbeat current reference as shown in Fig. 3. To<br />

determine the deadbeat gains , and , the state equation<br />

<strong>of</strong> (11) is rewritten symbolically<br />

If the sampling rate is fast enough such that the system voltage<br />

does not change rapidly over a single timestep, then it can<br />

be assumed that . Substituting and<br />

solving for gives the required converter command voltage<br />

where<br />

(16)<br />

(17)<br />

(18)<br />

(19)<br />

B. Damping and Integral Gain Calculation<br />

Damping <strong>of</strong> capacitor oscillations is achieved by state feedback<br />

through the gain , while zero steady-state error is guaranteed<br />

by the integral with gain . Calculation <strong>of</strong> these gains<br />

can be simplified by using the single-loop feedback control diagram<br />

in Fig. 4. Provided the current limiter does not engage, it<br />

can be shown that this diagram has the same closed-loop state<br />

response as Fig. 3 provided that<br />

(13)<br />

Due to the previously-mentioned one-timestep computation<br />

delay, the current can be made to reach its reference in a minimum<br />

<strong>of</strong> two timesteps. A control law can therefore be found<br />

which ensures that . The state equation for is<br />

(14)<br />

Incrementing by one timestep and substituting for , ,<br />

, and from (13) yields<br />

(20)<br />

(21)<br />

It should be noted that control diagram <strong>of</strong> Fig. 4 is only equivalent<br />

to that <strong>of</strong> Fig. 3 when the current limiter is not engaged.<br />

If excessive current is requested, the converter has no current<br />

capacity to damp capacitor oscillations and the incremental<br />

damping gain, is effectively disabled.<br />

To determine and , the open-loop state model <strong>of</strong> (11)<br />

must first be augmented with the integrator state equation [10]<br />

(22)<br />

The final, augmented state model is<br />

(15)<br />

(23)

WU AND LEHN: DIGITAL CURRENT CONTROL OF A VOLTAGE SOURCE CONVERTER 1367<br />

where<br />

Simple pole assignment may be used to determine the input<br />

Fig. 5. Separation <strong>of</strong> a complex system into d- and q-axis components.<br />

(24)<br />

so that the closed-loop system has the desired state response.<br />

The actual gains and may then be found using (20) and<br />

(21), respectively.<br />

C. Optimal Pole Assignment<br />

In this study, linear quadratic (LQ) optimal control [10] is<br />

used to determine the gains and , since optimal control<br />

frees the designer from the mathematical abstraction <strong>of</strong> pole<br />

assignment. Furthermore, LQ controllers <strong>of</strong>fer good stability<br />

margins and robustness. Analyses <strong>of</strong> stability margins for discrete-time<br />

LQ regulators are given in [12] and [13].<br />

The LQ regulator is designed by solving the algebraic Riccati<br />

equation to determine a gain which minimizes the quadratic<br />

cost function<br />

(25)<br />

and determine the quadratic cost weightings on the state<br />

values and inputs, respectively. The th diagonal element <strong>of</strong><br />

determines the direct weighting on the th state, while <strong>of</strong>f-diagonal<br />

elements have more complicated effects and are set to zero<br />

in this study.<br />

Some empirical guidelines for their selection can be given.<br />

• Heavy weighting should be placed on to ensure fast,<br />

well-damped transient current response.<br />

• The impedance <strong>of</strong> the capacitor is fairly high and little current<br />

is shunted through ; thus and will behave similarly,<br />

and an equal cost should also be placed on .<br />

• should be allowed to move as dictated by the grid in<br />

order to avoid converter saturation. Low or zero weighting<br />

may be placed on this state.<br />

• Weighting on should initially be close to or at zero.<br />

While an increase in this weighting will limit the amount<br />

<strong>of</strong> control effort used, it will also decrease damping and<br />

stability. For the same reason, input weighting should<br />

initially be set to one.<br />

• A fairly high weighting should be placed on the integrator<br />

state , in order to attain high bandwidth. However, this<br />

increase comes at the expense <strong>of</strong> stability.<br />

The transient response <strong>of</strong> the converter terminal voltage<br />

should be verified during a 1 per-unit step in , to ensure that<br />

it lies within the available converter terminal voltage, including<br />

the voltage required to reject the bus voltage . may be<br />

limited by increasing either the weighting on or the input<br />

weighting .<br />

D. Separation <strong>of</strong> and Axes<br />

To implement and simulate the system, the controller and<br />

model must be decomposed into real-valued d and -axis systems.<br />

The result <strong>of</strong> a multiplication between vector and<br />

matrix can be separated into and components using the<br />

matrix equation<br />

(26)<br />

This process is shown graphically in Fig. 5. Equation (26) can<br />

be applied to every gain in Fig. 3 to find real-valued, coupled<br />

- and -axis controllers, and to the matrices <strong>of</strong> the closed-loop<br />

state model for simulation and numerical analysis.<br />

IV. SIMULATION RESULTS<br />

To verify the controller’s performance, an LCL-filter was designed<br />

following the guidelines presented in [14]. The sampling<br />

and switching frequencies were 8 kHz and 4 kHz, respectively,<br />

and the filter parameters were 1.0 mH 0.04 p.u.),<br />

0.5 mH 0.02 p.u. , 14 F 20 p.u. ,<br />

with a resonant frequency <strong>of</strong> 2.3 kHz. The 60 Hz, 1.4 kVA test<br />

system had a rated voltage <strong>of</strong> 115 V (line–line rms).<br />

Following the guidelines <strong>of</strong> Section III-C, the following LQ<br />

weightings were chosen:<br />

The per-unitization <strong>of</strong> and with base voltage 115 V<br />

and current 7 A can be done by writing and in terms<br />

<strong>of</strong> their per-unit values and<br />

(27)<br />

(28)

1368 IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 21, NO. 5, SEPTEMBER 2006<br />

where<br />

Substituting (27) and (28) into (25), rearranging the result in the<br />

form<br />

(29)<br />

and solving for the per-unitized weightings<br />

yielded the following equations:<br />

and<br />

Fig. 6. Internal d-axis signals during 10-A step in I .<br />

(30)<br />

(31)<br />

The inverse relationships can be used to determine corresponding<br />

LQ weightings for any system <strong>of</strong> base values.<br />

The deadbeat current gains , , and were calculated<br />

using (17)–(19). The LQR weightings and were used to<br />

numerically calculate and . Finally, (20) and (21) were<br />

used to find and , respectively, completing the control<br />

design. The resulting gains are given by<br />

(32)<br />

(33)<br />

(34)<br />

(35)<br />

(36)<br />

Simulation is carried out using the closed-loop equivalent<br />

system, given by<br />

(37)<br />

which is valid provided the current limiter is not activated. For<br />

simulation, (38) was decomposed into a real-valued system with<br />

separate - and -axis signals using (26).<br />

Fig. 6 shows simulated -axis controller signals during a 10-A<br />

step in .<br />

The incremental damping current , which contains a<br />

decaying oscillation at the resonant frequency <strong>of</strong> the LC tank<br />

Fig. 7. Bode plots <strong>of</strong> i =I and i =I .<br />

formed by and , is subtracted from the undamped integral<br />

current reference to create a new reference for the<br />

deadbeat current controller. is made to track this deadbeat<br />

reference with a two-timestep delay.<br />

The closed-loop frequency response <strong>of</strong> the system is shown in<br />

the first column <strong>of</strong> Fig. 7. For this system, the theoretical bandwidth<br />

(at which response is 3 dB) is 646 Hz. The cross-coupling<br />

response, shown in the second column, is well-attenuated<br />

with a peak <strong>of</strong> 23 dB. It can also be seen from this figure that<br />

in the steady state, there is no cross-coupling response, hence<br />

cross-coupling has been implicitly eliminated by the complex<br />

-frame controller.<br />

V. ROBUSTNESS ANALYSIS<br />

The nominal eigenvalues <strong>of</strong> the overall closed-loop system<br />

(marked in bold on the -plane diagram <strong>of</strong> Fig. 8) show that

WU AND LEHN: DIGITAL CURRENT CONTROL OF A VOLTAGE SOURCE CONVERTER 1369<br />

Fig. 8. Locus <strong>of</strong> overall closed-loop eigenvalues where L<br />

markers) to 39.9 mH.<br />

= 0.18 to 0.5 (large<br />

Fig. 9. Nominal pole locations <strong>of</strong> the deadbeat current controller.<br />

the entire system is well-damped. Since a complex-valued statespace<br />

model was used, the pole locations are assymetrical about<br />

the real axis, with each root actually representing a conjugate<br />

pair.<br />

The robustness <strong>of</strong> the controller to parameter error was analyzed<br />

by varying from the nominal design value <strong>of</strong> 0.5 mH,<br />

since the value <strong>of</strong> is highly variable due to its association<br />

with the grid inductance. is particularly subject to underestimation<br />

since the local inductance should be known to the designer.<br />

The percentage parameter error is defined as<br />

error actual value<br />

nominal value<br />

(38)<br />

A. Overall System Robustness<br />

The robustness <strong>of</strong> the overall closed-loop system is<br />

demonstrated in the closed-loop root-locus <strong>of</strong> Fig. 8, in<br />

which is varied from 0.18 mH (error 64%) to 39.9 mH<br />

(error 7880%). For large values <strong>of</strong> , the largest eigenvalues<br />

approach the unit circle asymptotically. From these<br />

results, it is clear that the system is quite robust to both underand<br />

over-estimation <strong>of</strong> .<br />

B. Deadbeat <strong>Current</strong> <strong>Control</strong>ler Robustness<br />

When overcurrent limiting occurs, the incremental damping<br />

current has no effect; hence under ideal conditions, the<br />

outer LC tank formed by and is undamped and only the<br />

deadbeat current controller is in operation, with the closed-loop<br />

poles shown in Fig. 9.<br />

However, the second-order effect <strong>of</strong> a parameter error in<br />

can shift the undamped poles from the unit circle, possibly<br />

leading to an unstable deadbeat current controller in the event<br />

<strong>of</strong> overcurrent limiting. Fig. 10 shows the root-locus <strong>of</strong> the<br />

deadbeat current controller in the upper-right quadrant as the<br />

underestimation error <strong>of</strong> is increased from 0% to 100%,<br />

Fig. 10. Root locus <strong>of</strong> the deadbeat controller with 0100 %errorL 0%<br />

at f =f = f4; 4:7; 6g. Large X’s show nominal pole locations.<br />

for where is the filter’s resonant frequency.<br />

For 4, the pole becomes unstable for small<br />

errors in . However, for , the damping<br />

increases as the underestimation increases. Thus there exists a<br />

frequency ratio beyond which any underestimation <strong>of</strong> will<br />

lead to greater damping.<br />

It has been empirically found that if 5.8, then the<br />

deadbeat controller will be guaranteed to have poles with radii<br />

1 for any underestimation <strong>of</strong> , guaranteeing stable operation<br />

during overcurrent limiting. Fig. 11 shows the maximum radii<br />

<strong>of</strong> the deadbeat current controller poles for errors in between<br />

0 and 400%, where nominal values <strong>of</strong> and vary between<br />

0.252 mH and 12.6 mH. Filter capacitance was fixed at 14 F<br />

and the switching frequency was selected to yield 5.8.<br />

It can be seen that the maximum radius is unity for all combinations<br />

<strong>of</strong> inductances, showing that any underestimation <strong>of</strong><br />

will cause the outermost poles to either remain along the

1370 IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 21, NO. 5, SEPTEMBER 2006<br />

, damping and inte-<br />

Fig. 13. d- and q-axis currents during a 10-A step in i<br />

grator loops disabled.<br />

Fig. 11. Maximum eigenvalue radii <strong>of</strong> the deadbeat controller for 0400% <br />

%errorL 0%, C = 14 F, f =f = 5.8.<br />

Fig. 12. Implemented control structure.<br />

Fig. 14. Oscilloscope phase A signals during a 10-A step in i , damping and<br />

integrator loops disabled. Time: 5 ms/div. Top to bottom: i (20 A/div), i<br />

(20 A/div), v (100 V/div), v (100 V/div).<br />

unit circle or move towards the origin. Moreover, the addition<br />

<strong>of</strong> conduction losses will also increase system damping, thus the<br />

frequency ratio <strong>of</strong> 5.8 is a conservative requirement.<br />

VI. EXPERIMENTAL RESULTS<br />

The controller was implemented on a Texas Instruments<br />

TMS320C40 DSP as shown in Fig. 12.<br />

All measurements are first converted to the -frame, then<br />

projected onto the -frame synchronized to the 115-V bus<br />

voltage . The synchronization signal is obtained<br />

by lowpass filtering and phase-advancing the result by<br />

to compensate for filter, sensor and data-acquisition delays.<br />

Based on the user reference , the -frame controller<br />

then calculates the voltage command vector , which is<br />

converted back to a three-phase vector and sent to an Altera<br />

Flex 8000 FPGA, which generates and sends the corresponding<br />

PWM gating signals to the converter. <strong>Converter</strong> switching is<br />

performed by a 50-A, 1200-V six-pack IGBT module. The<br />

converter dc link capacitance is 4800 F, and is connected to<br />

a 50-kW, 220-V dc generator.<br />

A. Step Response<br />

Fig. 13 shows and during a 10-A step in , employing<br />

only the inner deadbeat current loop. The response is<br />

nearly deadbeat, with only a small amount <strong>of</strong> cross-coupling due<br />

to unmodeled source inductance. As shown in the oscilloscope<br />

traces <strong>of</strong> Fig. 14, severe ringing is observed in and since<br />

the LC tank consisting <strong>of</strong> capacitor and inductor is not<br />

damped. In addition, there is a 4-kHz harmonic modulated by<br />

a sixth harmonic appearing in the -frame currents, which can<br />

be attributed to: 1) bandwidth limitations <strong>of</strong> the current sensors<br />

and data acquisition, 2) asymmetries resulting from the on-state<br />

voltage drop <strong>of</strong> the switches, and 3) asymmetries in the deadtime<br />

insertion algorithm. This distortion does not significantly<br />

affect the output.<br />

Fig. 15 shows the controller’s step response with the damping<br />

and integrator loops enabled. The rise time is approximately<br />

1.5 ms, there is no cross-coupling, and as expected, the actual<br />

currents and follow their respective deadbeat references<br />

and within approximately two timesteps. The step response<br />

characteristics closely resemble the simulated results <strong>of</strong><br />

Fig. 6, validating the model. The oscilloscope image <strong>of</strong> Fig. 16

WU AND LEHN: DIGITAL CURRENT CONTROL OF A VOLTAGE SOURCE CONVERTER 1371<br />

Fig. 15. d- and q-axis currents during a 10-A step in I , damping and integrator<br />

loops enabled.<br />

Fig. 17. d- and q-axis currents, and three-phase bus voltages during three-phase<br />

fault.<br />

Fig. 16. Oscilloscope phase A signals during a 10-A step in I , damping and<br />

integrator loops enabled. Time: 5 ms/div. Top to bottom: i (20 A/div), v<br />

(100 V/div), i (20 A/div), v (100 V/div).<br />

Fig. 18. Oscilloscope screen capture <strong>of</strong> phase A signals during three-phase<br />

fault. Time: 5 ms/div. Top to bottom: i (10 A/div), v (100 V/div), i<br />

(10 A/div), v (100 V/div).<br />

shows that the step response is fast, the system is well-damped,<br />

and there is no ringing.<br />

B. Disturbance Rejection<br />

In order to demonstrate the ability <strong>of</strong> the controller to reject<br />

disturbances and its ability to damp the resonance from excitation<br />

by external sources, a balanced three-phase fault was introduced<br />

which instantaneously reduced the magnitude <strong>of</strong><br />

by approximately 2/3 for 15 ms before being cleared. The response<br />

<strong>of</strong> the system to this fault is shown in Figs. 17 and 18.<br />

There is a brief transient in due to the speed <strong>of</strong> the fault exceeding<br />

the controller bandwidth, and because <strong>of</strong> the approximation<br />

in the calculation <strong>of</strong> the feedforward gain.<br />

Otherwise, the system is well-damped despite the high speed<br />

and severity <strong>of</strong> the fault, as shown in the oscilloscope screen capture<br />

<strong>of</strong> Fig. 18. Despite imbalances caused by different clearing<br />

times for each phase, the controller maintains good regulation,<br />

demonstrating its ability to operate in an unbalanced system.<br />

C. Overcurrent Protection<br />

The current controller regulated the current during the fault<br />

so effectively that overcurrent limits were rarely reached. As<br />

a result, this controller could not be used to test the overcurrent<br />

protection. However, use <strong>of</strong> a less aggressive controller or<br />

a larger filter capacitor will make overcurrent limiting imperative.<br />

Fig. 19 shows the sampled and calculated - and -axis currents<br />

for a less aggressive damping controller during the fault,<br />

with the current limits set to 30 A in each axis. It can be seen<br />

that this controller allows high current levels to occur for a significant<br />

period <strong>of</strong> time. Despite the change in overall gain, the<br />

deadbeat controller maintained the same performance, tracking<br />

its reference with a fixed delay. Fig. 20 shows the corresponding<br />

phase A currents and voltages.<br />

The overcurrent limit was then set to 10 A in each axis and the<br />

balanced, three-phase fault was reintroduced to demonstrate the<br />

transient overcurrent protection capabilities <strong>of</strong> the controller. As<br />

shown in Fig. 21 the -axis current reaches the new overcurrent<br />

limit immediately after the fault but is clipped to 10 A. Ringing<br />

can be seen in the oscilloscope traces <strong>of</strong> and <strong>of</strong> Fig. 22<br />

following the fault. This occurs when the current is clipped because<br />

the sum <strong>of</strong> the damping and integral feedback is saturated,<br />

thus only the deadbeat controller is in operation with the current<br />

limit as its reference. <strong>With</strong> the damping feedback disabled<br />

by saturation, the fault excites ringing in the LC tank formed

1372 IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 21, NO. 5, SEPTEMBER 2006<br />

Fig. 19. d- and q-axis signals and three-phase bus voltages during three-phase<br />

fault with less aggressive control gains, 30-A current limit.<br />

Fig. 21. d- and q-axis signals and three-phase bus voltages during three-phase<br />

fault with less aggressive control gains, 10-A current limit.<br />

Fig. 20. Oscilloscope phase A signals during three-phase fault with less aggressive<br />

control gains, 30-A current limit. Time: 5 ms/div. Top to bottom: i<br />

(20 A/div), v (100 V/div), i , (20 A/div), v (100 V/div).<br />

Fig. 22. Oscilloscope phase A signals during three-phase fault with less aggressive<br />

control gains, 10-A current limit. Time: 5 ms/div. Top to bottom: i<br />

(20 A/div), v (100 V/div), i (20 A/div), v (100 V/div).<br />

by and , which will resonate just as if no converter were<br />

present. On the other hand, the converter is protected and can<br />

ride through the fault without tripping.<br />

D. Frequency Response<br />

The measured frequency response <strong>of</strong> the controller is shown<br />

in Fig. 23. The actual bandwidth (the 3 dB frequency) <strong>of</strong> the<br />

controller was approximately 430 Hz. This value is 67% <strong>of</strong><br />

the theoretical bandwidth. The decrease is mainly attributed to<br />

the frequency-dependent parameters <strong>of</strong> the ac inductors. Parameter<br />

errors may also have contributed to detuning <strong>of</strong> the controller.<br />

In addition to the faster high-frequency roll-<strong>of</strong>f, there<br />

was also an unexpected low frequency <strong>of</strong>fset <strong>of</strong> approximately<br />

0.5 dB. The cause may simply be due to aliasing <strong>of</strong> the harmonically<br />

rich output current, but this discrepancy does not invalidate<br />

these results.<br />

VII. CONCLUSION<br />

In this study, a rigorous discrete-time model <strong>of</strong> an LCL-filtered<br />

converter including calculation delay was derived in the<br />

-frame. By using a complex state-space, control design was<br />

Fig. 23. Magnitude frequency response <strong>of</strong> the test system controller, compared<br />

to theoretical values.<br />

simplified. The complex model was used to design a controller<br />

which implicitly eliminated -axes cross-coupling, and for the

WU AND LEHN: DIGITAL CURRENT CONTROL OF A VOLTAGE SOURCE CONVERTER 1373<br />

first time combined the flexibility <strong>of</strong> pole assignment with inherent<br />

transient overcurrent protection. -plane analysis <strong>of</strong> a test<br />

system with characteristic parameters showed that the controller<br />

was robustly stable to variations in the grid interface inductance.<br />

Both simulation and experimental results showed that even at<br />

a low switching frequency relative to the resonant frequency,<br />

the proposed control structure can achieve well-damped, highbandwidth<br />

current control, and that cross-coupling can be minimized.<br />

Furthermore, the controller has good disturbance rejection,<br />

and regardless <strong>of</strong> overall performance provides instantaneous<br />

overcurrent protection even during severe transient disturbances.<br />

REFERENCES<br />

[1] M. Lindgren and J. Svensson, “Connecting fast switching voltagesource<br />

converters to the grid-harmonic distortion and its reduction,”<br />

in Proc. IEEE/Stockholm Power Tech Conf., Stockholm, Sweden, Jun.<br />

1995, pp. 191–196.<br />

[2] V. Blasko and V. Kaura, “A novel control to actively damp resonance in<br />

input LC filter <strong>of</strong> a three-phase voltage source converter,” IEEE Trans.<br />

Ind. Appl., vol. 33, no. 2, pp. 542–550, Mar./Apr. 1997.<br />

[3] E. Twining and D. Holmes, “Grid current regulation <strong>of</strong> a three-phase<br />

voltage source inverter with an LCL input filter,” IEEE Transactions<br />

Power Electron., vol. 18, no. 3, pp. 888–895, May 2003.<br />

[4] M. Lindgren and J. Svensson, “<strong>Control</strong> <strong>of</strong> a voltage-source converter<br />

connected to the grid through an LCL-filter-application to active filtering,”<br />

in Proc. Power Electron. Spec. Conf., Fukuoka, Japan, May<br />

1998, vol. 1, pp. 229–235.<br />

[5] M. Liserre, A. Dell’Aquila, and F. Blaabjerg, “Stability improvements<br />

<strong>of</strong> an LCL-filter based three-phase active rectifier,” in Proc.<br />

Power Electron. Spec. Conf., Cairns, Australia, Jun. 2002, vol. 3, pp.<br />

1195–1201.<br />

[6] T. Kawabata, T. Miyashita, and Y. Yamamoto, “<strong>Digital</strong> control <strong>of</strong> three<br />

phase PWM inverter with L-C filter,” in Proc. Power Electron. Spec.<br />

Conf., Kyoto, Japan, Apr. 1988, vol. 2, pp. 634–643.<br />

[7] S. Buso, S. Fasolo, and P. Mattavelli, “Uninterruptible power supply<br />

multiloop control employing digital predictive voltage and current regulators,”<br />

IEEE Trans. Ind. Appl., vol. 37, no. 6, pp. 1846–1854, Nov./<br />

Dec. 2001.<br />

[8] P. Dahono, Y. Bahar, Y. Sato, and T. Kataoka, “Damping <strong>of</strong> transient<br />

oscillations on the output LC filter <strong>of</strong> PWM inverters by using a virtual<br />

resistor,” in Proc. 4th IEEE Int. Conf. Power Electron. Drive Syst., Oct.<br />

2001, vol. 1, pp. 403–407.<br />

[9] E. Wu and P. Lehn, “<strong>Digital</strong> current control <strong>of</strong> a voltage source<br />

converter with active damping <strong>of</strong> LCL resonance,” in Proc. 20th Appl.<br />

Power Electron. Conf. Expo (APEC), Austin, TX, Mar. 2005, pp.<br />

1642–1649.<br />

[10] G. F. Franklin, M. L. Workman, and D. J. Powell, <strong>Digital</strong> <strong>Control</strong> <strong>of</strong><br />

Dynamic Systems, 2nd ed. Reading, MA: Addison-Wesley, 1990.<br />

[11] O. Kukrer and H. Komurcugil, “Deadbeat control method for singlephase<br />

UPS inverters with compensation <strong>of</strong> computation delay,” Proc.<br />

Inst. Elect. Eng., pp. 123–128, Jan. 1999.<br />

[12] A. T. Neto, J. Dion, and L. Dugard, “On the robustness <strong>of</strong> LQ regulators<br />

for discrete time systems,” in Proc. 30th IEEE Conf. Decision Contr.,<br />

Brighton, UK, Dec. 1991, vol. 3, pp. 2960–2965.<br />

[13] U. Shaked, “Guaranteed stability margins for the discrete-time linear<br />

quadratic optimal regulator,” IEEE Trans. Autom. Contr., vol. AC-31,<br />

no. 2, pp. 162–165, Feb. 1986.<br />

[14] M. Liserre, F. Blaabjerg, and S. Hansen, “Design and control <strong>of</strong> an<br />

LCL-filter based three-phase active rectifier,” in Proc. 36th IAS Annu.<br />

Meeting, Chicago, IL, Oct. 2001, vol. 1, pp. 299–307.<br />

Eric Wu (S’03–M’05) was born in Taipei, Taiwan, R.O.C., in 1978. He received<br />

the B.A.Sc. and M.A.Sc. degrees in electrical engineering from the University<br />

<strong>of</strong> Toronto, Toronto, ON, Canada, in 2002 and 2005, respectively.<br />

Peter W. Lehn (SM’05) received the B.Sc. and M.Sc. degrees in electrical enginnering<br />

from the University <strong>of</strong> Manitoba, Winnipeg, MB, Canada, in 1990<br />

and 1992, respectively, and the Ph.D. degree from the University <strong>of</strong> Toronto,<br />

Toronto, ON, Canada, in 1999.<br />

From 1992 to 1994, he was with the Network Planning Group, Siemens AG,<br />

Erlangen, Germany. Presently, he is an Associate Pr<strong>of</strong>essor at the University <strong>of</strong><br />

Toronto.