Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

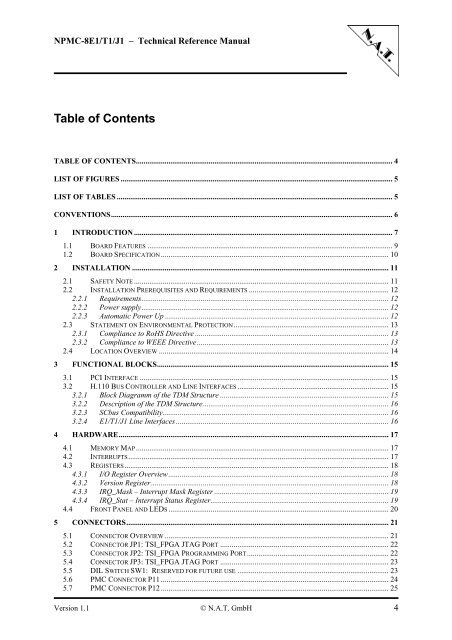

<strong>NPMC</strong>-<strong>8E1</strong>/<strong>T1</strong>/<strong>J1</strong> – Technical Reference Manual<br />

Table of Contents<br />

TABLE OF CONTENTS...................................................................................................................................... 4<br />

LIST OF FIGURES .............................................................................................................................................. 5<br />

LIST OF TABLES ................................................................................................................................................ 5<br />

CONVENTIONS................................................................................................................................................... 6<br />

1 INTRODUCTION ....................................................................................................................................... 7<br />

1.1 BOARD FEATURES ................................................................................................................................9<br />

1.2 BOARD SPECIFICATION....................................................................................................................... 10<br />

2 INSTALLATION ...................................................................................................................................... 11<br />

2.1 SAFETY NOTE ..................................................................................................................................... 11<br />

2.2 INSTALLATION PREREQUISITES AND REQUIREMENTS ......................................................................... 12<br />

2.2.1 Requirements................................................................................................................................. 12<br />

2.2.2 Power supply................................................................................................................................. 12<br />

2.2.3 Automatic Power Up ..................................................................................................................... 12<br />

2.3 STATEMENT ON ENVIRONMENTAL PROTECTION................................................................................. 13<br />

2.3.1 Compliance to RoHS Directive ..................................................................................................... 13<br />

2.3.2 Compliance to WEEE Directive.................................................................................................... 13<br />

2.4 LOCATION OVERVIEW ........................................................................................................................ 14<br />

3 FUNCTIONAL BLOCKS......................................................................................................................... 15<br />

3.1 PCI INTERFACE .................................................................................................................................. 15<br />

3.2 H.110 BUS CONTROLLER AND LINE INTERFACES ............................................................................... 15<br />

3.2.1 Block Diagramm of the TDM Structure ........................................................................................ 15<br />

3.2.2 Description of the TDM Structure................................................................................................. 16<br />

3.2.3 SCbus Compatibility...................................................................................................................... 16<br />

3.2.4 E1/<strong>T1</strong>/<strong>J1</strong> Line Interfaces ............................................................................................................... 16<br />

4 HARDWARE............................................................................................................................................. 17<br />

4.1 MEMORY MAP.................................................................................................................................... 17<br />

4.2 INTERRUPTS........................................................................................................................................ 17<br />

4.3 REGISTERS.......................................................................................................................................... 18<br />

4.3.1 I/O Register Overview................................................................................................................... 18<br />

4.3.2 Version Register............................................................................................................................ 18<br />

4.3.3 IRQ_Mask – Interrupt Mask Register ........................................................................................... 19<br />

4.3.4 IRQ_Stat – Interrupt Status Register............................................................................................. 19<br />

4.4 FRONT PANEL AND LEDS ................................................................................................................... 20<br />

5 CONNECTORS......................................................................................................................................... 21<br />

5.1 CONNECTOR OVERVIEW ..................................................................................................................... 21<br />

5.2 CONNECTOR JP1: TSI_FPGA JTAG PORT ........................................................................................ 22<br />

5.3 CONNECTOR JP2: TSI_FPGA PROGRAMMING PORT.......................................................................... 22<br />

5.4 CONNECTOR JP3: TSI_FPGA JTAG PORT ........................................................................................ 23<br />

5.5 DIL SWITCH SW1: RESERVED FOR FUTURE USE ............................................................................... 23<br />

5.6 PMC CONNECTOR P11 ....................................................................................................................... 24<br />

5.7 PMC CONNECTOR P12 ....................................................................................................................... 25<br />

Version 1.1 © N.A.T. GmbH 4