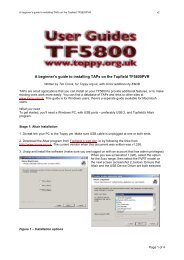

Download - Toppy.org.uk

Download - Toppy.org.uk

Download - Toppy.org.uk

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Chipsets<br />

Algorithmics Ltd.<br />

BONITO<br />

MIPS System<br />

Controller Cores<br />

and Chips<br />

Algorithmics Ltd.<br />

Salient Features<br />

<br />

Decent clock rates: the ASIC is very<br />

conservatively targeted at 83 MHz, but we<br />

expect to see higher frequencies<br />

<br />

<br />

<br />

Reliable BGA packages: we know production<br />

engineers hate big QFPs, and we thought that insystem<br />

price/performance would get worse if we<br />

were short of pins<br />

Unique debug mode/port: there is a mode that<br />

makes all cycles visible to a probe board<br />

connected to the SDRAM interface, so that<br />

developers can easily watch addresses and data<br />

without loading the board with a special<br />

connector<br />

Core logic is synthesizable Verilog: the same<br />

source code is used to produce both a Xilinx<br />

FPGA implementation (using “Synplicity”) and<br />

an ASIC (using Synopsys tools). Core logic<br />

users also get a test-bench using realistic models<br />

of connected devices. It’s all Algorithmicswritten<br />

or freely redistributable code.<br />

<br />

Supports variant MIPS CPUs: not all MIPS<br />

CPUs sharing the SysAD bus are the same, but<br />

BONITO supports all known 32-bit variants<br />

<br />

Programmer and development support: basic<br />

source code and a full bug list are freely<br />

available on line<br />

<br />

<br />

<br />

<br />

Configurable SDRAM port: runs synchronous to<br />

the CPU. Glueless for small systems, supporting<br />

64-bit DIMMs. Accepts external isolating<br />

switches and/or registers/drivers for larger<br />

configurations.<br />

PCI 2.1, 33 MHz, 32 bits: basic PCI as is widely<br />

used throughout the industry. Suitable for “host”<br />

or “peripheral” applications. The PCI clock need<br />

not be related to the CPU clock.<br />

I/O buffer cache: provides efficient PCI master<br />

access to local memory (usually the key I/O<br />

performance characteristic)<br />

High integration: glueless support for MIPS<br />

CPU reset (including the infamous<br />

“configuration bitstream”), for example<br />

algorithmics<br />

CPUs Supported<br />

All NEC VR Series processors<br />

Product Overview<br />

BONITO is a MIPS system controller that connects one of<br />

many different MIPS CPUs to a local SDRAM memory<br />

system, a PCI expansion bus, and a simple local I/O bus for<br />

ROM and 8-bit peripherals. BONITO is available now as<br />

reusable Verilog code configurable between 64-bit and 32-bit<br />

bus width at the CPU/SDRAM port. An ASIC for 32-bit<br />

systems is available now.<br />

Why BONITO?<br />

There are already several MIPS system controllers out there.<br />

BONITO is a cost-effective solution that will get you to<br />

market faster with a higher quality product.<br />

• Algorithmics’ MIPS system design experience goes back<br />

more than ten years<br />

• Appropriate detailing: we included, for example, a PCI<br />

arbiter and interrupt controller; we omitted, for example, a<br />

UART, or fast/wide PCI. Why? see below.<br />

26