EBD_intro_slides.pdf - Microelectronic Systems Laboratory - EPFL

EBD_intro_slides.pdf - Microelectronic Systems Laboratory - EPFL

EBD_intro_slides.pdf - Microelectronic Systems Laboratory - EPFL

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

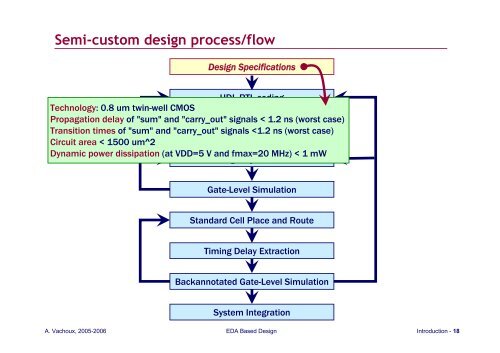

Semi-custom design process/flowDesign SpecificationsHDL RTL codingTechnology: 0.8 um twin-well CMOSPropagation delay of "sum" and "carry_out" signals < 1.2 ns (worst case)Transition times of "sum" and "carry_out" signals RTL simulation