EBD_intro_slides.pdf - Microelectronic Systems Laboratory - EPFL

EBD_intro_slides.pdf - Microelectronic Systems Laboratory - EPFL

EBD_intro_slides.pdf - Microelectronic Systems Laboratory - EPFL

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

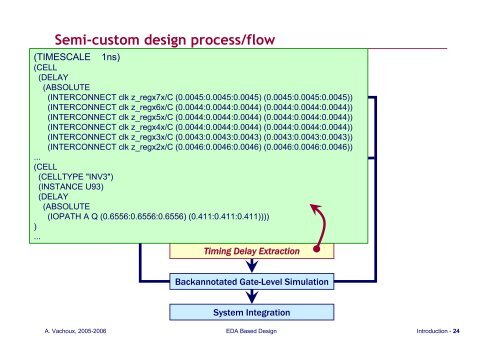

Semi-custom design process/flow(TIMESCALE 1ns)(CELL(DELAY(ABSOLUTEDesign SpecificationsHDL RTL coding(INTERCONNECT clk z_regx7x/C (0.0045:0.0045:0.0045) (0.0045:0.0045:0.0045))(INTERCONNECT clk z_regx6x/C (0.0044:0.0044:0.0044) (0.0044:0.0044:0.0044))(INTERCONNECT clk z_regx5x/C (0.0044:0.0044:0.0044) (0.0044:0.0044:0.0044))(INTERCONNECT clk z_regx4x/C (0.0044:0.0044:0.0044) (0.0044:0.0044:0.0044))RTL simulation(INTERCONNECT clk z_regx3x/C (0.0043:0.0043:0.0043) (0.0043:0.0043:0.0043))(INTERCONNECT clk z_regx2x/C (0.0046:0.0046:0.0046) (0.0046:0.0046:0.0046))...(CELL(CELLTYPE "INV3")(INSTANCE U93)(DELAY(ABSOLUTE(IOPATH A Q (0.6556:0.6556:0.6556) (0.411:0.411:0.411)))))...Logic SynthesisGate-Level SimulationStandard Cell Place and RouteTiming Delay ExtractionBackannotated Gate-Level SimulationSystem IntegrationA. Vachoux, 2005-2006 EDA Based Design Introduction - 24