You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

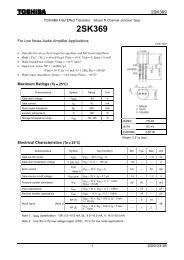

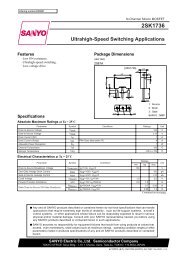

SPECIFICATIONSAll specifications at +25°C, +V CC = +V DD = +5V, fs = 44.1kHz, and 16-bit input data, SYSCLK = 384fs, unless otherwise noted. Measurement bandwidth is 20kHz.<strong>PCM1717</strong>EPARAMETER CONDITIONS MIN TYP MAX UNITSRESOLUTION 16 18 BitsDIGITAL INPUT/OUTPUTLogic FamilyCMOSInput Logic Level:V (2) IH 70% of V DD VV (2) IL 30% of V DD VV (3) IH 70% of V DD VV (3) IL 30% of V DD VV (4) IH 64% of V DD VV (4) IL 28% of V DD VInput Logic Current:I (5) IH –6.0 µAI (5) IL –120 µAI (6) IH –2 µAI (6) IL 0.02 µAI (4) IH V IN = 3.2V 40 µAI (4) IL V IN = 1.4V –40 µAOutput Logic Level: (+V DD = +5V)V (7) OH I OH = –5mA 3.8 VV (7) OL I OL = +5mA 1.0 VV (8) OL I OL = +5mA 1.0 VInterface FormatSelectable Normal, I 2 SData Format16/18 Bits MSB First Binary Two’s ComplementSampling Frequency 32 44.1 48 kHzSystem Clock Frequency 256fs/384fs 8.192/12.288 11.2896/16.9344 12.288/18.432 MHzDC ACCURACYGain Error ±1.0 ±5.0 % of FSRGain Mismatch Channel-to-Channel ±1.0 ±5.0 % of FSRBipolar Zero Error V O = 1/2 V CC at Bipolar Zero ±30 mVDYNAMIC PERFORMANCE (1)V CC = +5V, f = 991HzTHD+N at FS (0dB) –90 –80 dBTHD+N at –60dB –34 dBDynamic Range EIAJ, A-weighted 90 96 dBSignal-To-Noise Ratio EIAJ, A-weighted 92 100 dBChannel Separation 90 97 dBLevel Linearity Error (–90dB) ±0.5 dBDYNAMIC PERFORMANCE (1)V CC = +3V, f = 991HzTHD+N at FS (0dB) –86 dBDynamic Range EIAJ, A-weighted 91 dBSignal-To-Noise Ratio EIAJ, A-weighted 94 dBDIGITAL FILTER PERFORMANCEPass Band Ripple ±0.17 dBStop Band Attenuation –35 dBPass Band 0.445 fsStop Band 0.555 fsDe-emphasis Error (fs = 32kHz ~ 48kHz) –0.2 +0.55 dBDelay Time (Latency) 11.125/fs secANALOG OUTPUTVoltage Range FS (0dB) OUT 62% of V CC Vp-pLoad Impedance 5 kΩCenter Voltage 50% of V CC VPOWER SUPPLY REQUIREMENTSVoltage Range: +V CC +2.7 +5.5 VDC+V DD +2.7 +5.5 VDCSupply Current: +I CC +I (9) DD +V CC = +V DD = +5V 18.0 25.0 mA+V CC = +V DD = +3V 9.0 15.0 mA<strong>Power</strong> Dissipation +V CC = +V DD = +5V 90 125 mW+V CC = +V DD = +3V 27 45 mWTEMPERATURE RANGEOperation –25 +85 °CStorage –55 +100 °CNOTES: (1) Tested with Shibasoku #725 THD. Meter 400Hz HPF, 30kHz LPF On, Average Mode with 20kHz bandwidth limiting. (2) Pins 4, 5, 6, 14: LRCIN, DIN,BCKIN, FORMAT. (3) Pins 15, 16, 17, 18: RSTB, DM0, DM1, MUTE (Schmitt trigger input). (4) Pin 1: XTI. (5) Pins 15, 16, 17, 18: RSTB, DM0, DM1, MUTE (ifpull-up resistor is used). (6) Pins 4, 5, 6: LRCIN, DIN, BCKIN (if pull-up resistor is not used). (7) Pin 19: CLKO. (8) Pin 7: ZERO. (9) No load on pins 19 (CLKO)and 20 (XTO).®<strong>PCM1717</strong>2

TYPICAL PERFORMANCE CURVESAt T A = +25°C, +V CC = +V DD = +5V, fs = 44.1kHz, and 16-bit input data, SYSCLK = 384fs, unless otherwise noted.DYNAMIC PERFORMANCE–84THD+N vs V CC , V DDf IN = 1kHz, 384f S–30100DYNAMIC RANGE vs INPUT DATAf IN= 1kHzTHD+N at FS (dB)–86–88–90–92–60dB0dB–34–38THD+N at –60dB (dB)Dynamic Range (dB)98969492256f S384f S–943.0 3.5 4.0 4.5 5.0 5.5V CC , V DD (V)9016-BitInput Data18-Bit–84THD+N vs TEMPERATUREf IN= 1kHz, 384f S–30–84THD+N vs INPUT DATAf IN= 1kHz, FS (0dB)THD+N at FS (dB)–86–88–90–92–60dB–34–38THD+N at –60dB (dB)THD+N (dB)–86–88–90–92384f S0dB256f S–90–25 0 25 50 75 85 100Temperature (°C)–9416-BitInput Data18-Bit100DYNAMIC RANGE AND SNR vs V CC , V DDf IN = 1kHz, 384f S98SNR(dB)9694DynamicRange92903.0 3.5 4.0 4.5 5.0 5.5V CC , V DD®<strong>PCM1717</strong>4

TYPICAL PERFORMANCE CURVESAt T A = +25°C, +V CC = +V DD = +5V, fs = 44.1kHz, and 16-bit input data, SYSCLK = 384fs, unless otherwise noted.DIGITAL FILTER0OVERALL FREQUENCY CHARACTERISTIC0PASSBAND RIPPLE CHARACTERISTIC–20–0.2dB–40–60dB–0.4–0.6–80–0.8–1000 0.4536f S1.3605f S2.2675f S3.1745f S4.0815f SFrequency (Hz)–10 0.1134f S 0.2268f S 0.3402f S 0.4535f SFrequency (Hz)Level (dB)Level (dB)Level (dB)DE-EMPHASIS FREQUENCY RESPONSE (32kHz)0–2–4–6–8–10–120 5k 10k 15k 20k 25kFrequency (Hz)0–2–4–6–8–10–12DE-EMPHASIS FREQUENCY RESPONSE (44.1kHz)0 5k 10k 15k 20k 25kFrequency (Hz)DE-EMPHASIS FREQUENCY RESPONSE (48kHz)0–2–4–6–8–10–120 5k 10k 15k 20k 25kFrequency (Hz)Error (dB)Error (dB)Error (dB)DE-EMPHASIS ERROR (32kHz)0.60.40.20–0.2–0.4–0.60 3628 7256 10884 14512Frequency (Hz)DE-EMPHASIS ERROR (44.1kHz)0.60.40.20–0.2–0.4–0.60 4999.8375 9999.675 14999.5125 19999.35Frequency (Hz)DE-EMPHASIS ERROR (48kHz)0.60.40.20–0.2–0.4–0.60 5442 10884 16326 21768Frequency (Hz)5 <strong>PCM1717</strong>®

SYSTEM CLOCKThe system clock for <strong>PCM1717</strong> must be either 256f S or384f S , where f S is the audio sampling frequency (typically32kHz, 44.1kHz, or 48kHz). The system clock is used tooperate the digital filter and the modulator.The system clock can be either a crystal oscillator placedbetween XTI (pin 1) and XTO (pin 20), or an external clockinput to XTI. If an external system clock is used, XTO isopen (floating). Figure 1 illustrates the typical system clockconnections.<strong>PCM1717</strong> has a system clock detection circuit which automaticallysenses if the system clock is operating at 256f S or384f S . The system clock should be synchronized with LRCIN(pin 4) clock. LRCIN (left-right clock) operates at thesampling frequency fs. In the event these clocks are notsynchronized, <strong>PCM1717</strong> can compensate for the phase differenceinternally. If the phase difference between left-rightand system clocks is greater than 6 bit clocks (BCKIN), thesynchronization is performed internally. While the synchronizationis processing, the analog output is forced to a DClevel at bipolar zero. The synchronization typically occurs inless than 1 cycle of LRCIN.DATA INTERFACE FORMATSDigital audio data is interfaced to <strong>PCM1717</strong> on pins 4, 5,and 6—LRCIN (left-right clock), DIN (data input) andBCKIN (bit clock). <strong>PCM1717</strong> can accept both normal andI 2 S data formats. Normal data format is MSB first, two’scomplement, right-justified. I 2 S data is compatible withPhilips serial data protocol. In the I 2 S format, the data is 16-or 18-bit, selectable <strong>by</strong> bit 0 on Register 3 (Software ControlMode). In the Hardware Mode, <strong>PCM1717</strong> can only functionwith 16-bit normal data. Figures 5 through 9 illustrate timingand input formats.CLKOCLKOInternal System ClockInternal System ClockC 1X’talXTIExternal ClockXTIC 2XTOXTOC 1 , C 2 = 10 to 20pF<strong>PCM1717</strong>ECRYSTAL RESONATOR CONNECTION<strong>PCM1717</strong>EEXTERNAL CLOCK INPUTXTO pin = No ConnectionFIGURE 1. Internal Clock Circuit Diagram and Oscillator Connection.t XTIHt XTIL1/256f S or 1/384f S64% OF V DD28% OF V DDExternal System Clock High t XTIH 10ns (min)External System Clock Low t XTIL 10ns (min)FIGURE 2. External Clock Timing Requirements.®<strong>PCM1717</strong>6

Reset<strong>PCM1717</strong> has both internal power on reset circuit and theRSTB-pin (pin 15) which accepts external forced reset <strong>by</strong>RSTB = LOW. For internal power on reset, initialize (reset)is done automatically at power on V DD >2.2V (typ). Duringinternal reset = LOW, the output of the DAC is invalid andthe analog outputs are forced to V CC /2. Figure 3 illustratesthe timing of internal power on reset.For the RSTB-pin, PSTB-pin accepts external forced reset <strong>by</strong>RSTB = L. During RSTB = L, the output of the DAC isinvalid and the analog outputs are forced to V CC /2 afterinternal initialize (1024 system clocks count after RSTB = H.)Figure 4 illustrates the timing of RSTB-pin reset.V CC /V DD2.6V2.2V1.8VInternal ResetXTI ClockReset1024 system (= XTI) clocksReset RemovalFIGURE 3. Internal <strong>Power</strong>-On Reset Timing.RSTB-pinInternal Resett RST(1)50% of V DDResetReset Removal1024 system (XTI) clocksXTI ClockNOTE: (1) t RST = 20ns minFIGURE 4. RSTB-Pin Reset Timing.7 <strong>PCM1717</strong>®

OPERATIONAL CONTROL<strong>PCM1717</strong> can be controlled in two modes. Software Modeallows the user to control operation with a 16-bit serialregister. Hardware Mode allows the user to hard-wire operationof <strong>PCM1717</strong> using four parallel wires. The MODE pindetermines which mode <strong>PCM1717</strong> is in; a LOW level on pin14 places <strong>PCM1717</strong> in Hardware Mode, and a HIGH on pin14 places <strong>PCM1717</strong> in Software Mode.DIGITAL DE-EMPHASIS (Pins 16 and 17)Pins 16 and 17 are used as a two-bit parallel register tocontrol de-emphasis modes:PIN 16 PIN 17 MODE0 0 De-emphasis disabled1 0 De-emphasis enabled at 48kHz0 1 De-emphasis enabled at 44.1kHz1 1 De-emphasis enabled at 32kHzMODE (Pin 14) Selected Mode Pin 16 Pin 17 Pin 18“HIGH” Software Mode MD MC ML“LOW” Hardware Mode DM0 DM1 MUTETable I indicates which functions are selectable within theuser’s chosen mode. All of the functions shown are selectablein the Software Mode, but only soft mute and deemphasiscontrol may be selected in the Hardware Mode.SOFTWAREHARDWAREMODE DEFAULT MODE DEFAULTFUNCTION SELECTABLE SELECTABLEInput Data Format Yes NoNormal Format Normal Normal Only NormalI 2 S FormatInput Resolution Yes No16 Bits 16 Bits 16 Bits Only 16 Bits18 BitsLRCIN Polarity Yes NoL/R = High/Low L/R = H/L L/R = H/L L/R = H/LL/R = Low/HighOnlyDe-emphasis Control Yes Yes32kHz44.1kHz OFF OFF48kHzOFFSoft Mute Yes OFF Yes OFFDigital Attenuation Yes 0dB No 0dBAnalog Output Mode Yes Stereo No StereoInfinite Zero Detection Yes Disabled No DisabledDAC Operation Control Yes ON No ONTABLE I. Feature Selections <strong>by</strong> Mode.HARDWARE MODE(Pin 14 = “0”)This mode is controlled <strong>by</strong> logic levels present on pins 15,16, 17 and 18. Hardware Mode allows for control of softmute, digital de-emphasis and disable ONLY. Other functionssuch as attenuation, I/O format and infinite zero detectcan only be controlled in the Software Mode.SOFT MUTE (Pin 18)A LOW level on pin 18 will force both channels to be muted;a HIGH level on pin 18 will allow for normal operation.RESET MODE (Pin 15)A LOW level on pin 15 will force the digital filters, modulatorsand mode controls into a reset (disable) mode. Whilethis pin is held low, the output of <strong>PCM1717</strong> will be forcedto V CC /2 (Bipolar Zero). Bringing pin 15 HIGH will initializeall DAC functions, and allow for normal operation.SOFTWARE MODE(Pin 14 = “1”)The Software Mode uses a three-wire interface on pins 16,17 and 18. Pin 17 (MC) is used to clock in the serial controldata, pin 18 (ML) is used to synchronize the serial controldata, and pin 16 (MD) is used to latch in the serial controlregister. There are four distinct registers, with bits 9 and 10(of 16) determining which register is in use.REGISTER CONTROL (Bits 9, 10)REGISTER B9 (A0) B10 (A1)0 0 01 1 02 0 13 1 1Control data timing is shown in Figure 6. ML is used to latchthe data from the control registers. After each register’scontents are checked in, ML should be taken low to latch inthe data. A “res” in the register indicates that location isreserved for factory use. When loading the registers, the“res” bits should be set LOW.REGISTER 0B15 B14 B13 B12 B11 B10 B9 B8 B7 B6 B5 B4 B3 B2 B1 B0res res res res res A1 A0 LDL AL7 AL6 AL5 AL4 AL3 AL2 AL1 AL0Register 0 is used to control left channel attenuation. Bits0-7 (AL0-AL7) are used to determine the attenuation level.The level of attenuation is given <strong>by</strong>:ATT = [20log 10 (ATT_DATA/255)] dB®<strong>PCM1717</strong>8

ATTENUATION DATA LOAD CONTROLBit 8 (LDL) is used to control the loading of attenuation datain B0:B7. When LDL is set to 0, attenuation data will beloaded into AL0:AL7, but it will not affect the attenuationlevel until LDL is set to 1. LDR in Register 1 has the samefunction for right channel attenuation. The attenuation levelis given <strong>by</strong>:ATT = 20log (y/256) (dB), where y = x, when 0 ≤ x ≤ 254y = x + 1, when x = 255X is the user-determined step number, an integer valuebetween 0 and 255.Example:let x = 255ATT = 20 log⎛ 255 + 1 ⎞⎝ 256 ⎠ = 0dBlet x = 254let x = 1let x = 0REGISTER 1ATT = 20 log⎛ 254 ⎞⎝ 256⎠ = –0.068dB1ATT = 20 log⎛ ⎞⎝ 256⎠ = –48.16dB0ATT = 20 log⎛ ⎞⎝ 256⎠ = –∞B15 B14 B13 B12 B11 B10 B9 B8 B7 B6 B5 B4 B3 B2 B1 B0res res res res res A1 A0 LDR AR7 AR6 AR5 AR4 AR3 AR2 AR1 AR0Register 1 is used to control right channel attenuation. Asin Register 1, bits 0-7 (AR0-AR7) control the level ofattenuation.REGISTER 2B15 B14 B13 B12 B11 B10 B9 B8 B7 B6 B5 B4 B3 B2 B1 B0res res res res res A1 A0 res res res res IZD OPE DM1 DM0 MUTERegister 2 is used to control soft mute, digital de-emphasis,disable, and infinite zero detect. Bit 0 is used for soft mute;a HIGH level on bit 0 will cause the output to be muted.Bits 1 and 2 are used to control digital de-emphasis asshown below:BIT 1 (DM0) BIT 2 (DM1) DE-EMPHASIS0 0 De-emphasis disabled1 0 De-emphasis enabled at 48kHz0 1 De-emphasis enabled at 44.1kHz1 1 De-emphasis enabled at 32kHzBits 3 (OPE) and 4 (IZD) are used to control the infinite zerodetection features. Tables II through IV illustrate the relationshipbetween IZD, OPE, and RSTB (reset control):IZD = 1IZD = 0RSTB = “HIGH”RSTB = “LOW”DATA INPUTDAC OUTPUTZero Forced to BPZ (1)OtherNormalZero Zero (2)OtherNormalTABLE II. Infinite Zero Detection (IZD) Function.OPE = 1OPE = 0SOFTWARE MODEDATA INPUT DAC OUTPUT INPUTZero Forced to BPZ (1) EnabledOther Forced to BPZ (1) EnabledZero Controlled <strong>by</strong> IZD EnabledOther Normal EnabledTABLE III. Output Enable (OPE) Function.SOFTWAREMODEDATA INPUT DAC OUTPUT INPUTZero Controlled <strong>by</strong> OPE and IZD EnabledOther Controlled <strong>by</strong> OPE and IZD EnabledZero Forced to BPZ (1) DisabledOther Forced to BPZ (1) DisabledTABLE IV. Reset (RSTB) Function.NOTE: (1) ∆∑ is disconnected from output amplifier. (2) ∆∑ is connected tooutput amplifier.OPE controls the operation of the DAC: when OPE is“LOW”, the DAC will convert all non-zero input data. If theinput data is continuously zero for 65,536 cycles of BCKIN,the output will only be forced to zero only if IZD is “HIGH”.When OPE is “HIGH”, the output of the DAC will be forcedto bipolar zero, irrespective of any input data.IZD controls the operation of the zero detect feature: whenIZD is “LOW”, the zero detect circuit is off. Under thiscondition, no automatic muting will occur if the input iscontinuously zero. When IZD is “HIGH”, the zero detectfeature is enabled. If the input data is continuously zero for65,536 cycle of BCKIN, the output will be immediatelyforced to a bipolar zero state (V CC /2). The zero detectionfeature is used to avoid noise which may occur when theinput is DC. When the output is forced to bipolar zero, theremay be an audible click. <strong>PCM1717</strong> allows the zero detectfeature to be disabled so the user can implement an externalmuting circuit.REGISTER 3B15 B14 B13 B12 B11 B10 B9 B8 B7 B6 B5 B4 B3 B2 B1 B0res res res res res A1 A0 res PL3 PL2 PL1 PL0 ATC IW LRP IISRegister 3 is used to select the I/O data formats. Bit 0 (IIS)is used to control the input data format. If the input datasource is normal (16- or 18-bit, MSB first, right-justified),set bit 0 “LOW”. If the input format is IIS, set bit 0 “HIGH”.9 <strong>PCM1717</strong>®

1 f/sLeft-channel DataRight-channel DataLRCIN (pin 4)BCKIN (pin 6)Audio Data Word = 16-BitDIN (pin 5)14 15MSB LSB MSB LSB16 1 2 3 14 15 161 2 3 14 15 16Audio Data Word = 18-BitDIN (pin 5)16 17MSB LSB MSB LSB18 1 2 3 16 17 181 2 316 17 18FIGURE 5. “Normal” Data Input Timing.1 f/sLeft-channel DataRight-channel DataLRCIN (pin 4)BCKIN (pin 6)Audio Data Word = 16-BitDIN (pin 5)MSB LSB MSB LSB1 2 3 14 15 161 2 3 14 15 161 2Audio Data Word = 18-BitDIN (pin 5)MSB LSB MSB LSB1 2 3 16 17 181 2 316 17 181 2FIGURE 6. “I 2 S” Data Input Timing.LRCINBCKINDIN50% of V DDt BCH t BCL t LB50% of V DDt BLt BCY50% of V DDt DH t DSBCKIN Pulsewidth (High Level) t BCH 50ns (min)BCKIN Pulsewidth (Low Level) t BCL 50ns (min)BCKIN Pulse Cycle Time t BCY 100ns (min)BCKIN Rising Edge ➝ LRCIN Edge t BL 30ns (min)LRCIN Edge ➝ BCKIN Rising Edge t LB 30ns (min)DIN Setup Time t DS 30ns (min)DIN Hold Time t DH 30ns (min)FIGURE 7. Data Input Timing.Bit 1 is used to select the polarity of LRCIN (sample rateclock). When bit 1 is LOW, a HIGH state on LRCIN is usedfor the left channel, and a LOW state on LRCIN is used forthe right channel. When bit 1 is HIGH the polarity of LRCINis reversed.Bit 2 is used to select the input word length. When bit 2 isLOW, the input word length is set for 16 bits; when bit 2 isHIGH, the input word length is set for 18 bits.Bit 3 is used as an attenuation control. When bit 3 is setHIGH, the attenuation data on Register 0 is used for bothchannels, and the data in Register 1 is ignored. When bit 3is LOW, each channel has separate attenuation data.Bits 4 through 7 are used to determine the output format, asshown in Table V:PL0 PL1 PL2 PL3 Lch OUTPUT Rch OUTPUT NOTE0 0 0 0 MUTE MUTE MUTE0 0 0 1 MUTE R0 0 1 0 MUTE L0 0 1 1 MUTE (L + R)/20 1 0 0 R MUTE0 1 0 1 R R0 1 1 0 R L REVERSE0 1 1 1 R (L + R)/21 0 0 0 L MUTE1 0 0 1 L R STEREO1 0 1 0 L L1 0 1 1 L (L + R)/21 1 0 0 (L + R)/2 MUTE1 1 0 1 (L + R)/2 R1 1 1 0 (L + R)/2 L1 1 1 1 (L + R)/2 (L + R)/2 MONOTABLE V. <strong>PCM1717</strong> Output Mode Control.REGISTER RESET STATESAfter reset, each register is set to a predetermined state:Register 0 0000 0000 1111 1111Register 1 0000 0010 1111 1111Register 2 0000 0100 0000 0000Register 3 0000 0110 1001 0000®<strong>PCM1717</strong>10

ML (pin 18)MC (pin 17)MD (pin 16)B15 B14 B13 B12 B11 B10 B9 B8 B7 B6 B5 B4 B3 B2 B1 B0MLMCMDt MLHt MDHt MCLt MLLt MHH50% of V DD50% of V DD50% of V DDMC Pulse Cycle t MCY 100ns (min)MC Pulsewidth “L” t MCL 50ns (min)MC Pulse Cycle “H” t MCH 50ns (min)MD Setup Time t MDS 30ns (min)MD Hold Time t MDH 30ns (min)ML Setup Time t MLS 30ns (min)ML Hold Time t MLH 30ns (min)ML Pulsewidth “L” t MLL 30ns + 1SYSCLK (min)ML High Level Time t MHH 30ns + 1SYSCLK (min)FIGURE 8. Control Data Timing in Software Mode Control.RSTB50% of V DDt RSTRSTB Pulsewidth20ns (min)FIGURE 9. External Reset Timing.0.1µF ~ 10µFBypass Capacitor+5V Analog <strong>Power</strong> Supply10pF ~ 22pF1XTI2 3CLKO19FOUT = Inverted XTI (1 pin)to Other System10pF ~ 22pF20XTOPCMAudio DataProcessor456LRCINDINBCKINV OUT RD/C_R98+10µFPostLow PassFilter(optional)Mode ControlControlProcessor141817MODEML/MUTEMC/DM1D/C_LV OUT L131210µF+V DD4.7kΩPostLow PassFilter(optional)16MD/DM0ZERO7To External Mute CircuitReset15RSTBDGND V DD10 11AGNDV CC0.1µF ~ 10µFBypass CapacitorFIGURE 10. Typical Connection Diagram of <strong>PCM1717</strong>.11 <strong>PCM1717</strong>®

POWER SUPPLYCONNECTIONS<strong>PCM1717</strong> has two power supply connections: digital (V DD )and analog (V CC ). Each connection also has a separateground. If the power supplies turn on at different times, thereis a possibility of a latch-up condition. To avoid this condition,it is recommended to have a common connectionbetween the digital and analog power supplies. If separatesupplies are used without a common connection, the deltabetween the two supplies during ramp-up time must be lessthan 0.6V.An application circuit to avoid a latch-up condition is shownin Figure 11.A block diagram of the 5-level delta-sigma modulator isshown in Figure 12. This 5-level delta-sigma modulator hasthe advantage of stability and clock jitter sensitivity over thetypical one-bit (2 level) delta-sigma modulator.The combined oversampling rate of the delta-sigma modulatorand the internal 8-times interpolation filter is 48f S fora 384f S system clock, and 64f S for a 256f S system clock. Thetheoretical quantization noise performance of the 5-leveldelta-sigma modulator is shown in Figure 13.Digital<strong>Power</strong> SupplyAnalog<strong>Power</strong> SupplyV DDDGNDV CCAGND2003rd-ORDER ∆Σ MODULATOR–20FIGURE 11. Latch-up Prevention Circuit.BYPASSING POWER SUPPLIESThe power supplies should be <strong>by</strong>passed as close as possibleto the unit. Refer to Figure 10 for optimal values of <strong>by</strong>passcapacitors.THEORY OF OPERATIONThe delta-sigma section of <strong>PCM1717</strong> is based on a 5-levelamplitude quantizer and a 3rd-order noise shaper. Thissection converts the oversampled input data to 5-level deltasigmaformat.Gain (–dB)–40–60–80–100–120–140–1600 5 10 15 20Frequency (kHz)FIGURE 13. Quantization Noise Spectrum.25In+++++Z –1 Z –1+Z –18f S18-Bit––+++5-level Quantizer4Out48f S (384f S )64f S (256f S )3210FIGURE 12. 5-Level ∆Σ Modulator Block Diagram.®<strong>PCM1717</strong>12

APPLICATIONCONSIDERATIONSDELAY TIMEThere is a finite delay time in delta-sigma converters. In A/Dconverters, this is commonly referred to as latency. For adelta-sigma D/A converter, delay time is determined <strong>by</strong> theorder number of the FIR filter stage, and the chosen samplingrate. The following equation expresses the delay time of<strong>PCM1717</strong>:The performance of the internal low pass filter from DC to24kHz is shown in Figure 14. The higher frequency rolloffof the filter is shown in Figure 15. If the user’s applicationhas the <strong>PCM1717</strong> driving a wideband amplifier, it is recommendedto use an external low pass filter. A simple 3rdorderfilter is shown in Figure 16. For some applications, apassive RC filter or 2nd-order filter may be adequate.1.0INTERNAL ANALOG FILTER FREQUENCY RESPONSE(20Hz~24kHz, Expanded Scale)T D = 11.125 x 1/f SFor f S = 44.1kHz, T D = 11.125/44.1kHz = 251.4µsApplications using data from a disc or tape source, such asCD audio, CD-Interactive, Video CD, DAT, Minidisc, etc.,generally are not affected <strong>by</strong> delay time. For some professionalapplications such as broadcast audio for studios, it isimportant for total delay time to be less than 2ms.INTERNAL RESETWhen power is first applied to <strong>PCM1717</strong>, an automatic resetfunction occurs after 1,024 cycles of XTI clock. Refer toTable I for default conditions. During the first 1,024 cyclesof XTI clock, <strong>PCM1717</strong> cannot be programmed (SoftwareControl). Data can be loaded into the control registers duringthis time, and after 1,204 cycles of XTI clock, a "LOW" onML (pin 18) will initiate programming.OUTPUT FILTERINGFor testing purposes all dynamic tests are done on the<strong>PCM1717</strong> using a 20kHz low pass filter. This filter limitsthe measured bandwidth for THD+N, etc. to 20kHz. Failureto use such a filter will result in higher THD+N and lowerSNR and Dynamic Range readings than are found in thespecifications. The low pass filter removes out of bandnoise. Although it is not audible, it may affect dynamicspecification numbers.dB0.50–0.5–1.020100 1k 10k 24kFrequency (Hz)FIGURE 14. Low Pass Filter Frequency Response.dBINTERNAL ANALOG FILTER FREQUENCY RESPONSE(10Hz~10MHz)1050–5–10–15–20–25–30–35–40–45–50–55–6010 100 1k 10k 100k 1M 10MFrequency (Hz)FIGURE 15. Low Pass Filter Frequency Response.6GAIN vs FREQUENCY90Gain–140+V SIN–10kΩ10kΩ680pF1500pF10kΩOPA604100pFGain (dB)–34–54Phase–90–180Phase (°)–74–270–94–360100 1k 10k 100k 1MFrequency (Hz)FIGURE 16. 3rd-Order LPF.13 <strong>PCM1717</strong>®

Test Disk Shibasoku #725ThroughLchCDPlayerDigitalDAIDEM-<strong>PCM1717</strong>Rch11th-orderLPFPGATHDMeter0dB/60dB30KHz LPF onFor test of S/N ratio and Dynamic Range, A-filter ON.FIGURE 17. Test Block Diagram.TEST CONDITIONSFigure 17 illustrates the actual test conditions applied to<strong>PCM1717</strong> in production. The 11th-order filter is necessaryin the production environment for the removal of noiseresulting from the relatively long physical distance betweenthe unit and the test analyzer. In most actual applications, the3rd-order filter shown in Figure 16 is adequate. Undernormal conditions, THD+N typical performance is –70dBwith a 30kHz low pass filter (shown here on the THDmeter), improving to –89dB when the external 20kHz 11thorderfilter is used.EVALUATION FIXTURESThree evaluation fixtures are available for <strong>PCM1717</strong>.DEM-<strong>PCM1717</strong>This evaluation fixture is primarily intended for quick evaluationof the <strong>PCM1717</strong>’s performance. DEM-<strong>PCM1717</strong> canaccept either an external clock or a user-installed crystaloscillator. All of the functions can be controlled <strong>by</strong> on-boardswitches. DEM-<strong>PCM1717</strong> does not contain a receiver chipor an external low pass filter. DEM-<strong>PCM1717</strong> requires asingle +5V power supply.OUT-OF-BAND NOISE CONSIDERATIONSDelta-sigma DACs are <strong>by</strong> nature very sensitive to jitter onthe master clock. Phase noise on the clock will result in anincrease in noise, ultimately degrading dynamic range. It isdifficult to quantify the effect of jitter due to problems insynthesizing low levels of jitter. One of the reasons deltasigmaDACs are prone to jitter sensitivity is the largequantization noise when the modulator can only achieve twodiscrete output levels (0 or 1). The multi-level delta-sigmaDAC has improved theoretical SNR because of multipleoutput states. This reduces sensitivity to jitter. Figure 18contrasts jitter sensitivity between a one-bit PWM type DACand multi-level delta-sigma DAC. The data was derivedusing a simulator, where clock jitter could be completelysynthesized.Dynamic Range (dB)110105100Multi-level9590858075PWM7065600 100 200 300 400 500 600Clock Jitter (ps)FIGURE 18. Simulation Results of Clock Jitter Sensitivity.2114.4ps0–148fs2FIGURE 19. Simulation Method for Clock Jitter.®<strong>PCM1717</strong>14

PACKAGE OPTION ADDENDUMwww.ti.com23-Jan-2004PACKAGING INFORMATIONORDERABLE DEVICE STATUS(1) PACKAGE TYPE PACKAGE DRAWING PINS PACKAGE QTY<strong>PCM1717</strong>E ACTIVE SSOP DB 20 65<strong>PCM1717</strong>E/2K ACTIVE SSOP DB 20 2000<strong>PCM1717</strong>EG ACTIVE SSOP DB 20 65(1) The marketing status values are defined as follows:ACTIVE: Product device recommended for new designs.LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part ina new design.PREVIEW: Device has been announced but is not in production. Samples may or may not be available.OBSOLETE: TI has discontinued the production of the device.

IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications,enhancements, improvements, and other changes to its products and services at any time and to discontinueany product or service without notice. Customers should obtain the latest relevant information before placingorders and should verify that such information is current and complete. All products are sold subject to TI’s termsand conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale inaccordance with TI’s standard warranty. Testing and other quality control techniques are used to the extent TIdeems necessary to support this warranty. Except where mandated <strong>by</strong> government requirements, testing of allparameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design. Customers are responsible fortheir products and applications using TI components. To minimize the risks associated with customer productsand applications, customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right,copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or processin which TI products or services are used. Information published <strong>by</strong> TI regarding third-party products or servicesdoes not constitute a license from TI to use such products or services or a warranty or endorsement thereof.Use of such information may require a license from a third party under the patents or other intellectual propertyof the third party, or a license from TI under the patents or other intellectual property of TI.Reproduction of information in TI data books or data sheets is permissible only if reproduction is withoutalteration and is accompanied <strong>by</strong> all associated warranties, conditions, limitations, and notices. Reproductionof this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable forsuch altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated <strong>by</strong> TI for thatproduct or service voids all express and any implied warranties for the associated TI product or service andis an unfair and deceptive business practice. TI is not responsible or liable for any such statements.Following are URLs where you can obtain information on other Texas Instruments products and applicationsolutions:ProductsApplications<strong>Amp</strong>lifiers amplifier.ti.com Audio www.ti.com/audioData Converters dataconverter.ti.com Automotive www.ti.com/automotiveDSP dsp.ti.com Broadband www.ti.com/broadbandInterface interface.ti.com Digital Control www.ti.com/digitalcontrolLogic logic.ti.com Military www.ti.com/military<strong>Power</strong> Mgmt power.ti.com Optical Networking www.ti.com/opticalnetworkMicrocontrollers microcontroller.ti.com Security www.ti.com/securityTelephonywww.ti.com/telephonyVideo & Imaging www.ti.com/videoWirelesswww.ti.com/wirelessMailing Address:Texas InstrumentsPost Office Box 655303 Dallas, Texas 75265Copyright © 2004, Texas Instruments Incorporated