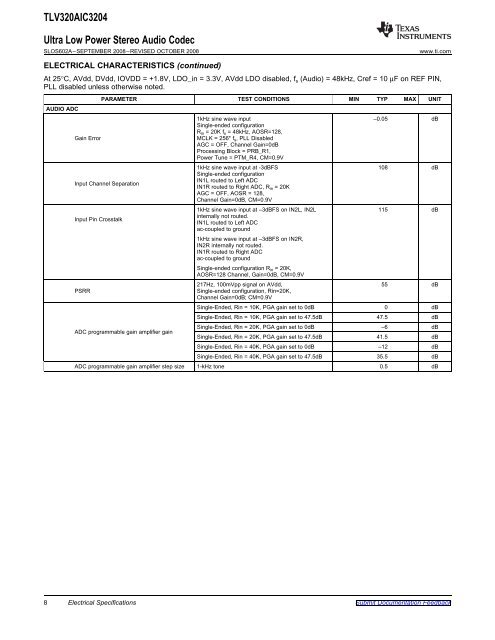

TLV320AIC3204<strong>Ultra</strong> <strong>Low</strong> <strong>Power</strong> <strong>Stereo</strong> <strong>Audio</strong> <strong>Codec</strong>SLOS602A–SEPTEMBER 2008–REVISED OCTOBER 2008www.ti.comELECTRICAL CHARACTERISTICS (continued)At 25°C, AVdd, DVdd, IOVDD = +1.8V, LDO_in = 3.3V, AVdd LDO disabled, f s (<strong>Audio</strong>) = 48kHz, Cref = 10 µF on REF PIN,PLL disabled unless otherwise noted.AUDIO ADCGain ErrorPARAMETER TEST CONDITIONS MIN TYP MAX UNITInput Channel SeparationInput Pin CrosstalkPSRRADC programmable gain amplifier gain1kHz sine wave input –0.05 dBSingle-ended configurationR in = 20K f s = 48kHz, AOSR=128,MCLK = 256* f s , PLL DisabledAGC = OFF, Channel Gain=0dBProcessing Block = PRB_R1,<strong>Power</strong> Tune = PTM_R4, CM=0.9V1kHz sine wave input at -3dBFS 108 dBSingle-ended configurationIN1L routed to Left ADCIN1R routed to Right ADC, R in = 20KAGC = OFF, AOSR = 128,Channel Gain=0dB, CM=0.9V1kHz sine wave input at –3dBFS on IN2L, IN2L 115 dBinternally not routed.IN1L routed to Left ADCac-coupled to ground1kHz sine wave input at –3dBFS on IN2R,IN2R internally not routed.IN1R routed to Right ADCac-coupled to groundSingle-ended configuration R in = 20K,AOSR=128 Channel, Gain=0dB, CM=0.9V217Hz, 100mVpp signal on AVdd, 55 dBSingle-ended configuration, Rin=20K,Channel Gain=0dB; CM=0.9VSingle-Ended, Rin = 10K, PGA gain set to 0dB 0 dBSingle-Ended, Rin = 10K, PGA gain set to 47.5dB 47.5 dBSingle-Ended, Rin = 20K, PGA gain set to 0dB –6 dBSingle-Ended, Rin = 20K, PGA gain set to 47.5dB 41.5 dBSingle-Ended, Rin = 40K, PGA gain set to 0dB –12 dBSingle-Ended, Rin = 40K, PGA gain set to 47.5dB 35.5 dBADC programmable gain amplifier step size 1-kHz tone 0.5 dB8 Electrical SpecificationsSubmit Documentation Feedback

TLV320AIC3204<strong>Ultra</strong> <strong>Low</strong> <strong>Power</strong> <strong>Stereo</strong> <strong>Audio</strong> <strong>Codec</strong>www.ti.com SLOS602A–SEPTEMBER 2008–REVISED OCTOBER 2008ELECTRICAL CHARACTERISTICS (continued)At 25°C, AVdd, DVdd, IOVDD = +1.8V, LDO_in = 3.3V, AVdd LDO disabled, f s (<strong>Audio</strong>) = 48kHz, Cref = 10 µF on REF PIN,PLL disabled unless otherwise noted.PARAMETER TEST CONDITIONS MIN TYP MAX UNITANALOG BYPASS TO HEADPHONE AMPLIFIER, DIRECT MODEDevice SetupLoad = 16Ω (single-ended), 50pF;Input and Output CM=0.9V;Headphone Output on LDOIN Supply;IN1L routed to HPL and IN1R routed to HPR;Channel Gain=0dBGain Error –0.8 dBNoise, A-weighted (1) Idle Channel, IN1L and IN1R ac-shorted to ground 3 µV RMSTHD Total Harmonic Distortion 446mVrms, 1-kHz input signal –89 dBANALOG BYPASS TO LINE-OUT AMPLIFIER, PGA MODEDevice SetupMICROPHONE BIASLoad = 10KOhm (single-ended), 56pF;Input and Output CM=0.9V;LINE Output on LDOIN Supply;IN1L routed to ADCPGA_L and IN1R routed toADCPGA_R; Rin = 20kADCPGA_L routed to LOL and ADCPGA_R routedto LOR; Channel Gain = 0dBGain Error 0.6 dBIdle Channel, 7 µV RMSIN1L and IN1R ac-shorted to groundNoise, A-weighted (1) Channel Gain=40dB, 3.4 µV RMSInput Signal (0dB) = 5mV rmsInputs ac-shorted to ground, Input ReferredBias voltage Bias voltage CM=0.9V, LDOin = 3.3VMicbias Mode 0, Connect to AVdd or LDOin 1.25 VMicbias Mode 1, Connect to LDOin 1.7 VMicbias Mode 2, Connect to LDOin 2.5 VMicbias Mode 3, Connect to AVdd AVdd VMicbias Mode 3, Connect to LDOin LDOin VCM=0.75V, LDOin = 3.3VMicbias Mode 0, Connect to AVdd or LDOin 1.04 VMicbias Mode 1, Connect to AVdd or LDOin 1.425 VMicbias Mode 2, Connect to LDOin 2.075 VMicbias Mode 3, Connect to AVdd AVdd VMicbias Mode 3, Connect to LDOin LDOin VOutput Noise CM=0.9V, Micbias Mode 2, A-weighted, 20Hz to 1020kHz bandwidth,Current load = 0mA.Current Sourcing Micbias Mode 2, Connect to LDOin 3 mAInline ResistanceMicbias Mode 3, Connect to AVdd 140Micbias Mode 3, Connect to LDOin 87(1) All performance measurements done with 20-kHz low-pass filter and, where noted, A-weighted filter. Failure to use such a filter mayresult in higher THD+N and lower SNR and dynamic range readings than shown in the Electrical Characteristics. The low-pass filterremoves out-of-band noise, which, although not audible, may affect dynamic specification valuesµV RMSΩSubmit Documentation Feedback Electrical Specifications 9

- Page 1 and 2: LDO inLDO SelectAVddDVddIOVddAVssDV

- Page 3 and 4: LORLOLIN3_RIN3_LMICBIASREFTLV320AIC

- Page 5 and 6: TLV320AIC3204Ultra Low Power Stereo

- Page 7: 3.3 ELECTRICAL CHARACTERISTICSTLV32

- Page 11 and 12: TLV320AIC3204Ultra Low Power Stereo

- Page 13 and 14: All numbers are from characterizati

- Page 15 and 16: 3.4.3.2 TYPICAL TIMING CHARACTERIST

- Page 17 and 18: 4 TYPICAL CHARACTERISTICS4.1 TYPICA

- Page 19 and 20: 4.2 FFTTLV320AIC3204Ultra Low Power

- Page 21 and 22: 5 Application Information5.1 TYPICA

- Page 23 and 24: 5.2.6 Register Settings for Multifu

- Page 25 and 26: 5.3 ANALOG ROUTINGTLV320AIC3204Ultr

- Page 27 and 28: 5.5 POWERTUNE5.5.1 PowerTune Modes5

- Page 29 and 30: 5.5.2.4 ADC, Mono, 48kHz, Highest P

- Page 31 and 32: 5.5.2.9 ADC, Stereo, 8kHz, Lowest P

- Page 33 and 34: 5.5.2.14 ADC, Stereo, 192kHz, Lowes

- Page 35 and 36: 5.5.3.2 DAC, Stereo, 48kHz, Lowest

- Page 37 and 38: 5.5.3.6 DAC, Stereo, 8kHz, Lowest P

- Page 39 and 40: 5.5.3.10 DAC, Stereo, 192kHz, Lowes

- Page 41 and 42: 5.7.2 Digital Volume Control5.7.3 F

- Page 43 and 44: NH(z) 2023 N D11z11zTLV320AIC3204Ul

- Page 45 and 46: 5.8 ADC Decimation Filtering and Si

- Page 47 and 48: 5.8.2.5 3 Biquads, 1 st order IIR,

- Page 49 and 50: 5.8.3.2 Biquad SectionNH(z) 2023 2

- Page 51 and 52: 5.8.4.1 Decimation Filter ATLV320AI

- Page 53 and 54: 5.8.4.3 Decimation Filter CTLV320AI

- Page 55 and 56: TLV320AIC3204Ultra Low Power Stereo

- Page 57 and 58: 5.9.7 Adaptive FilteringTLV320AIC32

- Page 59 and 60:

TLV320AIC3204Ultra Low Power Stereo

- Page 61 and 62:

5.11.1 Processing BlocksTLV320AIC32

- Page 63 and 64:

5.11.2.6 4 Biquads, Filter BTLV320A

- Page 65 and 66:

5.11.3 User Programmable Filters5.1

- Page 67 and 68:

TLV320AIC3204Ultra Low Power Stereo

- Page 69 and 70:

TLV320AIC3204Ultra Low Power Stereo

- Page 71 and 72:

5.12.2 Headphone Amplifier Class-D

- Page 73 and 74:

TLV320AIC3204Ultra Low Power Stereo

- Page 75 and 76:

5.13.3.1 DRC Threshold5.13.3.2 DRC

- Page 77 and 78:

5.14.2 DIGITAL AUTO MUTE5.14.3 Adap

- Page 79 and 80:

5.16 CLOCK GENERATION AND PLLTLV320

- Page 81 and 82:

TLV320AIC3204Ultra Low Power Stereo

- Page 83 and 84:

5.16.1 PLLTLV320AIC3204Ultra Low Po

- Page 85 and 86:

5.17 INTERFACE5.17.1 AUDIO DIGITAL

- Page 87 and 88:

TLV320AIC3204Ultra Low Power Stereo

- Page 89 and 90:

TLV320AIC3204Ultra Low Power Stereo

- Page 91 and 92:

5.17.2.1 I 2 C CONTROL MODETLV320AI

- Page 93 and 94:

TLV320AIC3204Ultra Low Power Stereo

- Page 95 and 96:

5.18.1.3 Other Supply Options5.19 R

- Page 97 and 98:

TLV320AIC3204Ultra Low Power Stereo

- Page 99 and 100:

5.22.3 DAC Playback Through Class-D

- Page 101 and 102:

5.22.5 Stereo ADC with 48ksps Sampl

- Page 103 and 104:

6 REGISTER MAP6.1 Register Map Summ

- Page 105 and 106:

6.2.9 Page 0 / Register 8: Clock Se

- Page 107 and 108:

6.2.19 Page 0 / Register 19: Clock

- Page 109 and 110:

6.2.29 Page 0 / Register 29: Audio

- Page 111 and 112:

6.2.36 Page 0 / Register 36: ADC Fl

- Page 113 and 114:

6.2.43 Page 0 / Register 45: Sticky

- Page 115 and 116:

TLV320AIC3204Ultra Low Power Stereo

- Page 117 and 118:

6.2.54 Page 0 / Register 57-59: Res

- Page 119 and 120:

6.2.61 Page 0 / Register 66: Right

- Page 121 and 122:

6.2.67 Page 0 / Register 72: Beep G

- Page 123 and 124:

6.2.79 Page 0 / Register 84: Right

- Page 125 and 126:

6.2.85 Page 0 / Register 90: Left C

- Page 127 and 128:

6.2.92 Page 0 / Register 97: Right

- Page 129 and 130:

6.2.98 Page 0 / Register 103: DC Me

- Page 131 and 132:

6.2.109 Page 1 / Register 3: Playba

- Page 133 and 134:

6.2.117 Page 1 / Register 14: LOL R

- Page 135 and 136:

TLV320AIC3204Ultra Low Power Stereo

- Page 137 and 138:

TLV320AIC3204Ultra Low Power Stereo

- Page 139 and 140:

TLV320AIC3204Ultra Low Power Stereo

- Page 141 and 142:

TLV320AIC3204Ultra Low Power Stereo

- Page 143 and 144:

6.2.134 Page 1 / Register 55: Right

- Page 145 and 146:

6.2.141 Page 1 / Register 62: ADC A

- Page 147 and 148:

6.2.152 Page 9-16 / Register 0: Pag

- Page 149 and 150:

6.2.167 Page 62-70 / Register 8-127

- Page 151 and 152:

TLV320AIC3204Ultra Low Power Stereo

- Page 153 and 154:

PACKAGE OPTION ADDENDUMwww.ti.com26

- Page 155:

PACKAGE MATERIALS INFORMATIONwww.ti