A Delta-Sigma Fractional-N Frequency Synthesizer for Quad ... - JSTS

A Delta-Sigma Fractional-N Frequency Synthesizer for Quad ... - JSTS

A Delta-Sigma Fractional-N Frequency Synthesizer for Quad ... - JSTS

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

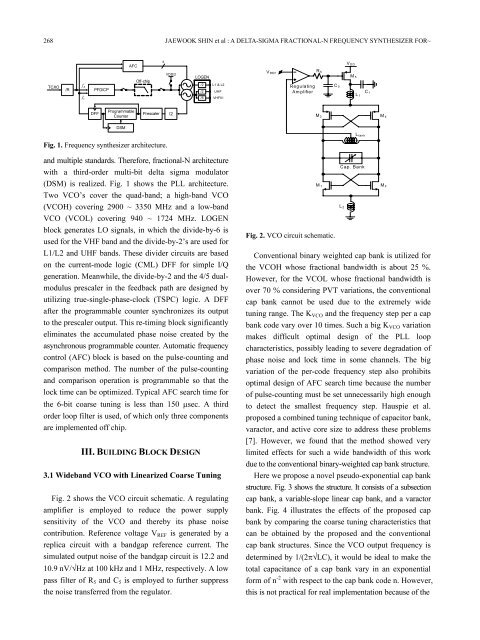

268 JAEWOOK SHIN et al : A DELTA-SIGMA FRACTIONAL-N FREQUENCY SYNTHESIZER FOR~AFC6V DDTCXO/RfRf VPFD/CPOff-chipVDD/2LOGEN/2/2/6L1 & L2UHFVHFIIIV REFRegulatingAm plifierR 5C 5M 5L 1C 1ProgrammableDFF Prescaler /2CounterM 3 M 4DSML tankFig. 1. <strong>Frequency</strong> synthesizer architecture.and multiple standards. There<strong>for</strong>e, fractional-N architecturewith a third-order multi-bit delta sigma modulator(DSM) is realized. Fig. 1 shows the PLL architecture.Two VCO’s cover the quad-band; a high-band VCO(VCOH) covering 2900 ~ 3350 MHz and a low-bandVCO (VCOL) covering 940 ~ 1724 MHz. LOGENblock generates LO signals, in which the divide-by-6 isused <strong>for</strong> the VHF band and the divide-by-2’s are used <strong>for</strong>L1/L2 and UHF bands. These divider circuits are basedon the current-mode logic (CML) DFF <strong>for</strong> simple I/Qgeneration. Meanwhile, the divide-by-2 and the 4/5 dualmodulusprescaler in the feedback path are designed byutilizing true-single-phase-clock (TSPC) logic. A DFFafter the programmable counter synchronizes its outputto the prescaler output. This re-timing block significantlyeliminates the accumulated phase noise created by theasynchronous programmable counter. Automatic frequencycontrol (AFC) block is based on the pulse-counting andcomparison method. The number of the pulse-countingand comparison operation is programmable so that thelock time can be optimized. Typical AFC search time <strong>for</strong>the 6-bit coarse tuning is less than 150 μsec. A thirdorder loop filter is used, of which only three componentsare implemented off chip.III. BUILDING BLOCK DESIGN3.1 Wideband VCO with Linearized Coarse TuningFig. 2 shows the VCO circuit schematic. A regulatingamplifier is employed to reduce the power supplysensitivity of the VCO and thereby its phase noisecontribution. Reference voltage V REF is generated by areplica circuit with a bandgap reference current. Thesimulated output noise of the bandgap circuit is 12.2 and10.9 nV/√Hz at 100 kHz and 1 MHz, respectively. A lowpass filter of R 5 and C 5 is employed to further suppressthe noise transferred from the regulator.Fig. 2. VCO circuit schematic.Cap. BankM 1 M 2Conventional binary weighted cap bank is utilized <strong>for</strong>the VCOH whose fractional bandwidth is about 25 %.However, <strong>for</strong> the VCOL whose fractional bandwidth isover 70 % considering PVT variations, the conventionalcap bank cannot be used due to the extremely widetuning range. The K VCO and the frequency step per a capbank code vary over 10 times. Such a big K VCO variationmakes difficult optimal design of the PLL loopcharacteristics, possibly leading to severe degradation ofphase noise and lock time in some channels. The bigvariation of the per-code frequency step also prohibitsoptimal design of AFC search time because the numberof pulse-counting must be set unnecessarily high enoughto detect the smallest frequency step. Hauspie et al.proposed a combined tuning technique of capacitor bank,varactor, and active core size to address these problems[7]. However, we found that the method showed verylimited effects <strong>for</strong> such a wide bandwidth of this workdue to the conventional binary-weighted cap bank structure.Here we propose a novel pseudo-exponential cap bankstructure. Fig. 3 shows the structure. It consists of a subsectioncap bank, a variable-slope linear cap bank, and a varactorbank. Fig. 4 illustrates the effects of the proposed capbank by comparing the coarse tuning characteristics thatcan be obtained by the proposed and the conventionalcap bank structures. Since the VCO output frequency isdetermined by 1/(2π√LC), it would be ideal to make thetotal capacitance of a cap bank vary in an exponential<strong>for</strong>m of n -2 with respect to the cap bank code n. However,this is not practical <strong>for</strong> real implementation because of theL 2