ICM7226A, ICM7226B - Syntax Taiwan

ICM7226A, ICM7226B - Syntax Taiwan

ICM7226A, ICM7226B - Syntax Taiwan

- No tags were found...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

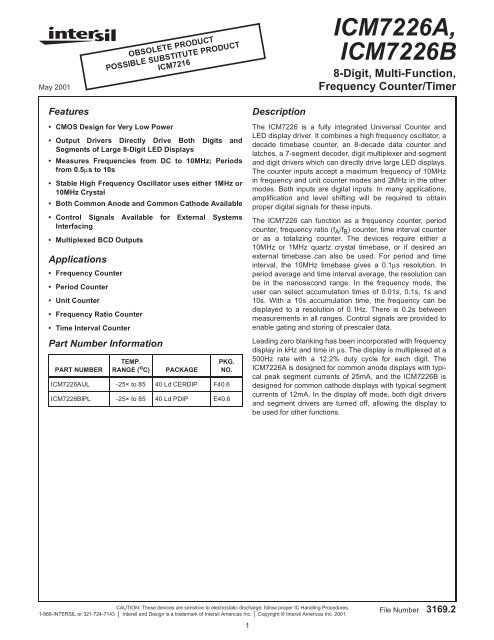

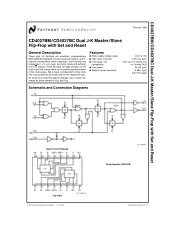

<strong>ICM7226A</strong>, <strong>ICM7226B</strong>Pinouts<strong>ICM7226A</strong>COMMON ANODE (CERDIP)TOP VIEWCONTROL INPUTINPUT BMEASUREMENT IN PROGRESSFUNCTIONSTOREBCD 4BCD 8DPSEG eSEG gSEG aV SSSEG dSEG bSEG cSEG fBCD 2BCD 1RST INPUTEXT DP IN123456789101112131415161718192040 INPUT A39 HOLD38 BUF OSC OUT37 NC (NOTE 1)36 OSC OUT35 OSC IN34 NC (NOTE 1)33 EXT OSC IN32 RST OUT31 EXT RANGE30 D129 D228 D327 D426 D525 V DD24 D623 D722 D821 RANGE<strong>ICM7226B</strong>COMMON CATHODE (PDIP)TOP VIEWCONTROL INPUTINPUT BMEASUREMENT IN PROGRESSFUNCTIONSTOREBCD 4BCD 8D1D3D2D4V SSD5D6D7D8BCD 2BCD 1RST INPUTEXT DP IN123456789101112131415161718192040 INPUT A39 HOLD38 BUF OSC OUT37 NC (NOTE 1)36 OSC OUT35 OSC IN34 NC (NOTE 1)33 EXT OSC IN32 RST OUT31 EXT RANGE30 DP OUT29 SEG g28 SEG e27 SEG a26 SEG d25 V DD24 SEG b23 SEG c22 SEG f21 RANGENOTE:1. For maximum frequency stability, connect to V DD or V SS .2

<strong>ICM7226A</strong>, <strong>ICM7226B</strong>Absolute Maximum RatingsMaximum Supply Voltage (V DD -V SS )....................6.5VMaximumDigitOutputCurrent........................400mAMaximumSegmentOutputCurrent.....................60mAVoltage On Any Input orOutputTerminal(Note1) ..............V DD +0.3V to V SS -0.3VOperating ConditionsTemperatureRange..........................-25 o Cto85 o CThermal InformationThermal Resistance (Typical, Note 2) θ JA ( o C/W) θ JC ( o C/W)CERDIPPackage................ 45 9PDIPPackage................... 50 N/AMaximum Junction TemperatureCERDIPPackage................................175 o CPDIPPackage...................................150 o CMaximumStorageTemperatureRange ..........-55 o Cto150 o CMaximumLeadTemperature(Soldering10s).............300 o CCAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operationof the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.NOTES:1. Destructive latchup may occur if input signals are applied before the power supply is established or if inputs or outputs are forced tovoltages exceeding V DD or V SS by 0.3V.2. θ JA is measured with the component mounted on an evaluation PC board in free air.Electrical SpecificationsV DD =5.0V,T A =25 o C, Unless Otherwise SpecifiedPARAMETER TEST CONDITIONS MIN TYP MAX UNITSOperating Supply Current, I DD Display Off, Unused Inputs to V SS - 2 5 mASupply Voltage Range (V DD -V SS ), V SUPPLY -25 o Cto85 o C, INPUT A,INPUT B Frequency at f MAX4.75 - 6.0 VMaximum Frequency INPUT A, Pin 40, f A(MAX)-25 o Cto85 o C4.75V < V DD

<strong>ICM7226A</strong>, <strong>ICM7226B</strong>Typical Performance Curves200T A =25 o CV DD =5.5V3004.5 ≤ V DD ≤ 6.0V50V DD =5.0VV DD =4.5V200I DIGIT (mA)10050I DIG (mA)10085 o C25 o C-20 o C00 1 2 3V OUT (V)00 1 2 3V DD -V OUT (V)FIGURE 2. <strong>ICM7226B</strong> TYPICAL I DIGIT vs V OUTFIGURE 3. <strong>ICM7226A</strong> TYPICAL I DIG vs V DD -V OUT304.5 ≤ V DD ≤ 6.0V-20 o C80T A =25 o CV DD =5.5V2025 o C60V DD =5.0VI SEG (mA)85 o CI SEG (mA)40V DD =4.5V102000 1 2 3V DD -V OUT (V)00 1 2 3V OUT (V)FIGURE 4. <strong>ICM7226B</strong> TYPICAL I SEG vs V DD -V OUTFIGURE 5. <strong>ICM7226A</strong> TYPICAL I SEG vs V OUT200150V DD =5.0V-20 o C25 o C8060V DD =5.0V-20 o C25 o CI DIGIT (mA)10085 o CI SEG (mA)4085 o C50200 0 1 2 3V OUT (V)00 1 2 3V OUT (V)FIGURE 6. <strong>ICM7226B</strong> TYPICAL I DIGIT vs V OUTFIGURE 7. <strong>ICM7226A</strong> TYPICAL I SEG vs V OUT6

<strong>ICM7226A</strong>, <strong>ICM7226B</strong>Typical Performance Curves (Continued)20f A (MAX) FREQUENCY UNIT COUNTER,FREQUENCY RATIO MODESFREQUENCY (MHz)15105f A (MAX) f B (MAX) PERIODTIME INTERVAL MODEST A =25 o C03 4 5 6V DD -V SS (V)FIGURE 8. f A (MAX), f B (MAX) AS A FUNCTION OF SUPPLYDescriptionINPUTS A and BThe signal to be measured is applied to INPUT A infrequency period, unit counter, frequency ratio and timeinterval modes. The other input signal to be measured isapplied to INPUT B in frequency ratio and time interval. f Ashould be higher than f B during frequency ratio.INPUT A 4.5V0.5V50ns MINCOUNTEDTRANSITIONS50ns MINt r =t f =10nsFIGURE 9. WAVEFORM FOR GUARANTEED MINIMUM f A (MAX)FUNCTION = FREQUENCY, FREQUENCY RATIO,UNIT COUNTERBoth inputs are digital inputs with a typical switching thresholdof2.0VatVDD = 5.0V and input impedance of 250kΩ.For optimum performance, the peak-to-peak input signalshould be at least 50% of the supply voltage and centeredabout the switching voltage. When these inputs are beingdriven from TTL logic, it is desirable to use a pullup resistor.The circuit counts high to low transitions at both inputsNote that the amplitude of the input should not exceed thedevice supply (above the V DD and below the V SS )bymorethan 0.3V, otherwise the device may be damaged.Multiplexed InputsThe FUNCTION, RANGE, CONTROL and EXTERNALDECIMAL POINT inputs are time multiplexed to select thefunction desired. This is achieved by connecting the appropriateDigit driver output to the inputs. The function, rangeand control inputs must be stable during the last half of eachdigit output, (typically 125µs). The multiplexed inputs areactive high for the common anode lCM7226A and active lowfor the common cathode lCM7226B.INPUT A ORINPUT B4.5V0.5V250nsMINMEASUREDINTERVAL250nsMINt r =t f = 10sNoise on the multiplex inputs can cause improper operation.This is particularly true when the unit counter mode ofoperation is selected, since changes in voltage on the digitdrivers can be capacitively coupled through the LED diodesto the multiplex inputs. For maximum noise immunity, a 10kΩresistor should be placed in series with the multiplexedinputs as shown in the application circuits.FIGURE 10. WAVEFORM FOR GUARANTEED MINIMUM f B (MAX)AND f A (MAX) FOR FUNCTION = PERIOD ANDTIME INTERVAL7

<strong>ICM7226A</strong>, <strong>ICM7226B</strong>Table 1 shows the functions selected by each digit for theseinputs.Function InputTABLE 1. MULTIPLEXED INPUT FUNCTIONSINPUT FUNCTION DIGITFUNCTION INPUTPin 4RANGE INPUTPin 21CONTROL INPUTPin 1External DP INPUTPin 20FrequencyPeriodFrequency RatioTime IntervalUnit CounterOscillator Frequency0.01s/1 Cycle0.1s/10 CyclesThe six functions that can be selected are: Frequency,Period, Time Interval, Unit Counter, Frequency Ratio andOscillator Frequency.D1D8D2D5D4D3D1D21s/100 Cycles D310s/1K CyclesEnable External Range InputDisplay OffDisplay Test1MHz SelectExternal Oscillator EnableExternal Decimal PointEnableD4D5D4 andHoldD8D2D1D3Decimal point is output for same digitthat is connected to this input.The implementation of different functions is done by routingthe different signals to two counters, called “Main Counter”and “Reference Counter”. A simplified block diagram of thedevice for functions realization is shown in Figure 11. Table 2shows which signals will be routed to each counter in differentcases. The output of the Main Counter is the informationwhich goes to the display. The Reference Counter divides itsinput to 1, 10, 100 and 1000. One of these outputs will beselected through the range selector and drive the enableinput of the Main Counter. This means that the ReferenceCounter, along with its' associated blocks, directs the MainCounter to begin counting and determines the length of thecounting period. Note that Figure 11 does not show the completefunctional diagram (See the Functional Block Diagram).After the end of each counting period, the output ofthe Main Counter will be latched and displayed, then thecounter will be reset and a new measurement cycle willbegin. Any change in the FUNCTION INPUT will stop thepresent measurement without updating the display and theninitiate a new measurement. This prevents an erroneous firstreading after the FUNCTION INPUT is changed. In allcases, the 1-0 transitions are counted or timed.TABLE 2. INPUT ROUTINGFUNCTIONMAINCOUNTERCOUNTERFrequency (f A ) Input A 100Hz (Oscillator ³÷10 5 or 10 4 )Period (t A ) Oscillator Input ARatio (f A /f B ) Input A Input BTime Interval(A→B)Unit Counter(Count A)Osc. Freq.(f OSC )OscillatorInputAInput AInput BNotApplicableOscillator 100Hz (Oscillator ³÷10 5 or 10 4 )INTERNAL CONTROLINTERNAL CONTROL100HzINPUT AINPUT BINPUTSELECTORCLOCKREFERENCE COUNTER÷1 ÷10 ÷100 ÷1000INTERNAL CONTROLINTERNAL CONTROLRANGE SELECTORINTERNAL OREXTERNALOSCILLATORINPUT AINPUTSELECTORENABLECLOCKMAIN COUNTERFIGURE 11. SIMPLIFIED BLOCK DIAGRAM OF FUNCTIONS IMPLEMENTATION8

<strong>ICM7226A</strong>, <strong>ICM7226B</strong>Frequency - In this mode input A is counted by the MainCounter for a precise period of time. This time is determinedby the time base oscillator and the selected range. For the10MHz (or 1MHz) time base, the resolutions are 100Hz,10Hz, 1Hz and 0.1Hz. The decimal point on the display isset for kHz reading.Period - In this mode, the timebase oscillator is counted bythe Main Counter for the duration of 1, 10, 100 or 1000(range selected) periods of the signal at input A. A 10MHztimebase gives resolutions of 0.1µs to 0.0001µs for 1000periods averaging. Note that the maximum input frequencyfor period measurement is 2.5MHz.Frequency Ratio - In this mode, the input A is counted bythe Main Counter for the duration of 1, 10, 100 or 1000(range selected) periods of the signal at input B. The frequencyat input A should be higher than input B for meaningfulresult. The result in this case is unitless and its resolutioncan go up to 3 digits after decimal point.Time Interval - In this mode, the timebase oscillator is countedby the Main Counter for the duration of a 1-0 transition of inputA until a 1-0 transition of input B. This means input A starts thecounting and input B stops it. If other ranges, except 0.01s/1cycle are selected the sequence of input A and B transitionsmust happen 10, 100 or 1000 times until the display becomesupdated; note this when measuring long time intervals to giveenough time for measurement completion. The resolution inthis mode is the same as for period measurement. See theTime Interval Measurement section also.Unit Counter - In this mode, the Main Counter is alwaysenabled. The input A is counted by the Main Counter anddisplayed continuously.Oscillator Frequency - In this mode, the device makes afrequency measurement on its timebase. This is a self testmode for device functionality check. For 10MHz timebasethe display will show 10000.0, 10000.00, 10000.000 andOverflow in different ranges.Range InputThe RANGE INPUT selects whether the measurement period ismade for 1,10,100 or 1000 counts of the Reference Counter or itis controlled by EXT RANGE input. As it is shown in Table 1, thisgives different counting windows for frequency measurementand various cycles for other modes of measurement.In all functional modes except Unit Counter, any change inthe RANGE INPUT will stop the present measurement withoutupdating the display and then initiate a new measurement.This prevents an erroneous first reading after theRANGE INPUT is changed.Control InputUnlike the other multiplexed inputs, to which only one of thedigit outputs can be connected at a time, this input can betied to different digit lines to select combination of controls.In this case, isolation diodes must be used in digit lines toavoid crosstalk between them (see Figure 19). The directionof diodes depends on the device version, common anode orcommon cathode. For maximum noise immunity at this input,in addition to the 10K resistor which was mentioned before,a 39pF to 100pF capacitor should also be placed betweenthis input and the V DD or V SS (See Figure 19).Display Off - To disable the display drivers, it is necessary to tiethe D4 line to the CONTROL INPUT and have the HOLD inputat V DD . While in Display Off mode, the segments and digit driversare all off, leaving the display lines floating, so the displaycan be shared with other devices. In this mode, the oscillatorcontinues to run with a typical supply current of 1.5mA with a10MHz crystal, but no measurements are made and multiplexedinputs are inactive. A new measurement cycle will be initiatedwhen the HOLD input is switched to V SS .Display Test - Display will turn on with all the digits showing8s and all decimal points also on. The display will be blankedif Display Off is selected at the same time.1MHz Select - The 1MHz select mode allows use of a 1MHzcrystal with the same digit multiplex rate and time betweenmeasurement as with a 10MHz crystal. This is done by dividingthe oscillator frequency by 10 4 rather than 10 5 . The decimalpoint is also shifted one digit to the right in period andtime interval, since the least significant digit will be in µsincrement rather than 0.1µs increment.External Oscillator Enable - In this mode, the signal at EXTOSC INPUT is used as a timebase instead of the on-boardcrystal oscillator (built around the OSC INPUT, OSC OUTPUTinputs). This input can be used for an external stable temperaturecompensated crystal oscillator or for special measurementswith any external source. The on-board crystal oscillatorcontinues to work when the external oscillator is selected. Thisis necessary to avoid hang-up problems, and has no effect onthe chip's functional operation. If the on-board oscillator frequencyis less than 1MHz or only the external oscillator is used,THE OSC INPUT MUST BE CONNECTED TO THE EXT OSCINPUT providing the timebase has enough voltage swing forOSC INPUT (See Electrical Specifications). If the external timebaseis TTL level a pullup resistor must be used for OSCINPUT. The other way is to put a 22MΩ resistor between OSCINPUT and OSC OUTPUT and capacitively couple the EXTOSC INPUT to OSC INPUT. This will bias the OSC INPUT atits threshold and the drive voltage will need to be only 2V P-P .The external timebase frequency must be greater than 100kHzor the chip will reset itself to enable the on-board oscillator.External Decimal Point Enable - In this mode, the EX DPINPUT is enabled. A decimal point will be displayed for thedigit that its output line is connected to this input (EX DPINPUT). Digit 8 should not be used since it will override theoverflow output. Leading zero blanking is effective for thedigits to the left of selected decimal point.Hold InputExcept in the unit counter mode, when the HOLD input isat V DD , any measurement in progress (before STORE goeslow) is stopped, the main counter is reset and the chip isheld ready to initiate a new measurement as soon as HOLDgoes low. The latches which hold the main counter data arenot updated, so the last complete measurement is displayed.In unit counter mode when HOLD input is at V DD , thecounter is not stopped or reset, but the display is frozen atthat instantaneous value. When HOLD goes low the countcontinues from the new value in the new counter.9

<strong>ICM7226A</strong>, <strong>ICM7226B</strong>RST IN InputThe RST IN is provided to reset the Main Counter, stop anymeasurement in progress, and enable the display latches,resulting in the all zero display. It is suggested to have acapacitor at this input to V SS to prevent any hangup problemon power up. See application circuits.EXT RANGE InputThis input is provided to select ranges other than thoseprovided in the chip. In any mode of measurement the durationof measurement is determined by the EXT RANGE if this inputis enabled. This input is sampled at 10ms intervals by the100Hz reference derived from the timebase. Figure 12 showsthe relationship between this input, 100Hz reference signal andMEAS IN PROGRESS. EXT RANGE can change stateanywhere during the period of 100Hz reference by will besampled at the trailing edge of the period to start or stopmeasurement.REFERENCECOUNTERCLOCKMEASIN PROGRESSEXT RANGEINPUTt rFIGURE 12. EXTERNAL RANGE INPUT TO END OFMEASUREMENT IN PROGRESSThis input should not be used for short arbitrary ranges(because of its sampling period), it is provided for very longgating purposes. A way of using the ICM7226 for a shortarbitrary range is to feed the gating signal into the INPUT Band run the device in the Frequency Ratio mode. Note thatthe gating period will be from one positive edge until the nextpositive edge of INPUT B (0.01s/1 cycle range).MEAS IN PROGRESS, STORE, RST OUT OutputsThese outputs are provided for external system interfacing.MEAS IN PROGRESS stays low during measurements andgoes high for intervals between measurements. Figure 13shows the relationship between these outputs for intervalsbetween measurements. All these outputs can drive a lowpower Schottky TTL. The MEAS IN PROGRESS can driveone ECL load if the ECL device is powered from the samepower supply as the ICM7226.MEASIN PROGRESSSTORERESET OUT30ms TO40ms190ms TO 200ms40ms60msBCD OutputsThe BCD representation of each display digit is available atthe BCD outputs in a multiplexed fashion. See Table 3 for digitstruth table. The BCD output of each digit is available whenits corresponding digit output is activated. Note that the digitoutputs are multiplexed from D8 (MSD) to D1 (LSD). The positivegoing (<strong>ICM7226A</strong>, common anode) or the negative going(<strong>ICM7226B</strong>, common cathode) digit drive signals lag the BCDdata by 2µs to6µs. This starting edge of each digit drive signalshouldbeusedtoexternallylatchtheBCDdata.EachBCD output drives one low power Schottky TTL load. Leadingzero blanking has no effect on the BCD outputs.TABLE 3. TRUTH TABLE BCD OUTPUTS40msFIGURE 13. RESET OUT, STORE AND MEASUREMENT INPROGRESS OUTPUTS BETWEEN MEASUREMENTSNUMBERBCD 8PIN 7BCD 4PIN 6BCD 2PIN 17BCD 1PIN 180 0 0 0 01 0 0 0 12 0 0 1 03 0 0 1 14 0 1 0 05 0 1 0 16 0 1 1 07 0 1 1 18 1 0 0 09 1 0 0 1BUF OSC OUT OutputThe BUFFered OSCillator OUTput is provided for use of theon-board oscillator signal, without loading the oscillator itself.This output can drive one low power Schottky TTL load. Careshould be taken to minimize capacitive loading on this pin.Decimal Point PositionTable 4 shows the decimal point position for different modesof lCM7226 operation. Note that the digit 1 is the least significantdigit. Table is given for 10MHz timebase frequency.TABLE 4. DECIMAL POINT POSITIONSRANGE FREQUENCY PERIODFREQUENCYRATIOTIMEINTERVALUNITCOUNTEROSCILLATORFREQUENCY0.01s/1 Cycle D2 D2 D1 D2 D1 D20.1s/10 Cycle D3 D3 D2 D3 D1 D31s/100 Cycle D4 D4 D3 D4 D1 D410s/1K Cycle D5 D5 D4 D5 D1 D5External N/A N/A N/A N/A N/A N/A10

<strong>ICM7226A</strong>, <strong>ICM7226B</strong>Overflow IndicationWhen overflow happens in any measurement it will be indicatedon the decimal point of the digit 8. A separate LED indicator canbe used. Figure 14 shows how to connect this indicator.af bge cdLED overflow indicator connections: Overflow will beindicated on the decimal point output of digit 8.DEVICE CATHODE ANODE<strong>ICM7226A</strong> Decimal Point D8<strong>ICM7226B</strong> D8 Decimal PointFIGURE 14. SEGMENT IDENTIFICATION AND DISPLAY FONTTime Interval MeasurementWhen in the time interval mode and measuring a singleevent, the lCM7226A and lCM7226B must first be “primed”prior to measuring the event of interest. This is done by firstgenerating a negative going edge on Channel A followed by anegative going edge on Channel B to start the “measurementinterval”. The inputs are then primed ready for the measurement.Positive going edges on A and B, before or after thepriming, will be needed to restore the original condition.Priming can be easily accomplished using the circuit inFigure 15.V DDSIGNAL ASIGNAL BDP22INPUT AINPUT BWhen timing repetitive signals, it is not necessary to “prime”the lCM7226A and lCM7226B as the first alternating signalstates automatically prime the device. See Figure 1.During any time interval measurement cycle, the <strong>ICM7226A</strong>and lCM7226B requires 200ms following B going low toupdate all internal logic. A new measurement cycle will nottake place until completion of this internal update time.Oscillator ConsiderationsThe oscillator is a high gain complementary FET inverter. Anexternal resistor of 10MΩ or 22MΩ should be connectedbetween the oscillator input and output to provide biasing.The oscillator is designed to work with a parallel resonant10MHz quartz crystal with a static capacitance of 22pF anda series resistance of less than 35Ω. Among suitablecrystals is the 10MHz CTS KNIGHTS ISI-002.For a specific crystal and load capacitance, the required g Mcanbecalculatedasfollows:g M ω 2 ⎛C IN C OUT R S 1 C O⎞ 2=⎜ + ------- ⎟⎝ C L ⎠⎛ C INC OUT ⎞where C L= ⎜--------------------------------⎟⎝C IN+ C OUT ⎠C O = Crystal Static CapacitanceR S = Crystal Series ResistanceC IN = Input CapacitanceC OUT = Output Capacitanceω =2πfThe required g M should not exceed 50% of the g M specifiedfor the lCM7226 to insure reliable startup. The OSCillatorINPUT and OUTPUT pins each contribute about 4pF to C INand C OUT . For maximum stability of frequency, C IN andC OUT should be approximately twice the specified crystalstatic capacitance.In cases where non decade prescalers are used, it may bedesirable to use a crystal which is neither 10MHz or 1MHz.In that case both the multiplex rate and time betweenmeasurements will be different. The multiplex rate is:N.O.PRIME11N914100KV DD150K1 110K10.1µF10nFf OSCffor 10MHz mode andOSCf MUX= ------------------for the2 10 4f MUX= ------------------×2 × 10 32 × 10 61MHz mode. The time between measurements is ------------------ inf OSC2 × 10 5the 10MHz mode and ------------------ in the 1MHz mode.f OSCV SS V SS V SSDEVICETYPE1 CD4049B Inverting Buffer2 CD4070B Exclusive - ORFIGURE 15. PRIMING CIRCUIT, SIGNALS A AND B BOTH HIGHOR LOWFollowing the priming procedure (when in single event or 1cycle range) the device is ready to measure one (only) event.The buffered oscillator output should be used as an oscillatortest point or to drive additional logic; this output will drive onelow power Schottky TTL load. When the buffered oscillatoroutput is used to drive CMOS or the external oscillator input,a10kΩ resistor should be added from the buffered oscillatoroutput to V DD .The crystal and oscillator components should be located asclose to the chip as practical to minimize pickup from othersignals. Coupling from the EXTERNAL OSClLLATOR INPUTto the OSClLLATOR OUTPUT or INPUT can causeundesirable shifts in oscillator frequency.11

<strong>ICM7226A</strong>, <strong>ICM7226B</strong>Display ConsiderationsThe display is multiplexed at a 500Hz rate with a digit time of244µs. An interdigit blanking time of 6µs isusedtopreventdisplay ghosting (faint display of data from previous digitsuperimposed on the next digit). Leading zero blanking isprovided, which blanks the left hand zeroes after decimalpoint or any non zero digits. Digits to the right of the decimalpoint are always displayed. The leading zero blanking will bedisabled when the Main Counter overflows.The lCM7226A is designed to drive common anode LED displaysat peak current of 25mA/segment, using displays withV F = 1.8V at 25mA. The average DC current will be greaterthan 3mA under these conditions. The lCM7226B is designedto drive common cathode displays at peak current of15mA/segment using displays with V F =1.8Vat15mA.Resistorscan be added in series with the segment drivers to limitthe display current, if required. The Typical PerformanceCurves show the digit and segment currents as a function ofoutput voltage for common anode and common cathodedrivers.To increase the light output from the displays, V DD may beincreased to 6.0V. However, care should be taken to see thatmaximum power and current ratings are not exceeded.The SEGment and Digit outputs in both the <strong>ICM7226A</strong> and<strong>ICM7226B</strong> are not directly compatible with either TTL orMAXIMUM NUMBER OFSIGNIFICANT DIGITS02460.01s0.1s1s10s1CYCLE10 CYCLES10 210 3 CYCLESCYCLESFREQUENCY MEASUREPERIOD MEASUREf OSC =10MHz81 10 10 3 10 510 7FREQUENCY (Hz)FIGURE 16. MAXIMUM ACCURACY OF FREQUENCY ANDPERIOD MEASUREMENTS DUE TO LIMITATIONSOF QUANTIZATION ERRORSCMOS logic. Therefore, level shifting with discrete transistorsmay be required to use these outputs as logic signals.External latching should be down on the leading edge of thedigit signal.AccuracyIn a Universal Counter, crystal drift and quantization errorscause errors. In frequency, period and time intervalmodes, a signal derived from the oscillator is used in eitherthe Reference Counter or Main Counter, and in thesemodes, an error in the oscillator frequency will cause anidentical error in the measurement. For instance, an oscillatortemperature coefficient of 20ppm/ o C will cause a measurementerror of 20ppm/ o C.In addition, there is a quantization error inherent in any digitalmeasurement of ±1 count. Clearly this error is reduced bydisplaying more digits. In the frequency mode maximumaccuracy is obtained with high frequency inputs and inperiod mode maximum accuracy is obtained with low frequencyinputs. As can be seen in Figure 16. In time intervalmeasurements there can be an error of 1 count per interval.As a result there is the same inherent accuracy in all rangesas shown in Figure 17. In frequency ratio measurementcan be more accurately obtained by averaging over morecycles of INPUT B as shown in Figure 18.MAXIMUM NUMBER OFSIGNIFICANT DIGITS012345678110MAXIMUM TIME INTERVALFOR 10 INTERVALS10 2MAXIMUM TIME INTERVALFOR 10 3 INTERVALSMAXIMUM TIMEINTERVAL FOR10 2 INTERVALS10 3 10 4 10 5 10 6 10 7 10 8TIME INTERVAL (µs)FIGURE 17. MAXIMUM ACCURACY OF TIME INTERVALMEASUREMENT DUE TO LIMITATIONS OFQUANTIZATION ERRORS0MAXIMUM NUMBER OFSIGNIFICANT DIGITS123456RANGE1CYCLE10 CYCLES10 2 CYCLES10 3 CYCLES781 10 10 2 10 3 10 4 10 5 10 6 10 7 10 8f A /f BFIGURE 18. MAXIMUM ACCURACY FOR FREQUENCY RATIO MEASUREMENT DUE TO LIMITATION OF QUANTIZATION ERRORS12

<strong>ICM7226A</strong>, <strong>ICM7226B</strong>Test CircuitV DD =5.0VDISPLAYOFFDISPLAYTEST 1MHzEXTOSCEXTDPTESTFUNCTIONGENERATORFUNCTIONGENERATOR39pFINPUT ACONTROL INPUTEXT OSC INFUNCTIONGENERATORD4D8 D2 D1 D31N914sD5INPUT B124039V SS10kΩHOLDV DDMEAS IN PROGRESSFUNCTION10K STORED1BCD CD8BCD DD2DPD5eD4gD3adbcfBCD BBCD ARESET34567891011121314151617181920<strong>ICM7226A</strong>383736353433323130292827262524232221BUF OSC OUTV DDV DDRST OUTEXT RANGED1D2D3D4D5D6D7D830pFV DD22MΩV DD10MHzCRYSTAL39pF8V DD D1D2100kΩD3D4D5D1D2D356CRYSTAL SPECS. =F O 10.00MHzC O 22pFR S 35Ω6DENOTES BUSWITH 6CONDUCTORS100kΩD4868abcdefgDPD8OVERFLOWD5D6D7D88D8 D7 D6 D5 D4 D3 D2 D1DEVICE CATHODE ANODE<strong>ICM7226A</strong> DP D8<strong>ICM7226B</strong> D8 DPNOTE: Overflow will be indicated on the decimal point output of digit 8.FIGURE 19.13

<strong>ICM7226A</strong>, <strong>ICM7226B</strong>Typical ApplicationsThe ICM7226 has been designed as a complete stand aloneUniversal Counter, or used with prescalers and other circuitryin a variety of applications. Since INPUT A and INPUT B aredigital inputs, additional circuitry will be required in manyapplications, for input buffering, amplification, hysteresis, andlevel shifting to obtain the required digital voltages. For manyapplications a FET source follower can be used for input buffering,and an ECL 10116 line receiver can be used for amplificationand hysteresis to obtain high impedance input,sensitivity and bandwidth. However, cost and complexity ofthis circuitry can vary widely, depending upon the sensitivityand bandwidth required. When TTL prescalers or input buffersareused,apullupresistorstoV DD should be used to obtainoptimal voltage swing at INPUTS A and B. If prescalers aren’trequired, the ICM7226 can be used to implement a minimumcomponent Universal Counter as shown in Figure 20.For input frequencies up to 40MHz, the circuit shown inFigure 21 can be used to implement a frequency andperiod counter. To obtain the correct value when measuringfrequency and period, it is necessary to divide the 10MHzoscillator frequency down to 2.5MHz. In doing this the timebetween measurements is lengthened to 800ms and the displaymultiplex rate is decreased to 125Hz.If the input frequency is prescaled by ten, the oscillatorfrequency can remain at either 10MHz or 1MHz, but thedecimal point must be moved. Figure 22 shows use of a ÷10prescaler in frequency counter mode. Additional logic hasbeen added to enable the ICM7226 to count the inputdirectly in period mode for maximum accuracy.10kΩDISPLAYBLANKDISPLAYTESTEXT OSCENABLE39pFV DDAINV DD100kΩBIN124039HOLDD41N914sD8D110kΩ343837V+3D1D8D2D5D4D3RESET0.1µFD3D2D4D5D6D756789101112131415<strong>ICM7226B</strong>3635343332313029282726geadEXT OSC IND8 161718252423bcV DDD11922 f2021100kΩD2D3DPV+39pFV+22MΩV+10MHzCRYSTAL39pF (TYP)84TYPICALCRYSTALPARAMETERSC L 22pFR S 35Ω68D4abcdefgDPD8 D7 D6 D5 D4 D3 D2 D1D8OVERFLOWFIGURE 20. 10MHz UNIVERSAL COUNTER14

<strong>ICM7226A</strong>, <strong>ICM7226B</strong>V DDV DDEXT OSCENABLEBIND1DISPLAYOFFD4DDDISPLAYTESTV+PCPCV+1N914D8 3QQV+QQV+74LS743kΩV+PPQ DQ D÷2 CK ÷2 CKQQC C39pFV DDV DD74LS74V DDV DD3kΩV10kΩDDHOLD140100kΩPD Q239IC ÷210kΩ338CK1437 V DDCQ56363510MHzV DD734 V DDCRYSTALD183322MΩD393239pF39pF (TYP)D2 10<strong>ICM7226B</strong>31V DD V DDD4D5D6D7D81112131415161730292827262524DPgeadb81823 cD141922 f100kΩD22021D3RESETD40.1aµFD1D8D2PFR388D8 D7 D6 D5 D4 D3 D2 D1bcdAINV DDPD QIC ÷2CK2QCV DDV DD3kΩefgDPD8OVERFLOWFIGURE 21. 40MHz FREQUENCY, PERIOD COUNTER15

<strong>ICM7226A</strong>, <strong>ICM7226B</strong>INPUTV DDM1CP ECL11C90 QTTLCE MS74LS0010kΩDISPLAYOFFDISPLAYTESTEXTOSCEN1MHz39pF74LS00MSM1INPUT CP ECL11C90 QTTLCEV+ 10kΩV+ 10kΩV+ 10kΩV DDD1D8D2D4FPRUC10kΩDPegad12345678910111213<strong>ICM7226A</strong>40393837363534333231302928D1V DDD4 D8 D1 D2HOLD1N914s10D2D3V DD100kΩV DDEXT OSC IN39pFV DD22MΩV DD10MHzCRYSTAL39pF(TYP)88D3kΩb1427D4c1526D54S6f16171819202524232221D6D7D8V DDRANGED1D2D3D4D5520.1µF88abcdefgDP100kΩD8D8 D7 D6 D5 D4 D3 D2 D18OVERFLOWFIGURE 22. 100MHz MULTI-FUNCTION COUNTER16

<strong>ICM7226A</strong>, <strong>ICM7226B</strong>V DDINPUTM1CP ECL11C90 QTTLCE MSV DD39pF10kΩV DDDISPLAYOFFDISPLAYTEST10kΩ2N2222V DD3kΩD4D8D110kΩV DDFUNCTIONSWITCHOPEN FREQCLOSEDPERIODV DDFD1 INCONT 2CD4016D8 INCONT 2OUTOUT10kΩD1D3D2D4D5D6D7123456789101112131415<strong>ICM7226B</strong>403938373635343332313029282726DPgead100kΩV DDV DDHOLD39pFV DDV DD1N914s22MΩV DD10MHzCRYSTAL39pF(TYP)30.1µFN.O.RESETINPUTD816171819202524232221bcfV DD10kΩD1D2D4D38428D8 D7 D6 D5 D4 D3 D2 D1abcdefgDPD8OVERFLOWFIGURE 23. 100MHz FREQUENCY, PERIOD COUNTER17

<strong>ICM7226A</strong>, <strong>ICM7226B</strong>Figure 23 shows the use of a CD4016 analog multiplexer tomultiplex the digital outputs back to the FUNCTION Input.Since the CD4016 is a digitally controlled analog transmissiongate, no level shifting of the digit output is required. CD4051sor CD4052s could also be used to select the proper inputs forthe multiplexed input on the ICM7226 from 2-bit or 3-bit digitalinputs. These analog multiplexers may also be used in systemsin which the mode of operation is controlled by a microprocessorrather than directly from front panel switches. TTLmultiplexers such as the 74LS153 or 74LS251 may also beused, but some additional circuitry will be required to convertthe digit output to TTL compatible logic levels.The circuit shown in Figure 24 can be used in any of thecircuit applications shown to implement a single measurementmode of operation. This circuit uses the STORE outputto put the ICM7226 into a hold mode. The HOLD input canalso be used to reduce the time between measurements.The circuit shown in Figure 25 puts a short pulse into theHOLD input a short time after STORE goes low. A new measurementwill be initiated at the end of the pulse on theHOLD input. This circuit reduces the time between measurementsto about 40ms from 200ms; use of the circuit shown inFigure 25 on the circuit shown in Figure 21 will reduce thetime between measurements from 800ms to about 160ms.Using LCD DisplayFigure 26 shows the ICM7226 being interfaced to LCD displays,by using its BCD outputs and 8 digit lines to drive twoICM7211 display drivers.STOREOUTPUTS1V DD100kΩS3V DD100kΩHOLDINPUTV DDSWITCHS2100kΩV DDFUNCTIONSTOREOUTPUT100kΩ100pF100pF100kΩHOLDINPUTS1S2Open-Single Meas Mode EnabledClosed-Initiate New MeasurementHOLD SWITCHN.O.S3Closed-Hold InputFIGURE 24. SINGLE MEASUREMENT CIRCUIT FOR USE WITHICM7226FIGURE 25. CIRCUIT FOR REDUCING TIME BETWEENMEASUREMENTSefabgcdefabgcdefabgcdefabgcdefabgcdefabgcdefabgcdefabgcd+5V128 SEGMENT LINES 28 SEGMENT LINES5 5+5V1ICM7211ICM721135 31 32 33 3430 29 28 27 27 28 29 3031 32 33 34363522 23 24 2676171827 28 29 30D8 • • D5D8 • • D1<strong>ICM7226A</strong>FIGURE 26. 10MHz UNIVERSAL COUNTER SYSTEM WITH LCD DISPLAY18

<strong>ICM7226A</strong>, <strong>ICM7226B</strong>All Intersil products are manufactured, assembled and tested utilizing ISO9000 quality systems.Intersil Corporation’s quality certifications can be viewed at website www.intersil.com/design/quality/iso.asp.Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice.Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable.However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which mayresult from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.For information regarding Intersil Corporation and its products, see web site www.intersil.comSales Office HeadquartersNORTH AMERICAIntersil Corporation2401 Palm Bay Rd.Palm Bay, FL 32905TEL: (321) 724-7000FAX: (321) 724-7240EUROPEIntersil SAMercure Center100, Rue de la Fusee1130 Brussels, BelgiumTEL: (32) 2.724.2111FAX: (32) 2.724.22.05ASIAIntersil Ltd.8F-2, 96, Sec. 1, Chien-kuo North,Taipei, <strong>Taiwan</strong> 104Republic of ChinaTEL: 886-2-2515-8508FAX: 886-2-2515-836919