PIC16C55X, EPROM-Based 8-Bit CMOS MCU Data Sheet

PIC16C55X, EPROM-Based 8-Bit CMOS MCU Data Sheet

PIC16C55X, EPROM-Based 8-Bit CMOS MCU Data Sheet

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

<strong>PIC16C55X</strong>NOTES:DS40143C-page 4 Preliminary © 1998 Microchip Technology Inc.

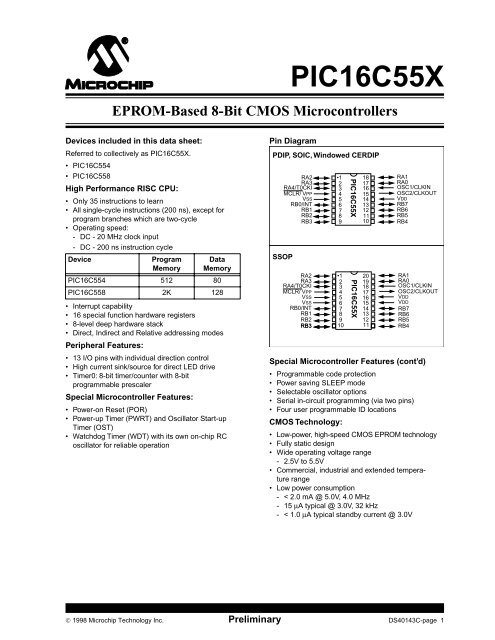

<strong>PIC16C55X</strong>1.0 GENERAL DESCRIPTIONThe <strong>PIC16C55X</strong> are 18 and 20-Pin <strong>EPROM</strong>-basedmembers of the versatile PIC16CXX family of low-cost,high-performance, <strong>CMOS</strong>, fully-static, 8-bitmicrocontrollers.All PICmicro ® microcontrollers employ an advancedRISC architecture. The <strong>PIC16C55X</strong> have enhancedcore features, eight-level deep stack, and multiple internaland external interrupt sources. The separateinstruction and data buses of the Harvard architectureallow a 14-bit wide instruction word with the separate8-bit wide data. The two-stage instruction pipelineallows all instructions to execute in a single-cycle,except for program branches (which require twocycles). A total of 35 instructions (reduced instructionset) are available. Additionally, a large register set givessome of the architectural innovations used to achieve avery high performance.<strong>PIC16C55X</strong> microcontrollers typically achieve a 2:1code compression and a 4:1 speed improvement overother 8-bit microcontrollers in their class.The PIC16C554 has 80 bytes of RAM. The PIC16C558has 128 bytes of RAM. Each device has 13 I/O pins andan 8-bit timer/counter with an 8-bit programmable prescaler.<strong>PIC16C55X</strong> devices have special features to reduceexternal components, thus reducing cost, enhancingsystem reliability and reducing power consumption.There are four oscillator options, of which the single pinRC oscillator provides a low-cost solution, the LPoscillator minimizes power consumption, XT is astandard crystal, and the HS is for High Speed crystals.The SLEEP (power-down) mode offers power saving.The user can wake up the chip from SLEEP throughseveral external and internal interrupts and reset.A highly reliable Watchdog Timer with its own on-chipRC oscillator provides protection against softwarelock-up.A UV-erasable CERDIP-packaged version is ideal forcode development while the cost-effective One-TimeProgrammable (OTP) version is suitable for productionin any volume.Table 1-1 shows the features of the <strong>PIC16C55X</strong>mid-range microcontroller families.A simplified block diagram of the <strong>PIC16C55X</strong> is shownin Figure 3-1.The <strong>PIC16C55X</strong> series fit perfectly in applicationsranging from motor control to low-power remote sensors.The <strong>EPROM</strong> technology makes customization ofapplication programs (detection levels, pulse generation,timers, etc.) extremely fast and convenient. Thesmall footprint packages make this microcontrollerseries perfect for all applications with space limitations.Low-cost, low-power, high-performance, ease of useand I/O flexibility make the <strong>PIC16C55X</strong> very versatile.1.1 Family and Upward CompatibilityThose users familiar with the PIC16C5X family ofmicrocontrollers will realize that this is an enhancedversion of the PIC16C5X architecture. Please refer toAppendix A for a detailed list of enhancements. Codewritten for PIC16C5X can be easily ported to<strong>PIC16C55X</strong> family of devices (Appendix B).The <strong>PIC16C55X</strong> family fills the niche for users wantingto migrate up from the PIC16C5X family and not needingvarious peripheral features of other members of thePIC16XX mid-range microcontroller family.1.2 Development SupportThe <strong>PIC16C55X</strong> family is supported by a full-featuredmacro assembler, a software simulator, an in-circuitemulator, a low-cost development programmer and afull-featured programmer. A “C” compiler and fuzzylogic support tools are also available.© 1998 Microchip Technology Inc. Preliminary DS40143C-page 5

<strong>PIC16C55X</strong>TABLE 1-1:<strong>PIC16C55X</strong> FAMILY OF DEVICESPIC16C554Clock Maximum Frequency of Operation (MHz) 20 20Memory<strong>EPROM</strong> Program Memory (x14 words) 512 2K<strong>Data</strong> Memory (bytes) 80 128Peripherals Timer Module(s) TMR0 TMR0FeaturesPIC16C558Interrupt Sources 3 3I/O Pins 13 13Voltage Range (Volts) 2.5-5.5 2.5-5.5Brown-out Reset — —Packages18-pin DIP,SOIC;20-pin SSOP18-pin DIP,SOIC;20-pin SSOPAll PICmicro ® Family devices have Power-on Reset, selectable Watchdog Timer, selectable code protect and highI/O current capability. All <strong>PIC16C55X</strong> Family devices use serial programming with clock pin RB6 and data pin RB7.DS40143C-page 6 Preliminary © 1998 Microchip Technology Inc.

<strong>PIC16C55X</strong>2.0 <strong>PIC16C55X</strong> DEVICE VARIETIESA variety of frequency ranges and packaging options areavailable. Depending on application and productionrequirements the proper device option can be selectedusing the information in the <strong>PIC16C55X</strong> ProductIdentification System section at the end of this datasheet. When placing orders, please use this page of thedata sheet to specify the correct part number.2.1 UV Erasable DevicesThe UV erasable version, offered in CERDIP packageis optimal for prototype development and pilotprograms. This version can be erased andreprogrammed to any of the oscillator modes.Microchip's PICSTART ® and PROMATE ®programmers both support programming of the<strong>PIC16C55X</strong>.2.2 One-Time-Programmable (OTP)DevicesThe availability of OTP devices is especially useful forcustomers who need the flexibility for frequent codeupdates and small volume applications. In addition tothe program memory, the configuration bits must alsobe programmed.2.3 Quick-Turnaround-Production (QTP)DevicesMicrochip offers a QTP Programming Service forfactory production orders. This service is madeavailable for users who choose not to program amedium to high quantity of units and whose code patternshave stabilized. The devices are identical to theOTP devices but with all <strong>EPROM</strong> locations and configurationoptions already programmed by the factory.Certain code and prototype verification proceduresapply before production shipments are available.Please contact your Microchip Technology sales officefor more details.2.4 SerializedQuick-Turnaround-Production(SQTP SM ) DevicesMicrochip offers a unique programming service wherea few user-defined locations in each device areprogrammed with different serial numbers. The serialnumbers may be random, pseudo-random orsequential.Serial programming allows each device to have aunique number which can serve as an entry-code,password or ID number.© 1998 Microchip Technology Inc. Preliminary DS40143C-page 7

<strong>PIC16C55X</strong>NOTES:DS40143C-page 8 Preliminary © 1998 Microchip Technology Inc.

<strong>PIC16C55X</strong>3.0 ARCHITECTURAL OVERVIEWThe high performance of the <strong>PIC16C55X</strong> family can beattributed to a number of architectural featurescommonly found in RISC microprocessors. To beginwith, the <strong>PIC16C55X</strong> uses a Harvard architecture, inwhich, program and data are accessed from separatememories using separate busses. This improvesbandwidth over traditional von Neumann architecturewhere program and data are fetched from the samememory. Separating program and data memory furtherallows instructions to be sized differently than 8-bitwide data words. Instruction opcodes are 14-bits widemaking it possible to have all single word instructions.A 14-bit wide program memory access bus fetches a14-bit instruction in a single cycle. A two-stage pipelineoverlaps fetch and execution of instructions.Consequently, all instructions (35) execute in a single-cycle(200 ns @ 20 MHz) except for programbranches. The table below lists the memory (E<strong>EPROM</strong>and ROM).DeviceProgramMemory<strong>Data</strong>MemoryPIC16C554 512 80PIC16C558 2K 128The PIC16C554 addresses 512 x 14 on-chip programmemory. The PIC16C558 addresses 2K x 14 programmemory. All program memory is internal.The <strong>PIC16C55X</strong> can directly or indirectly address itsregister files or data memory. All special functionregisters including the program counter are mappedinto the data memory. The <strong>PIC16C55X</strong> have anorthogonal (symmetrical) instruction set that makes itpossible to carry out any operation on any registerusing any addressing mode. This symmetrical natureand lack of ‘special optimal situations’ make programmingwith the <strong>PIC16C55X</strong> simple yet efficient. In addition,the learning curve is reduced significantly.The <strong>PIC16C55X</strong> devices contain an 8-bit ALU andworking register. The ALU is a general purposearithmetic unit. It performs arithmetic and Booleanfunctions between data in the working register and anyregister file.The ALU is 8-bits wide and capable of addition,subtraction, shift and logical operations. Unlessotherwise mentioned, arithmetic operations are two'scomplement in nature. In two-operand instructions,typically one operand is the working register(W register). The other operand is a file register or animmediate constant. In single operand instructions, theoperand is either the W register or a file register.The W register is an 8-bit working register used for ALUoperations. It is not an addressable register.Depending on the instruction executed, the ALU mayaffect the values of the Carry (C), Digit Carry (DC), andZero (Z) bits in the STATUS register. The C and DC bitsoperate as a Borrow and Digit Borrow out bit,respectively, in subtraction. See the SUBLW andSUBWF instructions for examples.A simplified block diagram is shown in Figure 3-1, witha description of the device pins in Table 3-1.© 1998 Microchip Technology Inc. Preliminary DS40143C-page 9

<strong>PIC16C55X</strong>FIGURE 3-1: BLOCK DIAGRAMDevicePIC16C554PIC16C558ProgramMemory512 x 142K x 14<strong>Data</strong> Memory(RAM)80 x 8128 x 8ProgramBus<strong>EPROM</strong>ProgramMemory512 x 14to2K x 1414Instruction reg13Program Counter8 Level Stack(13-bit)Direct Addr 7RAM Addr (1)<strong>Data</strong> BusRAMFileRegisters80 x 8 to128 x 88Addr MUX8FSR reg8IndirectAddrPORTAPORTBRA0RA1RA2RA3RA4/T0CKIRB0/INTRB7:RB18STATUS regPower-upTimer3MUXOSC1/CLKINOSC2/CLKOUTInstructionDecode &ControlTimingGenerationOscillatorStart-up TimerPower-onResetWatchdogTimer8ALUW regMCLRVDD, VSSTimer0Note 1: Higher order bits are from the status register.DS40143C-page 10 Preliminary © 1998 Microchip Technology Inc.

<strong>PIC16C55X</strong>FIGURE 4-3:DATA MEMORY MAP FORTHE PIC16C554FIGURE 4-4:DATA MEMORY MAP FORTHE PIC16C558FileAddressFileAddressFileAddressFileAddress00h01h02h03h04h05h06h07h08h09h0Ah0Bh0Ch0Dh0Eh0Fh10h11h12h13h14h15h16h17h18h19h1Ah1Bh1Ch1Dh1Eh1FhINDF (1)TMR0PCLSTATUSFSRPORTAPORTBPCLATHINTCONINDF (1)OPTIONPCLSTATUSFSRTRISATRISBPCLATHINTCONPCON80h81h82h83h84h85h86h87h88h89h8Ah8Bh8Ch8Dh8Eh8Fh90h91h92h93h94h95h96h97h98h99h9Ah9Bh9Ch9Dh9Eh9Fh00h01h02h03h04h05h06h07h08h09h0Ah0Bh0Ch0Dh0Eh0Fh10h11h12h13h14h15h16h17h18h19h1Ah1Bh1Ch1Dh1Eh1FhINDF (1)TMR0PCLSTATUSFSRPORTAPORTBPCLATHINTCONINDF (1)OPTIONPCLSTATUSFSRTRISATRISBPCLATHINTCONPCON80h81h82h83h84h85h86h87h88h89h8Ah8Bh8Ch8Dh8Eh8Fh90h91h92h93h94h95h96h97h98h99h9Ah9Bh9Ch9Dh9Eh9Fh20h6FhGeneralPurposeRegisterA0h20hGeneralPurposeRegisterGeneralPurposeRegisterA0hBFh70hC0h7FhBank 0 Bank 1FFh7FhBank 0 Bank 1FFhUnimplemented data memory locations, read as '0'.Note 1: Not a physical register.Unimplemented data memory locations, read as '0'.Note 1: Not a physical register.DS40143C-page 14 Preliminary © 1998 Microchip Technology Inc.

<strong>PIC16C55X</strong>4.2.2 SPECIAL FUNCTION REGISTERSThe Special Function Registers are registers used bythe CPU and peripheral functions for controlling thedesired operation of the device (Table 4-1). Theseregisters are static RAM.The special function registers can be classified into twosets (core and peripheral). The special function registersassociated with the “core” functions are describedin this section. Those related to the operation of theperipheral features are described in the section of thatperipheral feature.TABLE 4-1:SPECIAL REGISTERS FOR THE <strong>PIC16C55X</strong>Address Name <strong>Bit</strong> 7 <strong>Bit</strong> 6 <strong>Bit</strong> 5 <strong>Bit</strong> 4 <strong>Bit</strong> 3 <strong>Bit</strong> 2 <strong>Bit</strong> 1 <strong>Bit</strong> 0Value onPOR ResetValue onall otherresets (1)Bank 000h INDFAddressing this location uses contents of FSR to address data memory (not a physicalregister)xxxx xxxx xxxx xxxx01h TMR0 Timer0 Module’s Register xxxx xxxx uuuu uuuu02h PCL Program Counter's (PC) Least Significant Byte 0000 0000 0000 000003h STATUS IRP (2) RP1 (2) RP0 TO PD Z DC C 0001 1xxx 000q quuu04h FSR Indirect data memory address pointer xxxx xxxx uuuu uuuu05h PORTA — — — RA4 RA3 RA2 RA1 RA0 ---x xxxx ---u uuuu06h PORTB RB7 RB6 RB5 RB4 RB3 RB2 RB1 RB0 xxxx xxxx uuuu uuuu07h Unimplemented — —08h Unimplemented — —09h Unimplemented — —0Ah PCLATH — — — Write buffer for upper 5 bits of program counter ---0 0000 ---0 00000Bh INTCON GIE (3) T0IE INTE RBIE T0IF INTF RBIF 0000 000x 0000 000u0Ch Unimplemented — —0Dh-1Eh Unimplemented — —1Fh Unimplemented — —Bank 180h INDFAddressing this location uses contents of FSR to address data memory (not a physical xxxx xxxx xxxx xxxxregister)81h OPTION RBPU INTEDG T0CS T0SE PSA PS2 PS1 PS0 1111 1111 1111 111182h PCL Program Counter's (PC) Least Significant Byte 0000 0000 0000 000083h STATUS — — RP0 TO PD Z DC C 0001 1xxx 000q quuu84h FSR Indirect data memory address pointer xxxx xxxx uuuu uuuu85h TRISA — — — TRISA4 TRISA3 TRISA2 TRISA1 TRISA0 ---1 1111 ---1 111186h TRISB TRISB7 TRISB6 TRISB5 TRISB4 TRISB3 TRISB2 TRISB1 TRISB0 1111 1111 1111 111187h Unimplemented — —88h Unimplemented — —89h Unimplemented — —8Ah PCLATH — — — Write buffer for upper 5 bits of program counter ---0 0000 ---0 00008Bh INTCON GIE (3) T0IE INTE RBIE T0IF INTF RBIF 0000 000x 0000 000u8Ch Unimplemented — —8Dh Unimplemented — —8Eh PCON — — — — — — POR — ---- --0- ---- --u-8Fh-9Eh Unimplemented — —9Fh Unimplemented — —Legend: — = Unimplemented locations read as ‘0’, u = unchanged, x = unknown, q = value depends on condition,shaded = unimplementedNote 1: Other (non power-up) resets include MCLR reset and Watchdog Timer reset during normal operation.Note 2: IRP & RP1bits are reserved, always maintain these bits clear.Note 3: <strong>Bit</strong> 6 of INTCON register is reserved for future use. Always maintain this bit as clear.© 1998 Microchip Technology Inc. Preliminary DS40143C-page 15

<strong>PIC16C55X</strong>4.2.2.2 OPTION REGISTERThe OPTION register is a readable and writableregister which contains various control bits to configurethe TMR0/WDT prescaler, the external RB0/INTinterrupt, TMR0 and the weak pull-ups on PORTB.Note:To achieve a 1:1 prescaler assignment forTMR0, assign the prescaler to the WDT(PSA = 1).FIGURE 4-6: OPTION REGISTER (ADDRESS 81H)R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1RBPU INTEDG T0CS T0SE PSA PS2 PS1 PS0 R = Readable bitbit7bit0 W = Writable bit- n = Value at POR resetbit 7: RBPU: PORTB Pull-up Enable bit1 = PORTB pull-ups are disabled0 = PORTB pull-ups are enabled by individual port latch valuesbit 6: INTEDG: Interrupt Edge Select bit1 = Interrupt on rising edge of RB0/INT pin0 = Interrupt on falling edge of RB0/INT pinbit 5: T0CS: TMR0 Clock Source Select bit1 = Transition on RA4/T0CKI pin0 = Internal instruction cycle clock (CLKOUT)bit 4: T0SE: TMR0 Source Edge Select bit1 = Increment on high-to-low transition on RA4/T0CKI pin0 = Increment on low-to-high transition on RA4/T0CKI pinbit 3: PSA: Prescaler Assignment bit1 = Prescaler is assigned to the WDT0 = Prescaler is assigned to the Timer0 modulebit 2-0: PS2:PS0: Prescaler Rate Select bits<strong>Bit</strong> Value TMR0 Rate WDT Rate0000010100111001011101111 : 21 : 41 : 81 : 161 : 321 : 641 : 1281 : 2561 : 11 : 21 : 41 : 81 : 161 : 321 : 641 : 128© 1998 Microchip Technology Inc. Preliminary DS40143C-page 17

<strong>PIC16C55X</strong>4.2.2.3 INTCON REGISTERThe INTCON register is a readable and writableregister which contains the various enable and flag bitsfor all interrupt sources.Note:Interrupt flag bits get set when an interruptcondition occurs regardless of the state ofits corresponding enable bit or the globalenable bit, GIE (INTCON).FIGURE 4-7:INTCON REGISTER (ADDRESS 0BH OR 8BH)R/W-0 Reserved R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-xGIE — T0IE INTE RBIE T0IF INTF RBIF R = Readable bitbit7bit0 W = Writable bit- n = Value at POR reset- x = Unknown at POR resetbit 7: GIE: Global Interrupt Enable bit1 = Enables all un-masked interrupts0 = Disables all interruptsbit 6: — = Reserved for future use. Always maintain this bit clear.bit 5: T0IE: TMR0 Overflow Interrupt Enable bit1 = Enables the TMR0 interrupt0 = Disables the TMR0 interruptbit 4: INTE: RB0/INT External Interrupt Enable bit1 = Enables the RB0/INT external interrupt0 = Disables the RB0/INT external interruptbit 3: RBIE: RB Port Change Interrupt Enable bit1 = Enables the RB port change interrupt0 = Disables the RB port change interruptbit 2: T0IF: TMR0 Overflow Interrupt Flag bit1 = TMR0 register has overflowed (must be cleared in software)0 = TMR0 register did not overflowbit 1: INTF: RB0/INT External Interrupt Flag bit1 = The RB0/INT external interrupt occurred (must be cleared in software)0 = The RB0/INT external interrupt did not occurbit 0: RBIF: RB Port Change Interrupt Flag bit1 = When at least one of the RB7:RB4 pins changed state (must be cleared in software)0 = None of the RB7:RB4 pins have changed stateDS40143C-page 18 Preliminary © 1998 Microchip Technology Inc.

<strong>PIC16C55X</strong>4.2.2.4 PCON REGISTERThe PCON register contains flag bits to differentiatebetween a Power-on Reset, an external MCLR reset orWDT reset. See Section 7.3 and Section 7.4 fordetailed reset operation.FIGURE 4-8:PCON REGISTER (ADDRESS 8Eh)U-0 U-0 U-0 U-0 U-0 U-0 R/W-0 U-0— — — — — — POR — R = Readable bitbit7bit0 W = Writable bitU = Unimplemented bit,read as ‘0’- n = Value at POR resetbit 7-2: Unimplemented: Read as '0'bit 1: POR: Power-on Reset Status bit1 = No Power-on Reset occurred0 = Power-on Reset occurredbit 0: Unimplemented: Read as '0'© 1998 Microchip Technology Inc. Preliminary DS40143C-page 19

<strong>PIC16C55X</strong>4.3 PCL and PCLATHThe program counter (PC) is 13-bits wide. The low bytecomes from the PCL register, which is a readable andwritable register. The high bits (PC) are not directlyreadable or writable and come from PCLATH. On anyreset, the PC is cleared. Figure 4-9 shows the twosituations for the loading of the PC. The upper example inthe figure shows how the PC is loaded on a write to PCL(PCLATH → PCH). The lower example in Figure 4-9shows how the PC is loaded during a CALL or GOTOinstruction (PCLATH → PCH).FIGURE 4-9:PCPCPCHLOADING OF PC INDIFFERENT SITUATIONS12 8 7 05PCHPCLATHPCLATHPCLPCL12 11 10 8 708Instruction withPCL asDestinationALU resultGOTO, CALL4.3.2 STACKThe <strong>PIC16C55X</strong> family has an 8 level deep x 13-bitwide hardware stack (Figure 4-1 and Figure 4-2). Thestack space is not part of either program or data spaceand the stack pointer is not readable or writable. ThePC is PUSHed onto the stack when a CALL instructionis executed or an interrupt causes a branch. The stackis POPed in the event of a RETURN, RETLW or a RETFIEinstruction execution. PCLATH is not affected by aPUSH or POP operation.The stack operates as a circular buffer. This means thatafter the stack has been PUSHed eight times, the ninthpush overwrites the value that was stored from the firstpush. The tenth push overwrites the second push (andso on).Note 1: There are no STATUS bits to indicatestack overflow or stack underflowconditions.Note 2: There are no instructions mnemonicscalled PUSH or POP. These are actionsthat occur from the execution of theCALL, RETURN, RETLW and RETFIEinstructions, or vectoring to an interruptaddress.2PCLATH11Opcode PCLATH4.3.1 COMPUTED GOTOA computed GOTO is accomplished by adding anoffset to the program counter (ADDWF PCL). Whendoing a table read using a computed GOTO method,care should be exercised if the table location crosses aPCL memory boundary (each 256 byte block). Refer tothe application note “Implementing a Table Read"(AN556).DS40143C-page 20 Preliminary © 1998 Microchip Technology Inc.

<strong>PIC16C55X</strong>4.4 Indirect Addressing, INDF and FSRRegistersThe INDF register is not a physical register. Addressingthe INDF register will cause indirect addressing.Indirect addressing is possible by using the INDF register.Any instruction using the INDF register actuallyaccesses data pointed to by the file select register(FSR). Reading INDF itself indirectly will produce 00h.Writing to the INDF register indirectly results in ano-operation (although status bits may be affected). Aneffective 9-bit address is obtained by concatenating the8-bit FSR register and the IRP bit (STATUS), asshown in Figure 4-10. However, IRP is not used in the<strong>PIC16C55X</strong>.A simple program to clear RAM locations 20h-2Fhusing indirect addressing is shown in Example 4-1.EXAMPLE 4-1:INDIRECT ADDRESSINGmovlw 0x20 ;initialize pointermovwf FSR ;to RAMNEXT clrf INDF ;clear INDF registerincf FSR ;inc pointerbtfss FSR,4 ;all done?goto NEXT ;no clear next;yes continueCONTINUE:FIGURE 4-10: DIRECT/INDIRECT ADDRESSING <strong>PIC16C55X</strong>Direct AddressingIndirect Addressing(1) RP1 RP0 6 from opcode 0IRP (1) 7 FSR register 0bank selectlocation selectbank selectlocation select00h00 01 10 1100h<strong>Data</strong>Memorynot used7FhBank 0 Bank 1 Bank 2 Bank 37FhFor memory map detail see Figure 4-3 and Figure 4-4.Note 1: The RP1 and IRP bits are reserved, always maintain these bits clear.© 1998 Microchip Technology Inc. Preliminary DS40143C-page 21

<strong>PIC16C55X</strong>NOTES:DS40143C-page 22 Preliminary © 1998 Microchip Technology Inc.

<strong>PIC16C55X</strong>5.0 I/O PORTSThe <strong>PIC16C55X</strong> have two ports, PORTA and PORTB.5.1 PORTA and TRISA RegistersPORTA is a 5-bit wide latch. RA4 is a Schmitt Trigger inputand an open drain output. Port RA4 is multiplexed with theT0CKI clock input. All other RA port pins have SchmittTrigger input levels and full <strong>CMOS</strong> output drivers. All pinshave data direction bits (TRIS registers) which can configurethese pins as input or output.A '1' in the TRISA register puts the corresponding outputdriver in a hi- impedance mode. A '0' in the TRISA registerputs the contents of the output latch on the selected pin(s).Reading the PORTA register reads the status of the pins,whereas writing to it will write to the port latch. All writeoperations are read-modify-write operations. So a writeto a port implies that the port pins are first read, then thisvalue is modified and written to the port data latch.Note:On reset, the TRISA register is set to all inputs.FIGURE 5-2:<strong>Data</strong>busWRPORTAWRTRISARD PORTADCKBLOCK DIAGRAM OF RA4 PIN<strong>Data</strong> LatchDCKQQQQTRISA LatchRD TRISAQSchmittTriggerinputbufferDENNVSSVSSI/O pin (1)FIGURE 5-1:BLOCK DIAGRAM OFPORT PINS RATMR0 clock input<strong>Data</strong>busDQWRPortACKQVDDPVDD<strong>Data</strong> LatchDQNI/O pinWRTRISACK QTRIS LatchVSSSchmittTriggerinputbufferVSSRD TRISAQDENRD PORTA© 1998 Microchip Technology Inc. Preliminary DS40143C-page 23

<strong>PIC16C55X</strong>TABLE 5-1:PORTA FUNCTIONSName <strong>Bit</strong> #BufferTypeFunctionRA0 bit0 ST Bi-directional I/O port.RA1 bit1 ST Bi-directional I/O port.RA2 bit2 ST Bi-directional I/O port.RA3 bit3 ST Bi-directional I/O port.RA4/T0CKI bit4 ST Bi-directional I/O port or external clock input for TMR0. Output is opendrain type.Legend: ST = Schmitt Trigger inputTABLE 5-2:SUMMARY OF REGISTERS ASSOCIATED WITH PORTAAddress Name <strong>Bit</strong> 7 <strong>Bit</strong> 6 <strong>Bit</strong> 5 <strong>Bit</strong> 4 <strong>Bit</strong> 3 <strong>Bit</strong> 2 <strong>Bit</strong> 1 <strong>Bit</strong> 0Value onPORValue onAll Other Resets05h PORTA — — — RA4 RA3 RA2 RA1 RA0 ---x xxxx ---u uuuu85h TRISA — — — TRISA4 TRISA3 TRISA2 TRISA1 TRISA0 ---1 1111 ---1 1111Legend: — = Unimplemented locations, read as ‘0’x = unknownu = unchangedNote: Shaded bits are not used by PORTA.DS40143C-page 24 Preliminary © 1998 Microchip Technology Inc.

<strong>PIC16C55X</strong>5.2 PORTB and TRISB RegistersPORTB is an 8-bit wide bi-directional port. Thecorresponding data direction register is TRISB. A '1' inthe TRISB register puts the corresponding output driverin a high impedance mode. A '0' in the TRISB registerputs the contents of the output latch on the selectedpin(s).Reading PORTB register reads the status of the pins,whereas writing to it will write to the port latch. All writeoperations are read-modify-write operations. So a writeto a port implies that the port pins are first read, thenthis value is modified and written to the port data latch.Each of the PORTB pins has a weak internal pull-up(≈200 µA typical). A single control bit can turn on all thepull-ups. This is done by clearing the RBPU(OPTION) bit. The weak pull-up is automaticallyturned off when the port pin is configured as an output.The pull-ups are disabled on Power-on Reset.Four of PORTB’s pins, RB7:RB4, have an interrupt onchange feature. Only pins configured as inputs cancause this interrupt to occur (i.e., any RB7:RB4 pinconfigured as an output is excluded from the interrupton change comparison). The input pins (of RB7:RB4)are compared with the old value latched on the lastread of PORTB. The “mismatch” outputs of RB7:RB4are OR’ed together to generate the RBIF interrupt (flaglatched in INTCON). This interrupt can wake thedevice from SLEEP. The user, in the interrupt serviceroutine, can clear the interrupt in the following manner:a) Any read or write of PORTB. This will end themismatch condition.b) Clear flag bit RBIF.A mismatch condition will continue to set flag bit RBIF.Reading PORTB will end the mismatch condition, andallow flag bit RBIF to be cleared.This interrupt on mismatch feature, together withsoftware configurable pull-ups on these four pins alloweasy interface to a key pad and make it possible forwake-up on key-depression. (See AN552 in theMicrochip Embedded Control Handbook.)Note:If a change on the I/O pin should occur when theread operation is being executed (start of the Q2cycle), then the RBIF interrupt flag may notget set.The interrupt on change feature is recommended forwake-up on key depression operation and operationswhere PORTB is only used for the interrupt on changefeature. Polling of PORTB is not recommended whileusing the interrupt on change feature.FIGURE 5-3:BLOCK DIAGRAM OF RB7:RB4 PINSRBPU (1)VDD<strong>Data</strong> busWR PortBWR TRISB<strong>Data</strong> LatchD QCKTRIS LatchD QCK QVDDPNVSSPTTLInputBufferweakpull-upSTBufferVDDVSSI/OpinSet RBIFRD TRISBRD PortBLatchQ DENFrom otherQRB7:RB4 pinsRB7:RB6 in serial programming modeENDRD Port BNote 1: TRISB = 1 enables weak pull-up if RBPU = '0'(OPTION).© 1998 Microchip Technology Inc. Preliminary DS40143C-page 25

<strong>PIC16C55X</strong>FIGURE 5-4:BLOCK DIAGRAM OF RB3:RB0 PINSRBPU (1)VDD<strong>Data</strong> busWR PortBWR TRISB<strong>Data</strong> LatchD QCKTRIS LatchD QCK QVDDPNVSSPTTLInputBufferweakpull-upSTBufferVDDVSSI/OpinRD TRISBRD PortBLatchQ DENRB0:INTSTBufferRD Port BNote 1: TRISB = 1 enables weak pull-up if RBPU = '0'(OPTION).TABLE 5-3:PORTB FUNCTIONSName <strong>Bit</strong> # Buffer Type FunctionRB0/INT bit0 TTL/ST (1) Input/output or external interrupt input. Internal software programmableweak pull-up.RB1 bit1 TTL Input/output pin. Internal software programmable weak pull-up.RB2 bit2 TTL Input/output pin. Internal software programmable weak pull-up.RB3 bit3 TTL Input/output pin. Internal software programmable weak pull-up.RB4 bit4 TTL Input/output pin (with interrupt on change). Internal softwareprogrammable weak pull-up.RB5 bit5 TTL Input/output pin (with interrupt on change). Internal softwareprogrammable weak pull-up.RB6 bit6 TTL/ST (2) Input/output pin (with interrupt on change). Internal softwareprogrammable weak pull-up. Serial programming clock pin.RB7 bit7 TTL/ST (2) Input/output pin (with interrupt on change). Internal softwareprogrammable weak pull-up. Serial programming data pin.Legend: ST = Schmitt Trigger, TTL = TTL inputNote 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.Note 2: This buffer is a Schmitt Trigger input when used in serial programming mode.TABLE 5-4:SUMMARY OF REGISTERS ASSOCIATED WITH PORTBAddress Name <strong>Bit</strong> 7 <strong>Bit</strong> 6 <strong>Bit</strong> 5 <strong>Bit</strong> 4 <strong>Bit</strong> 3 <strong>Bit</strong> 2 <strong>Bit</strong> 1 <strong>Bit</strong> 0Value onPORValue onAll Other Rests06h PORTB RB7 RB6 RB5 RB4 RB3 RB2 RB1 RB0 xxxx xxxx uuuu uuuu86h TRISB TRISB7 TRISB6 TRISB5 TRISB4 TRISB3 TRISB2 TRISB1 TRISB0 1111 1111 1111 111181h OPTION RBPU INTEDG T0CS T0SE PSA PS2 PS1 PS0 1111 1111 1111 1111Legend:Note:x = unknown, u = unchangedShaded bits are not used by PORTB.DS40143C-page 26 Preliminary © 1998 Microchip Technology Inc.

<strong>PIC16C55X</strong>5.3 I/O Programming Considerations5.3.1 BI-DIRECTIONAL I/O PORTSAny instruction which writes, operates internally as aread followed by a write operation. The BCF and BSFinstructions, for example, read the register into theCPU, execute the bit operation and write the result backto the register. Caution must be used when theseinstructions are applied to a port with both inputs andoutputs defined. For example, a BSF operation on bit5of PORTB will cause all eight bits of PORTB to be readinto the CPU. Then the BSF operation takes place onbit5 and PORTB is written to the output latches. Ifanother bit of PORTB is used as a bidirectional I/O pin(e.g., bit0) and it is defined as an input at this time, theinput signal present on the pin itself would be read intothe CPU and re-written to the data latch of thisparticular pin, overwriting the previous content. As longas the pin stays in the input mode, no problem occurs.However, if bit0 is switched into output mode later on,the content of the data latch may now be unknown.Reading the port register, reads the values of the portpins. Writing to the port register writes the value to theport latch. When using read modify write instructions(ex. BCF, BSF, etc.) on a port, the value of the port pinsis read, the desired operation is done to this value, andthis value is then written to the port latch.Example 5-1 shows the effect of two sequentialread-modify-write instructions (ex., BCF, BSF, etc.) onan I/O port.A pin actively outputting a Low or High should not bedriven from external devices at the same time in orderto change the level on this pin (“wired-or”, “wired-and”).The resulting high output currents may damagethe chip.EXAMPLE 5-1: READ-MODIFY-WRITEINSTRUCTIONS ON ANI/O PORT; Initial PORT settings: PORTB Inputs;; PORTB Outputs; PORTB have external pull-up and are not; connected to other circuitry;; PORT latch PORT pins; ---------- ----------BCF PORTB, 7 ; 01pp pppp 11pp ppppBCF PORTB, 6 ; 10pp pppp 11pp ppppBSF STATUS,RP0 ;BCF TRISB, 7 ; 10pp pppp 11pp ppppBCF TRISB, 6 ; 10pp pppp 10pp pppp;; Note that the user may have expected the pin; values to be 00pp pppp. The 2nd BCF caused; RB7 to be latched as the pin value (High).5.3.2 SUCCESSIVE OPERATIONS ON I/O PORTSThe actual write to an I/O port happens at the end of aninstruction cycle, whereas for reading, the data must bevalid at the beginning of the instruction cycle(Figure 5-5). Therefore, care must be exercised if awrite followed by a read operation is carried out on thesame I/O port. The sequence of instructions should besuch to allow the pin voltage to stabilize (loaddependent) before the next instruction which causesthat file to be read into the CPU is executed. Otherwise,the previous state of that pin may be read into the CPUrather than the new state. When in doubt, it is better toseparate these instructions with an NOP or anotherinstruction not accessing this I/O port.FIGURE 5-5:SUCCESSIVE I/O OPERATIONPCInstructionfetchedRB7:RB0Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4PC PC + 1 PC + 2 PC + 3MOVWF PORTBWrite toPORTBMOVF PORTB, WRead PORTBNOPNOPTPDExecuteMOVWFPORTBPort pinsampled hereExecuteMOVFPORTB, WExecuteNOPNote:This example shows write to PORTBfollowed by a read from PORTB.Note that:data setup time = (0.25 TCY - TPD)where TCY = instruction cycle andTPD = propagation delay of Q1 cycleto output valid.Therefore, at higher clock frequencies,a write followed by a read may beproblematic.© 1998 Microchip Technology Inc. Preliminary DS40143C-page 27

<strong>PIC16C55X</strong>NOTES:DS40143C-page 28 Preliminary © 1998 Microchip Technology Inc.

<strong>PIC16C55X</strong>6.0 TIMER0 MODULEThe Timer0 module timer/counter has the followingfeatures:• 8-bit timer/counter• Readable and writable• 8-bit software programmable prescaler• Internal or external clock select• Interrupt on overflow from FFh to 00h• Edge select for external clockFigure 6-1 is a simplified block diagram of the Timer0module.Timer mode is selected by clearing the T0CS bit(OPTION). In timer mode, the TMR0 will incrementevery instruction cycle (without prescaler). If Timer0 iswritten, the increment is inhibited for the following twocycles (Figure 6-2 and Figure 6-3). The user can workaround this by writing an adjusted value to TMR0.Counter mode is selected by setting the T0CS bit. Inthis mode Timer0 will increment either on every risingor falling edge of pin RA4/T0CKI. The incrementingedge is determined by the source edge (T0SE) controlbit (OPTION). Clearing the T0SE bit selects therising edge. Restrictions on the external clock input arediscussed in detail in Section 6.2.The prescaler is shared between the Timer0 moduleand the WatchdogTimer. The prescaler assignment iscontrolled in software by the control bit PSA(OPTION). Clearing the PSA bit will assign theprescaler to Timer0. The prescaler is not readable orwritable. When the prescaler is assigned to the Timer0module, prescale value of 1:2, 1:4, ..., 1:256 areselectable. Section 6.3 details the operation of theprescaler.6.1 TIMER0 InterruptTimer0 interrupt is generated when the TMR0 registertimer/counter overflows from FFh to 00h. This overflowsets the T0IF bit. The interrupt can be masked byclearing the T0IE bit (INTCON). The T0IF bit(INTCON) must be cleared in software by theTimer0 module interrupt service routine beforere-enabling this interrupt. The Timer0 interrupt cannotwake the processor from SLEEP since the timer is shutoff during SLEEP. See Figure 6-4 for Timer0 interrupttiming.FIGURE 6-1:TIMER0 BLOCK DIAGRAMRA4/T0CKI FOSC/4pinT0SE01ProgrammablePrescaler10PSoutSync withInternalclocks(2 Tcy delay)PSout<strong>Data</strong> busTMR08T0CSPS2:PS0PSASet Flag bit T0IFon OverflowNote 1: <strong>Bit</strong>s, T0SE, T0CS, PS2, PS1, PS0 and PSA are located in the OPTION register.2: The prescaler is shared with Watchdog Timer (Figure 6-6)FIGURE 6-2:TIMER0 (TMR0) TIMING: INTERNAL CLOCK/NO PRESCALERPC(ProgramCounter)InstructionFetchQ1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4PC-1PC PC+1 PC+2 PC+3 PC+4 PC+5 PC+6MOVWF TMR0 MOVF TMR0,W MOVF TMR0,W MOVF TMR0,W MOVF TMR0,W MOVF TMR0,WTMR0T0 T0+1 T0+2 NT0 NT0 NT0 NT0+1 NT0+2 T0InstructionExecutedWrite TMR0executedRead TMR0reads NT0Read TMR0reads NT0Read TMR0reads NT0Read TMR0reads NT0 + 1Read TMR0reads NT0 + 2© 1998 Microchip Technology Inc. Preliminary DS40143C-page 29

<strong>PIC16C55X</strong>FIGURE 6-3: TIMER0 TIMING: INTERNAL CLOCK/PRESCALE 1:2PC(ProgramCounter)InstructionFetchQ1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4PC-1PC PC+1 PC+2 PC+3 PC+4 PC+5 PC+6MOVWF TMR0 MOVF TMR0,W MOVF TMR0,W MOVF TMR0,W MOVF TMR0,W MOVF TMR0,WTMR0T0T0+1 NT0NT0+1InstructionExecuteWrite TMR0executedRead TMR0reads NT0Read TMR0reads NT0Read TMR0reads NT0Read TMR0reads NT0Read TMR0reads NT0 + 1FIGURE 6-4:TIMER0 INTERRUPT TIMINGQ1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4OSC1CLKOUT(3)TMR0 timerT0IF bit(INTCON)FEh1 1FFh 00h 01h 02hGIE bit(INTCON)INSTRUCTION FLOWPCInterrupt Latency TimePC PC +1 PC +1 0004h 0005hInstructionfetchedInst (PC)Inst (PC+1)Inst (0004h)Inst (0005h)InstructionexecutedInst (PC-1)Inst (PC)Dummy cycleDummy cycleInst (0004h)Note 1: T0IF interrupt flag is sampled here (every Q1).2: Interrupt latency = 4Tcy, where Tcy = instruction cycle time.3: CLKOUT is available only in RC oscillator mode.DS40143C-page 30 Preliminary © 1998 Microchip Technology Inc.

<strong>PIC16C55X</strong>6.2 Using Timer0 with External ClockWhen an external clock input is used for Timer0, it mustmeet certain requirements. The external clockrequirement is due to internal phase clock (TOSC)synchronization. Also, there is a delay in the actualincrementing of Timer0 after synchronization.6.2.1 EXTERNAL CLOCK SYNCHRONIZATIONWhen no prescaler is used, the external clock input isthe same as the prescaler output. The synchronizationof T0CKI with the internal phase clocks isaccomplished by sampling the prescaler output on theQ2 and Q4 cycles of the internal phase clocks(Figure 6-5). Therefore, it is necessary for T0CKI to behigh for at least 2TOSC (and a small RC delay of 20 ns)and low for at least 2TOSC (and a small RC delay of20 ns). Refer to the electrical specification of thedesired device.When a prescaler is used, the external clock input isdivided by the asynchronous ripple-counter typeprescaler so that the prescaler output is symmetrical.For the external clock to meet the samplingrequirement, the ripple-counter must be taken intoaccount. Therefore, it is necessary for T0CKI to have aperiod of at least 4TOSC (and a small RC delay of40 ns) divided by the prescaler value. The onlyrequirement on T0CKI high and low time is that they donot violate the minimum pulse width requirement of10 ns. Refer to parameters 40, 41 and 42 in theelectrical specification of the desired device.6.2.2 TIMER0 INCREMENT DELAYSince the prescaler output is synchronized with theinternal clocks, there is a small delay from the time theexternal clock edge occurs to the time the TMR0 isactually incremented. Figure 6-5 shows the delay fromthe external clock edge to the timer incrementing.FIGURE 6-5:TIMER0 TIMING WITH EXTERNAL CLOCKExternal Clock Input orPrescaler output (2)External Clock/PrescalerOutput after samplingIncrement Timer0 (Q4)Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4Small pulsemisses sampling(3)(1)Timer0 T0 T0 + 1 T0 + 2Note 1: Delay from clock input change to Timer0 increment is 3Tosc to 7Tosc. (Duration of Q = Tosc).Therefore, the error in measuring the interval between two edges on Timer0 input = ±4Tosc max.2: External clock if no prescaler selected, Prescaler output otherwise.3: The arrows indicate the points in time where sampling occurs.© 1998 Microchip Technology Inc. Preliminary DS40143C-page 31

<strong>PIC16C55X</strong>6.3 PrescalerAn 8-bit counter is available as a prescaler for theTimer0 module, or as a postscaler for the WatchdogTimer, respectively (Figure 6-6). For simplicity, thiscounter is being referred to as “prescaler” throughoutthis data sheet. Note that there is only one prescaleravailable which is mutually exclusive between theTimer0 module and the Watchdog Timer. Thus, aprescaler assignment for the Timer0 module meansthat there is no prescaler for the Watchdog Timer, andvice-versa.The PSA and PS2:PS0 bits (OPTION) determinethe prescaler assignment and prescale ratio.When assigned to the Timer0 module, all instructionswriting to the TMR0 register (e.g., CLRF 1, MOVWF 1,BSF 1,x....etc.) will clear the prescaler. Whenassigned to WDT, a CLRWDT instruction will clear theprescaler along with the Watchdog Timer. Theprescaler is not readable or writable.FIGURE 6-6:BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALERCLKOUT (=Fosc/4)<strong>Data</strong> BusT0CKIpin0MU1X1 0MUXSYNC2Tcy8TMR0 regT0SET0CSPSASet flag bit T0IFon OverflowWatchdogTimer01MUX8-bit Prescaler8PSA8-to-1MUXPS0 - PS2WDT Enable bit0 1M U XPSAWDTTime-outNote: T0SE, T0CS, PSA, PS0-PS2 are bits in the OPTION register.DS40143C-page 32 Preliminary © 1998 Microchip Technology Inc.

<strong>PIC16C55X</strong>6.3.1 SWITCHING PRESCALER ASSIGNMENTThe prescaler assignment is fully under softwarecontrol (i.e., it can be changed “on the fly” duringprogram execution). To avoid an unintended deviceRESET, the following instruction sequence(Example 6-1) must be executed when changing theprescaler assignment from Timer0 to WDT. Lines 5-7are required only if the desired postscaler rate is 1:1(PS = 000) or 1:2 (PS = 001).EXAMPLE 6-1:CHANGING PRESCALER(TIMER0→WDT)1.BCF STATUS, RP0 ;Skip if already in; Bank 02.CLRWDT;Clear WDT3.CLRF TMR0 ;Clear TMR0 & Prescaler4.BSF STATUS, RP0 ;Bank 15.MOVLW '00101111’b; ;These 3 lines (5, 6, 7)6.MOVWF OPTION ; are required only if; desired PS are7.CLRWDT ; 000 or 0018.MOVLW '00101xxx’b ;Set Postscaler to9.MOVWF OPTION ; desired WDT rate10.BCF STATUS, RP0 ;Return to Bank 0To change prescaler from the WDT to the TMR0module use the sequence shown in Example 6-2. Thisprecaution must be taken even if the WDT is disabled.EXAMPLE 6-2:CHANGING PRESCALER(WDT→TIMER0)CLRWDT;Clear WDT and;prescalerBSF STATUS, RP0MOVLW b'xxxx0xxx' ;Select TMR0, new;prescale value and;clock sourceMOVWF OPTIONBCF STATUS, RP0TABLE 6-1:REGISTERS ASSOCIATED WITH TIMER0Address Name <strong>Bit</strong> 7 <strong>Bit</strong> 6 <strong>Bit</strong> 5 <strong>Bit</strong> 4 <strong>Bit</strong> 3 <strong>Bit</strong> 2 <strong>Bit</strong> 1 <strong>Bit</strong> 0Value onPORValue onAll Other Resets01h TMR0 Timer0 module’s register xxxx xxxx uuuu uuuu0Bh/8Bh INTCON GIE + T0IE INTE RBIE T0IF INTF RBIF 0000 000x 0000 000x81h OPTION RBPU INTEDG T0CS T0SE PSA PS2 PS1 PS0 1111 1111 1111 111185h TRISA — — — TRISA4 TRISA3 TRISA2 TRISA1 TRISA0 ---1 1111 ---1 1111Legend: — = Unimplemented locations, read as ‘0’.+ = Reserved for future use.Note: Shaded bits are not used by TMR0 module.© 1998 Microchip Technology Inc. Preliminary DS40143C-page 33

<strong>PIC16C55X</strong>NOTES:DS40143C-page 34 Preliminary © 1998 Microchip Technology Inc.

<strong>PIC16C55X</strong>7.0 SPECIAL FEATURES OF THECPUWhat sets a microcontroller apart from otherprocessors are special circuits to deal with the needs ofreal time applications. The <strong>PIC16C55X</strong> family has ahost of such features intended to maximize systemreliability, minimize cost through elimination of externalcomponents, provide power saving operating modesand offer code protection.These are:1. OSC selection2. ResetPower-on Reset (POR)Power-up Timer (PWRT)Oscillator Start-Up Timer (OST)3. Interrupts4. Watchdog Timer (WDT)5. SLEEP6. Code protection7. ID Locations8. In-circuit serial programmingThe <strong>PIC16C55X</strong> has a Watchdog Timer which iscontrolled by configuration bits. It runs off its own RCoscillator for added reliability. There are two timers thatoffer necessary delays on power-up. One is theOscillator Start-up Timer (OST), intended to keep thechip in reset until the crystal oscillator is stable. Theother is the Power-up Timer (PWRT), which provides afixed delay of 72 ms (nominal) on power-up only,designed to keep the part in reset while the powersupply stabilizes. With these two functions on-chip,most applications need no external reset circuitry.The SLEEP mode is designed to offer a very lowcurrent power-down mode. The user can wake-up fromSLEEP through external reset, Watchdog Timerwake-up or through an interrupt. Several oscillatoroptions are also made available to allow the part to fitthe application. The RC oscillator option saves systemcost while the LP crystal option saves power. A set ofconfiguration bits are used to select various options.© 1998 Microchip Technology Inc. Preliminary DS40143C-page 35

<strong>PIC16C55X</strong>7.1 Configuration <strong>Bit</strong>sThe configuration bits can be programmed (read as '0')or left unprogrammed (read as '1') to select variousdevice configurations. These bits are mapped inprogram memory location 2007h.The user will note that address 2007h is beyondthe user program memory space. In fact, it belongsto the special test/configuration memory space(2000h – 3FFFh), which can be accessed only duringprogramming.FIGURE 7-1:CONFIGURATION WORDCP1 CP0 1 CP1 CP0 1 CP1 CP0 1 — Reserved CP1 CP0 1 PWRTE WDTE F0SC1 F0SC0 CONFIG Addressbit13bit0 REGISTER: 2007hbit 13-8 CP: Code protection bits (1)5-4: 11 = Program Memory code protection off10 = 0400h - 07FFh code protected01 = 0200h - 07FFh code protected11 = 0000h - 07FFh code protectedbit 7: Unimplemented: Read as '1'bit 6: Reserved: Do not usebit 3:bit 2:bit 1-0:PWRTE: Power-up Timer Enable bit1 = PWRT disabled0 = PWRT enabledWDTE: Watchdog Timer Enable bit1 = WDT enabled0 = WDT disabledFOSC1:FOSC0: Oscillator Selection bits11 = RC oscillator10 = HS oscillator01 = XT oscillator00 = LP oscillatorNote 1: All of the CP1:CP0 pairs have to be given the same value to enable the code protection scheme listed.DS40143C-page 36 Preliminary © 1998 Microchip Technology Inc.

<strong>PIC16C55X</strong>7.2 Oscillator Configurations7.2.1 OSCILLATOR TYPESThe <strong>PIC16C55X</strong> can be operated in four differentoscillator options. The user can program twoconfiguration bits (FOSC1 and FOSC0) to select one ofthese four modes:• LP Low Power Crystal• XT Crystal/Resonator• HS High Speed Crystal/Resonator• RC Resistor/Capacitor7.2.2 CRYSTAL OSCILLATOR / CERAMICRESONATORSIn XT, LP or HS modes a crystal or ceramic resonatoris connected to the OSC1 and OSC2 pins to establishoscillation (Figure 7-2). The <strong>PIC16C55X</strong> oscillatordesign requires the use of a parallel cut crystal. Use ofa series cut crystal may give a frequency out of thecrystal manufacturers specifications. When in XT, LP orHS modes, the device can have an external clocksource to drive the OSC1 pin (Figure 7-3).TABLE 7-1:Ranges Characterized:CAPACITOR SELECTIONFOR CERAMIC RESONATORS(PRELIMINARY)Mode Freq OSC1(C1) OSC2(C2)XTHSTABLE 7-2:455 kHz2.0 MHz4.0 MHz8.0 MHz16.0 MHz22 - 100 pF15 - 68 pF15 - 68 pF10 - 68 pF10 - 22 pF22 - 100 pF15 - 68 pF15 - 68 pF10 - 68 pF10 - 22 pFHigher capacitance increases the stability of the oscillatorbut also increases the start-up time. These values are fordesign guidance only. Since each resonator has its owncharacteristics, the user should consult with the resonatormanufacturer for appropriate values of external components.CAPACITOR SELECTIONFOR CRYSTAL OSCILLATOR(PRELIMINARY)Mode Freq OSC1(C1) OSC2(C2)FIGURE 7-2:CRYSTAL OPERATION(OR CERAMIC RESONATOR)(HS, XT OR LP OSCCONFIGURATION)LPXT32 kHz200 kHz100 kHz2 MHz4 MHz68 - 100 pF15 - 30 pF68 - 150 pF15 - 30 pF15 - 30 pF68 - 100 pF15 - 30 pF150 - 200 pF15 - 30 pF15 - 30 pFC1C2See Table 7-1 and Table 7-2 for recommendedvalues of C1 and C2.Note:XTALRSsee NoteOSC1OSC2RFTo internal logicSLEEP<strong>PIC16C55X</strong>A series resistor may be required forAT strip cut crystals.HS8 MHz10 MHz20 MHz15 - 30 pF15 - 30 pF15 - 30 pF15 - 30 pF15 - 30 pF15 - 30 pFHigher capacitance increases the stability of the oscillatorbut also increases the start-up time. These values are fordesign guidance only. Rs may be required in HS mode aswell as XT mode to avoid overdriving crystals with low drivelevel specification. Since each crystal has its owncharacteristics, the user should consult with the crystalmanufacturer for appropriate values of external components.FIGURE 7-3:EXTERNAL CLOCK INPUTOPERATION (HS, XT OR LPOSC CONFIGURATION)Clock fromext. systemOpenOSC1<strong>PIC16C55X</strong>OSC2© 1998 Microchip Technology Inc. Preliminary DS40143C-page 37

<strong>PIC16C55X</strong>7.2.3 EXTERNAL CRYSTAL OSCILLATORCIRCUITEither a pre-packaged oscillator can be used or a simpleoscillator circuit with TTL gates can be built.Prepackaged oscillators provide a wide operatingrange and better stability. A well-designed crystaloscillator will provide good performance with TTLgates. Two types of crystal oscillator circuits can beused; one with series resonance, or one with parallelresonance.Figure 7-4 shows implementation of a parallel resonantoscillator circuit. The circuit is designed to use thefundamental frequency of the crystal. The 74AS04inverter performs the 180° phase shift that a paralleloscillator requires. The 4.7 kΩ resistor provides thenegative feedback for stability. The 10 kΩpotentiometers bias the 74AS04 in the linear region.This could be used for external oscillator designs.FIGURE 7-4:+5V10k4.7kEXTERNAL PARALLELRESONANT CRYSTALOSCILLATOR CIRCUIT74AS04XTAL10k74AS04To otherDevices<strong>PIC16C55X</strong>CLKIN7.2.4 RC OSCILLATORFor timing insensitive applications the “RC” deviceoption offers additional cost savings. The RC oscillatorfrequency is a function of the supply voltage, theresistor (Rext) and capacitor (Cext) values, and theoperating temperature. In addition to this, the oscillatorfrequency will vary from unit to unit due to normalprocess parameter variation. Furthermore, thedifference in lead frame capacitance between packagetypes will also affect the oscillation frequency,especially for low Cext values. The user also needs totake into account variation due to tolerance of externalR and C components used. Figure 7-6 shows how theR/C combination is connected to the <strong>PIC16C55X</strong>. ForRext values below 2.2 kΩ, the oscillator operation maybecome unstable, or stop completely. For very highRext values (e.g., 1 MΩ), the oscillator becomessensitive to noise, humidity and leakage. Thus, werecommend to keep Rext between 3 kΩ and 100 kΩ.Although the oscillator will operate with no externalcapacitor (Cext = 0 pF), we recommend using valuesabove 20 pF for noise and stability reasons. With no orsmall external capacitance, the oscillation frequencycan vary dramatically due to changes in externalcapacitances, such as PCB trace capacitance orpackage lead frame capacitance.The oscillator frequency, divided by 4, is available onthe OSC2/CLKOUT pin, and can be used for testpurposes or to synchronize other logic (Figure 3-2 forwaveform).FIGURE 7-6:RC OSCILLATOR MODE10k20 pF20 pFFigure 7-5 shows a series resonant oscillator circuit.This circuit is also designed to use the fundamentalfrequency of the crystal. The inverter performs a 180°phase shift in a series resonant oscillator circuit. The330 Ω resistors provide the negative feedback to biasthe inverters in their linear region.VDDRextCextVDDFosc/4<strong>PIC16C55X</strong>OSC1Internal ClockOSC2/CLKOUTFIGURE 7-5:EXTERNAL SERIESRESONANT CRYSTALOSCILLATOR CIRCUIT330 Ω74AS04330 Ω74AS04To otherDevices<strong>PIC16C55X</strong>74AS040.1 µFCLKINXTALDS40143C-page 38 Preliminary © 1998 Microchip Technology Inc.

<strong>PIC16C55X</strong>7.3 ResetThe <strong>PIC16C55X</strong> differentiates between various kindsof reset:a) Power-on reset (POR)b) MCLR reset during normal operationc) MCLR reset during SLEEPd) WDT reset (normal operation)e) WDT wake-up (SLEEP)Some registers are not affected in any reset condition;their status is unknown on POR and unchanged in anyother reset. Most other registers are reset to a “resetstate” on Power-on reset, on MCLR or WDT reset andon MCLR reset during SLEEP. They are not affected bya WDT wake-up, since this is viewed as the resumptionof normal operation. TO and PD bits are set or cleareddifferently in different reset situations as indicated inTable 7-4. These bits are used in software to determinethe nature of the reset. See Table 7-6 for a full descriptionof reset states of all registers.A simplified block diagram of the on-chip reset circuit isshown in Figure 7-7.The MCLR reset path has a noise filter to detect andignore small pulses. See Table 10-4 for pulse widthspecification.FIGURE 7-7:SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUITExternalResetMCLR/VPP PinVDDWDTModuleVDD risedetectSLEEPWDTTime-outResetPower-on ResetSOST/PWRTOST10-bit Ripple-counterRQChip_ResetOSC1/CLKINPinOn-chip (1)RC OSCPWRT10-bit Ripple-counterEnable PWRTSee Table 7-3 for time-out situations.Enable OSTNote 1:This is a separate oscillator from the RC oscillator of the CLKIN pin.© 1998 Microchip Technology Inc. Preliminary DS40143C-page 39

<strong>PIC16C55X</strong>7.4 Power-on Reset (POR), Power-upTimer (PWRT), Oscillator Start-upTimer (OST)7.4.1 POWER-ON RESET (POR)A Power-on Reset pulse is generated on-chip whenVDD rise is detected (in the range of 1.6 V – 1.8 V). Totake advantage of the POR, just tie the MCLR pinthrough a resistor to VDD. This will eliminate externalRC components usually needed to create Power-onReset. A maximum rise time for VDD is required. SeeElectrical Specifications for details.The POR circuit does not produce internal reset whenVDD declines.When the device starts normal operation (exits thereset condition), device operating parameters (voltage,frequency, temperature, etc.) must be met to ensureoperation. If these conditions are not met, the devicemust be held in reset until the operating conditions aremet.For additional information, refer to Application NoteAN607 “Power-up Trouble Shooting”.7.4.2 POWER-UP TIMER (PWRT)The Power-up Timer provides a fixed 72 ms (nominal)time-out on power-up only, from POR. The Power-upTimer operates on an internal RC oscillator. The chip iskept in reset as long as PWRT is active. The PWRTdelay allows the VDD to rise to an acceptable level. Aconfiguration bit, PWRTE can disable (if set) or enable(if cleared or programmed) the Power-up Timer. ThePower-Up Time delay will vary from chip to chip anddue to VDD, temperature and process variation. SeeDC parameters for details.7.4.3 OSCILLATOR START-UP TIMER (OST)The Oscillator Start-Up Timer (OST) provides a 1024oscillator cycle (from OSC1 input) delay after thePWRT delay is over. This ensures that the crystaloscillator or resonator has started and stabilized.The OST time-out is invoked only for XT, LP and HSmodes and only on power-on reset or wake-up fromSLEEP.7.4.4 TIME-OUT SEQUENCEOn power-up, the time-out sequence is as follows: FirstPWRT time-out is invoked after POR has expired, thenOST is activated. The total time-out will vary based onoscillator configuration and PWRTE bit status. Forexample, in RC mode with PWRTE bit erased (PWRTdisabled), there will be no time-out at all. Figure 7-8,Figure 7-9 and Figure 7-10 depict time-out sequences.Since the time-outs occur from the POR pulse, if MCLRis kept low long enough, the time-outs will expire. Thenbringing MCLR high will begin execution immediately(see Figure 7-9). This is useful for testing purposes orto synchronize more than one <strong>PIC16C55X</strong> device operatingin parallel.Table 7-5 shows the reset conditions for some specialregisters, while Table 7-6 shows the reset conditions forall the registers.DS40143C-page 40 Preliminary © 1998 Microchip Technology Inc.

<strong>PIC16C55X</strong>7.4.5 POWER CONTROL/STATUS REGISTER(PCON)<strong>Bit</strong>1 is POR (Power-on-reset). It is a ‘0’ onpower-on-reset and unaffected otherwise. The usermust write a ‘1’ to this bit following a power-on-reset.On a subsequent reset if POR is ‘0’, it will indicate thata power-on-reset must have occurred (VDD may havegone too low).TABLE 7-3:TIME-OUT IN VARIOUS SITUATIONSOscillator ConfigurationPower-upPWRTE = 0 PWRTE = 1Wake-up fromSLEEPXT, HS, LP 72 ms + 1024 TOSC 1024 TOSC 1024 TOSCRC 72 ms — —TABLE 7-4:STATUS BITS AND THEIR SIGNIFICANCEPOR TO PD0 1 1 Power-on-reset0 0 X Illegal, TO is set on POR0 X 0 Illegal, PD is set on POR1 0 u WDT Reset1 0 0 WDT Wake-up1 u u MCLR reset during normal operation1 1 0 MCLR reset during SLEEP© 1998 Microchip Technology Inc. Preliminary DS40143C-page 41

<strong>PIC16C55X</strong>TABLE 7-5:INITIALIZATION CONDITION FOR SPECIAL REGISTERSConditionProgramCounterSTATUSRegisterPCONRegisterPower-on Reset 000h 0001 1xxx ---- --0-MCLR reset during normal operation 000h 000u uuuu ---- --u-MCLR reset during SLEEP 000h 0001 0uuu ---- --u-WDT reset 000h 0000 uuuu ---- --u-WDT Wake-up PC + 1 uuu0 0uuu ---- --u-Interrupt Wake-up from SLEEP PC + 1 (1) uuu1 0uuu ---- --u-Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as ‘0’.Note 1: When the wake-up is due to an interrupt and global enable bit, GIE is set, the PC is loaded with the interrupt vector(0004h) after execution of PC+1.TABLE 7-6:INITIALIZATION CONDITION FOR REGISTERS• MCLR Reset duringnormal operation• MCLR Reset duringSLEEP• Wake up from SLEEPthrough interrupt• Wake up from SLEEPthrough WDT time-outRegister Address Power-on Reset • WDT ResetW - xxxx xxxx uuuu uuuu uuuu uuuuINDF 00h - - -TMR0 01h xxxx xxxx uuuu uuuu uuuu uuuuPCL 02h 0000 0000 0000 0000 PC + 1 (2)STATUS 03h 0001 1xxx 000q quuu (3) uuuq quuu (3)FSR 04h xxxx xxxx uuuu uuuu uuuu uuuuPORTA 05h ---x xxxx ---u uuuu ---u uuuuPORTB 06h xxxx xxxx uuuu uuuu uuuu uuuuPCLATH 0Ah ---0 0000 ---0 0000 ---u uuuuINTCON 0Bh 0000 000x 0000 000u uuuu uuuu (1)OPTION 81h 1111 1111 1111 1111 uuuu uuuuTRISA 85h ---1 1111 ---1 1111 ---u uuuuTRISB 86h 1111 1111 1111 1111 uuuu uuuuPCON 8Eh ---- --0- ---- --u- ---- --u-Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as ‘0’,q = value depends on condition.Note 1: One or more bits in INTCON will be affected (to cause wake-up).2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interruptvector (0004h).3: See Table 7-5 for reset value for specific condition.DS40143C-page 42 Preliminary © 1998 Microchip Technology Inc.

<strong>PIC16C55X</strong>FIGURE 7-8: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 1VDDMCLRINTERNAL PORTPWRTPWRT TIME-OUTTOSTOST TIME-OUTINTERNAL RESETFIGURE 7-9: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2VDDMCLRINTERNAL PORTPWRTPWRT TIME-OUTTOSTOST TIME-OUTINTERNAL RESETFIGURE 7-10: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD): CASE 3VDDMCLRINTERNAL PORTPWRTPWRT TIME-OUTTOSTOST TIME-OUTINTERNAL RESET© 1998 Microchip Technology Inc. Preliminary DS40143C-page 43

<strong>PIC16C55X</strong>FIGURE 7-11:EXTERNAL POWER-ONRESET CIRCUIT (FOR SLOWVDD POWER-UP)VDDVDDDRR1MCLRC<strong>PIC16C55X</strong>Note 1: External power-on reset circuit is requiredonly if VDD power-up slope is too slow.The diode D helps discharge the capacitorquickly when VDD powers down.2: < 40 kΩ is recommended to make surethat voltage drop across R does not violatethe device’s electrical specification.3: R1 = 100Ω to 1 kΩ will limit any currentflowing into MCLR from external capacitorC in the event of MCLR/VPP pin breakdowndue to Electrostatic Discharge(ESD) or Electrical Overstress (EOS).DS40143C-page 44 Preliminary © 1998 Microchip Technology Inc.

<strong>PIC16C55X</strong>7.5 InterruptsThe <strong>PIC16C55X</strong> has 3 sources of interrupt:• External interrupt RB0/INT• TMR0 overflow interrupt• PortB change interrupts (pins RB7:RB4)The interrupt control register (INTCON) recordsindividual interrupt requests in flag bits. It also hasindividual and global interrupt enable bits.A global interrupt enable bit, GIE (INTCON)enables (if set) all un-masked interrupts or disables (ifcleared) all interrupts. Individual interrupts can bedisabled through their corresponding enable bits inINTCON register. GIE is cleared on reset.The “return from interrupt” instruction, RETFIE, exitsthe interrupt routine as well as sets the GIE bit, whichre-enables RB0/INT interrupts.The INT pin interrupt, the RB port change interrupt andthe TMR0 overflow interrupt flags are contained in theINTCON register.When an interrupt is responded to, the GIE is clearedto disable any further interrupt, the return address ispushed into the stack and the PC is loaded with 0004h.Once in the interrupt service routine the source(s) ofthe interrupt can be determined by polling the interruptflag bits. The interrupt flag bit(s) must be cleared in softwarebefore re-enabling interrupts to avoid RB0/INTrecursive interrupts.For external interrupt events, such as the INT pin orPORTB change interrupt, the interrupt latency will bethree or four instruction cycles. The exact latencydepends when the interrupt event occurs (Figure 7-13).The latency is the same for one or two cycleinstructions. Once in the interrupt service routine thesource(s) of the interrupt can be determined by pollingthe interrupt flag bits. The interrupt flag bit(s) must becleared in software before re-enabling interrupts toavoid multiple interrupt requests. Individual interruptflag bits are set regardless of the status of theircorresponding mask bit or the GIE bit.Note 1: Individual interrupt flag bits are setregardless of the status of theircorresponding mask bit or the GIE bit.2: When an instruction that clears the GIEbit is executed, any interrupts that werepending for execution in the next cycleare ignored. The CPU will execute aNOP in the cycle immediately followingthe instruction which clears the GIE bit.The interrupts which were ignored arestill pending to be serviced when the GIEbit is set again.FIGURE 7-12:INTERRUPT LOGICT0IFT0IEINTFINTERBIFRBIEWake-up(If in SLEEP mode)Interruptto CPUGIE© 1998 Microchip Technology Inc. Preliminary DS40143C-page 45

<strong>PIC16C55X</strong>7.5.1 RB0/INT INTERRUPTAn external interrupt on RB0/INT pin is edge triggered:either rising if INTEDG bit (OPTION) is set, or fallingif INTEDG bit is clear. When a valid edge appearson the RB0/INT pin, the INTF bit (INTCON) is set.This interrupt can be disabled by clearing the INTEcontrol bit (INTCON). The INTF bit must be clearedin software in the interrupt service routine beforere-enabling this interrupt. The RB0/INT interrupt canwake-up the processor from SLEEP, if the INTE bit wasset prior to going into SLEEP. The status of the GIE bitdecides whether or not the processor branches to theinterrupt vector following wake-up. See Section 7.8 fordetails on SLEEP and Figure 7-16 for timing ofwake-up from SLEEP through RB0/INT interrupt.7.5.2 TMR0 INTERRUPTAn overflow (FFh → 00h) in the TMR0 register willset the T0IF (INTCON) bit. The interrupt canbe enabled/disabled by setting/clearing T0IE(INTCON) bit. For operation of the Timer0 module,see Section 6.0.7.5.3 PORTB INTERRUPTAn input change on PORTB sets the RBIF(INTCON) bit. The interrupt can be enabled/disabledby setting/clearing the RBIE (INTCON) bit.For operation of PORTB (Section 5.2).Note:If a change on the I/O pin should occurwhen the read operation is being executed(start of the Q2 cycle), then the RBIF interruptflag may get set.FIGURE 7-13:INT PIN INTERRUPT TIMINGQ1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4OSC1CLKOUT 34INT pinINTF flag(INTCON)151Interrupt Latency2GIE bit(INTCON)INSTRUCTION FLOWPCInstructionfetchedPC PC+1 PC+1 0004h 0005hInst (PC)Inst (PC+1)—Inst (0004h)Inst (0005h)InstructionexecutedInst (PC-1)Inst (PC)Dummy CycleDummy CycleInst (0004h)Note1: INTF flag is sampled here (every Q1).2: Interrupt latency = 3-4 Tcy where Tcy = instruction cycle time.Latency is the same whether Inst (PC) is a single cycle or a 2-cycle instruction.3: CLKOUT is available only in RC oscillator mode.4: For minimum width of INT pulse, refer to AC specs.5: INTF is enabled to be set anytime during the Q4-Q1 cycles.DS40143C-page 46 Preliminary © 1998 Microchip Technology Inc.

<strong>PIC16C55X</strong>7.6 Context Saving During InterruptsDuring an interrupt, only the return PC value is savedon the stack. Typically, users may wish to save key registersduring an interrupt, e.g. W register and STATUSregister. This will have to be implemented in software.Example 7-1 stores and restores the STATUS and Wregisters. The user register, W_TEMP, must be definedin both banks and must be defined at the same offsetfrom the bank base address (i.e., W_TEMP is definedat 0x20 in Bank 0 and it must also be defined at 0xA0in Bank 1). The user register, STATUS_TEMP, must bedefined in Bank 0. The Example 7-1:• Stores the W register• Stores the STATUS register in Bank 0• Executes the ISR code• Restores the STATUS (and bank select bitregister)• Restores the W registerEXAMPLE 7-1:SAVING THE STATUS ANDW REGISTERS IN RAMMOVWF W_TEMP ;copy W to temp register,;could be in either bankSWAPF STATUS,W ;swap status to be saved into WBCF STATUS,RP0 ;change to bank 0 regardless;of current bankMOVWF STATUS_TEMP ;save status to bank 0;register:: (ISR):SWAPF STATUS_TEMP,W ;swap STATUS_TEMP register;into W, sets bank to original;stateMOVWF STATUS ;move W into STATUS registerSWAPF W_TEMP,F ;swap W_TEMPSWAPF W_TEMP,W ;swap W_TEMP into W7.7 Watchdog Timer (WDT)The watchdog timer is a free running on-chip RC oscillatorwhich does not require any external components.This RC oscillator is separate from the RC oscillator ofthe CLKIN pin. That means that the WDT will run, evenif the clock on the OSC1 and OSC2 pins of the devicehas been stopped, for example, by execution of aSLEEP instruction. During normal operation, a WDTtime-out generates a device RESET. If the device is inSLEEP mode, a WDT time-out causes the device towake-up and continue with normal operation. The WDTcan be permanently disabled by programming the configurationbit WDTE as clear (Section 7.1).7.7.1 WDT PERIODThe WDT has a nominal time-out period of 18 ms, (withno prescaler). The time-out periods vary with temperature,VDD and process variations from part to part (seeDC specs). If longer time-out periods are desired, aprescaler with a division ratio of up to 1:128 can beassigned to the WDT under software control by writingto the OPTION register. Thus, time-out periods up to2.3 seconds can be realized.The CLRWDT and SLEEP instructions clear the WDTand the postscaler, if assigned to the WDT, and preventit from timing out and generating a device RESET.The TO bit in the STATUS register will be cleared upona Watchdog Timer time-out.7.7.2 WDT PROGRAMMING CONSIDERATIONSIt should also be taken in account that under worst caseconditions (VDD = Min., Temperature = Max., max.WDT prescaler) it may take several seconds before aWDT time-out occurs.© 1998 Microchip Technology Inc. Preliminary DS40143C-page 47

<strong>PIC16C55X</strong>FIGURE 7-14:WATCHDOG TIMER BLOCK DIAGRAMFrom TMR0 Clock Source(Figure 6-6)WatchdogTimer01•MUXPostscaler88 - to -1 MUXPSWDTEnable <strong>Bit</strong>PSA•To TMR0 (Figure 6-6)01MUXPSAWDTTime-outNote: T0SE, T0CS, PSA, PS0-PS2 are bits in the OPTION register.FIGURE 7-15:SUMMARY OF WATCHDOG TIMER REGISTERSAddress Name <strong>Bit</strong> 7 <strong>Bit</strong> 6 <strong>Bit</strong> 5 <strong>Bit</strong> 4 <strong>Bit</strong> 3 <strong>Bit</strong> 2 <strong>Bit</strong> 1 <strong>Bit</strong> 0 Value on PORValue on allother Resets2007h Config. bits — + CP1 CP0 PWRTE WDTE FOSC1 FOSC081h OPTION RBPU INTEDG T0CS T0SE PSA PS2 PS1 PS0 1111 1111 1111 1111Legend: Shaded cells are not used by the Watchdog Timer.— = Unimplemented location, read as ‘0’.+ = Reserved for future use.DS40143C-page 48 Preliminary © 1998 Microchip Technology Inc.

<strong>PIC16C55X</strong>7.8 Power-Down Mode (SLEEP)The Power-down mode is entered by executing aSLEEP instruction.If enabled, the Watchdog Timer will be cleared butkeeps running, the PD bit in the STATUS register iscleared, the TO bit is set, and the oscillator driver isturned off. The I/O ports maintain the status they had,before SLEEP was executed (driving high, low, orhi-impedance).For lowest current consumption in this mode, all I/Opins should be either at VDD, or VSS, with no externalcircuitry drawing current from the I/O pin. I/O pins thatare hi-impedance inputs should be pulled high or lowexternally to avoid switching currents caused by floatinginputs. The T0CKI input should also be at VDD orVSS for lowest current consumption. The contributionfrom on chip pull-ups on PORTB should be considered.The MCLR pin must be at a logic high level (VIHMC).Note:It should be noted that a RESET generatedby a WDT time-out does not drive MCLRpin low.7.8.1 WAKE-UP FROM SLEEPThe device can wake-up from SLEEP through one ofthe following events:1. External reset input on MCLR pin2. Watchdog Timer Wake-up (if WDT was enabled)3. Interrupt from RB0/INT pin or RB Port changeThe first event will cause a device reset. The two latterevents are considered a continuation of program execution.The TO and PD bits in the STATUS register canbe used to determine the cause of device reset. PDbit, which is set on power-up is cleared when SLEEP isinvoked. TO bit is cleared if WDT Wake-up occurred.When the SLEEP instruction is being executed, thenext instruction (PC + 1) is pre-fetched. For the deviceto wake-up through an interrupt event, the correspondinginterrupt enable bit must be set (enabled). Wake-upis regardless of the state of the GIE bit. If the GIE bit isclear (disabled), the device continues execution at theinstruction after the SLEEP instruction. If the GIE bit isset (enabled), the device executes the instruction afterthe SLEEP instruction and then branches to the interruptaddress (0004h). In cases where the execution ofthe instruction following SLEEP is not desirable, theuser should have an NOP after the SLEEP instruction.Note:If the global interrupts are disabled (GIE iscleared), but any interrupt source has bothits interrupt enable bit and the correspondinginterrupt flag bits set, the device willimmediately wakeup from sleep. The sleepinstruction is completely executed.The WDT is cleared when the device wakes-up fromsleep, regardless of the source of wake-up.FIGURE 7-16:WAKE-UP FROM SLEEP THROUGH INTERRUPTOSC1CLKOUT(4)Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4TOST(2)INT pinINTF flag(INTCON)GIE bit(INTCON)Processor inSLEEPInterrupt Latency(Note 2)INSTRUCTION FLOWPCInstructionfetchedInstructionexecutedPC PC+1 PC+2Inst(PC) = SLEEPInst(PC - 1)Inst(PC + 1)SLEEPPC+2Inst(PC + 2)Inst(PC + 1)PC + 2 0004h 0005hInst(0004h) Inst(0005h)Dummy cycle Dummy cycle Inst(0004h)Note 1: XT, HS or LP oscillator mode assumed.2: TOST = 1024TOSC (drawing not to scale) This delay will not be there for RC osc mode.3: GIE = '1' assumed. In this case after wake- up, the processor jumps to the interrupt routine. If GIE = '0', execution will continue in-line.4: CLKOUT is not available in these osc modes, but shown here for timing reference.© 1998 Microchip Technology Inc. Preliminary DS40143C-page 49

<strong>PIC16C55X</strong>7.9 Code ProtectionIf the code protection bit(s) have not beenprogrammed, the on-chip program memory can beread out for verification purposes.Note:Microchip does not recommend codeprotecting windowed devices.7.10 ID LocationsFour memory locations (2000h-2003h) are designatedas ID locations where the user can store checksum orother code-identification numbers. These locations arenot accessible during normal execution but arereadable and writable during program/verify. Only theleast significant 4 bits of the ID locations are used.7.11 In-Circuit Serial ProgrammingThe <strong>PIC16C55X</strong> microcontrollers can be seriallyprogrammed while in the end application circuit. This issimply done with two lines for clock and data, and threeother lines for power, ground, and the programmingvoltage. This allows customers to manufacture boardswith unprogrammed devices, and then program themicrocontroller just before shipping the product. Thisalso allows the most recent firmware or a customfirmware to be programmed.The device is placed into a program/verify mode byholding the RB6 and RB7 pins low while raising theMCLR (VPP) pin from VIL to VIHH (see programmingspecification). RB6 becomes the programming clockand RB7 becomes the programming data. Both RB6and RB7 are Schmitt Trigger inputs in this mode.After reset, to place the device into programming/verifymode, the program counter (PC) is at location 00h. A6-bit command is then supplied to the device.Depending on the command, 14-bits of program dataare then supplied to or from the device, depending if thecommand was a load or a read. For complete details ofserial programming, please refer to the PIC16C6X/7XProgramming Specifications (Literature #DS30228).A typical in-circuit serial programming connection isshown in Figure 7-17.FIGURE 7-17:TYPICAL IN-CIRCUIT SERIALPROGRAMMINGCONNECTIONExternalConnectorSignals+5V0VVPPCLK<strong>Data</strong> I/OTo NormalConnections<strong>PIC16C55X</strong>VDDVSSMCLR/VPPRB6RB7VDDTo NormalConnectionsDS40143C-page 50 Preliminary © 1998 Microchip Technology Inc.

<strong>PIC16C55X</strong>8.0 INSTRUCTION SET SUMMARYEach <strong>PIC16C55X</strong> instruction is a 14-bit word dividedinto an OPCODE which specifies the instruction typeand one or more operands which further specify theoperation of the instruction. The <strong>PIC16C55X</strong> instructionset summary in Table 8-2 lists byte-oriented,bit-oriented, and literal and control operations.Table 8-1 shows the opcode field descriptions.For byte-oriented instructions, 'f' represents a fileregister designator and 'd' represents a destinationdesignator. The file register designator specifies whichfile register is to be used by the instruction.The destination designator specifies where the result ofthe operation is to be placed. If 'd' is zero, the result isplaced in the W register. If 'd' is one, the result is placedin the file register specified in the instruction.For bit-oriented instructions, 'b' represents a bit fielddesignator which selects the number of the bit affectedby the operation, while 'f' represents the number of thefile in which the bit is located.For literal and control operations, 'k' represents aneight or eleven bit constant or literal value.TABLE 8-1:FieldOPCODE FIELDDESCRIPTIONSDescriptionf Register file address (0x00 to 0x7F)W Working register (accumulator)b <strong>Bit</strong> address within an 8-bit file registerk Literal field, constant data or labelx Don't care location (= 0 or 1)The assembler will generate code with x = 0. It is therecommended form of use for compatibility with allMicrochip software tools.d Destination select; d = 0: store result in W,d = 1: store result in file register f.Default is d = 1label Label nameTOS Top of StackPC Program CounterPCLATH Program Counter High LatchGIE Global Interrupt Enable bitWDT Watchdog Timer/CounterTO Time-out bitPD Power-down bitdest Destination either the W register or the specifiedregister file location[ ] Options( ) Contents→ Assigned to< > Register bit field∈ In the set ofitalics User defined term (font is courier)The instruction set is highly orthogonal and is groupedinto three basic categories:• Byte-oriented operations• <strong>Bit</strong>-oriented operations• Literal and control operationsAll instructions are executed within one singleinstruction cycle, unless a conditional test is true or theprogram counter is changed as a result of aninstruction. In this case, the execution takes twoinstruction cycles with the second cycle executed as aNOP. One instruction cycle consists of four oscillatorperiods. Thus, for an oscillator frequency of 4 MHz, thenormal instruction execution time is 1 µs. If aconditional test is true or the program counter ischanged as a result of an instruction, the instructionexecution time is 2 µs.Table 8-1 lists the instructions recognized by theMPASM assembler.Figure 8-1 shows the three general formats that theinstructions can have.Note:All examples use the following format to represent ahexadecimal number:0xhhwhere h signifies a hexadecimal digit.FIGURE 8-1:To maintain upward compatibility withfuture PICmicro ® products, do not use theOPTION and TRIS instructions.GENERAL FORMAT FORINSTRUCTIONSByte-oriented file register operations13 8 7 6 0OPCODE d f (FILE #)d = 0 for destination Wd = 1 for destination ff = 7-bit file register address<strong>Bit</strong>-oriented file register operations13 10 9 7 6 0OPCODE b (BIT #) f (FILE #)b = 3-bit bit addressf = 7-bit file register addressLiteral and control operationsGeneral13 8 7 0OPCODEk (literal)k = 8-bit immediate valueCALL and GOTO instructions only13 11 10 0OPCODEk (literal)k = 11-bit immediate value© 1998 Microchip Technology Inc. Preliminary DS40143C-page 51

<strong>PIC16C55X</strong>TABLE 8-2:Mnemonic,Operands<strong>PIC16C55X</strong> INSTRUCTION SETDescription Cycles 14-<strong>Bit</strong> Opcode StatusMSbLSbAffectedNotesBYTE-ORIENTED FILE REGISTER OPERATIONSADDWFANDWFCLRFCLRWCOMFDECFDECFSZINCFINCFSZIORWFMOVFMOVWFNOPRLFRRFSUBWFSWAPFXORWFf, df, df-f, df, df, df, df, df, df, df-f, df, df, df, df, dAdd W and fAND W with fClear fClear WComplement fDecrement fDecrement f, Skip if 0Increment fIncrement f, Skip if 0Inclusive OR W with fMove fMove W to fNo OperationRotate Left f through CarryRotate Right f through CarrySubtract W from fSwap nibbles in fExclusive OR W with fBIT-ORIENTED FILE REGISTER OPERATIONSBCFBSFBTFSCBTFSSf, bf, bf, bf, b<strong>Bit</strong> Clear f<strong>Bit</strong> Set f<strong>Bit</strong> Test f, Skip if Clear<strong>Bit</strong> Test f, Skip if SetLITERAL AND CONTROL OPERATIONSADDLWANDLWCALLCLRWDTGOTOIORLWMOVLWRETFIERETLWRETURNSLEEPSUBLWXORLWkkk-kkk-k--kkAdd literal and WAND literal with WCall subroutineClear Watchdog TimerGo to addressInclusive OR literal with WMove literal to WReturn from interruptReturn with literal in WReturn from SubroutineGo into standby modeSubtract W from literalExclusive OR literal with W1111111(2)11(2)111111111111 (2)1 (2)1121211222111000000000000000000000000000000000000010101011111100010111100110000111101110101000100011001001110111010111101001000000000001101110000101110011000bb01bb10bb11bb111x10010kkk00001kkk100000xx000001xx00000000110x1010dfffdffflfff0000dfffdfffdfffdfffdfffdfffdffflfff0xx0dfffdfffdfffdfffdfffbfffbfffbfffbfffkkkkkkkkkkkk0110kkkkkkkkkkkk0000kkkk00000110kkkkkkkkffffffffffff0011ffffffffffffffffffffffffffffffff0000ffffffffffffffffffffffffffffffffffffkkkkkkkkkkkk0100kkkkkkkkkkkk1001kkkk10000011kkkkkkkkC,DC,ZZZZZZZZZCCC,DC,ZZC,DC,ZZTO,PDZTO,PDC,DC,ZZNote 1: When an I/O register is modified as a function of itself ( e.g., MOVF PORTB, 1), the value used will be that value presenton the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an externaldevice, the data will be written back with a '0'.2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assignedto the Timer0 Module.3: If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle isexecuted as a NOP.1,21,221,21,21,2,31,21,2,31,21,21,21,21,21,21,21,21,233DS40143C-page 52 Preliminary © 1998 Microchip Technology Inc.