Pseudo-Noise (PN) Ranging Systems - CCSDS

Pseudo-Noise (PN) Ranging Systems - CCSDS

Pseudo-Noise (PN) Ranging Systems - CCSDS

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

<strong>CCSDS</strong> INFORMATIONAL REPORT CONCERNING PSEUDO-NOISE RANGING SYSTEMS<br />

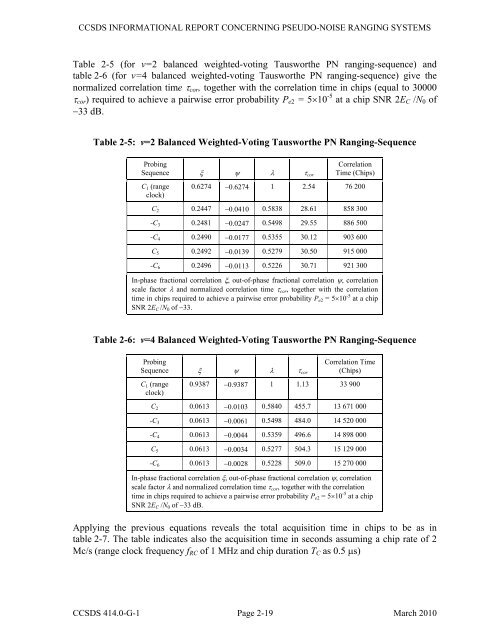

Table 2-5 (for v=2 balanced weighted-voting Tausworthe <strong>PN</strong> ranging-sequence) and<br />

table 2-6 (for v=4 balanced weighted-voting Tausworthe <strong>PN</strong> ranging-sequence) give the<br />

normalized correlation time τcor, together with the correlation time in chips (equal to 30000<br />

τcor) required to achieve a pairwise error probability Pe2 = 5×10 -5 at a chip SNR 2EC /N0 of<br />

−33 dB.<br />

Table 2-5: v=2 Balanced Weighted-Voting Tausworthe <strong>PN</strong> <strong>Ranging</strong>-Sequence<br />

Probing<br />

Sequence ξ ψ λ τ cor<br />

C 1 (range<br />

clock)<br />

Correlation<br />

Time (Chips)<br />

0.6274 −0.6274 1 2.54 76 200<br />

C 2 0.2447 −0.0410 0.5838 28.61 858 300<br />

-C3 0.2481 −0.0247 0.5498 29.55 886 500<br />

-C 4 0.2490 −0.0177 0.5355 30.12 903 600<br />

C 5 0.2492 −0.0139 0.5279 30.50 915 000<br />

-C 6 0.2496 −0.0113 0.5226 30.71 921 300<br />

In-phase fractional correlation ξ, out-of-phase fractional correlation ψ, correlation<br />

scale factor λ and normalized correlation time τ cor, together with the correlation<br />

time in chips required to achieve a pairwise error probability Pe2 = 5×10 -5 at a chip<br />

SNR 2EC /N 0 of −33.<br />

Table 2-6: v=4 Balanced Weighted-Voting Tausworthe <strong>PN</strong> <strong>Ranging</strong>-Sequence<br />

Probing<br />

Sequence ξ ψ λ τ cor<br />

C 1 (range<br />

clock)<br />

Correlation Time<br />

(Chips)<br />

0.9387 −0.9387 1 1.13 33 900<br />

C 2 0.0613 −0.0103 0.5840 455.7 13 671 000<br />

-C 3 0.0613 −0.0061 0.5498 484.0 14 520 000<br />

-C 4 0.0613 −0.0044 0.5359 496.6 14 898 000<br />

C 5 0.0613 −0.0034 0.5277 504.3 15 129 000<br />

-C 6 0.0613 −0.0028 0.5228 509.0 15 270 000<br />

In-phase fractional correlation ξ, out-of-phase fractional correlation ψ, correlation<br />

scale factor λ and normalized correlation time τ cor, together with the correlation<br />

time in chips required to achieve a pairwise error probability Pe2 = 5×10 -5 at a chip<br />

SNR 2EC /N 0 of −33 dB.<br />

Applying the previous equations reveals the total acquisition time in chips to be as in<br />

table 2-7. The table indicates also the acquisition time in seconds assuming a chip rate of 2<br />

Mc/s (range clock frequency fRC of 1 MHz and chip duration TC as 0.5 μs)<br />

<strong>CCSDS</strong> 414.0-G-1 Page 2-19 March 2010