Zadaci za pripremu prvog kolokvijuma (pdf)

Zadaci za pripremu prvog kolokvijuma (pdf)

Zadaci za pripremu prvog kolokvijuma (pdf)

- No tags were found...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

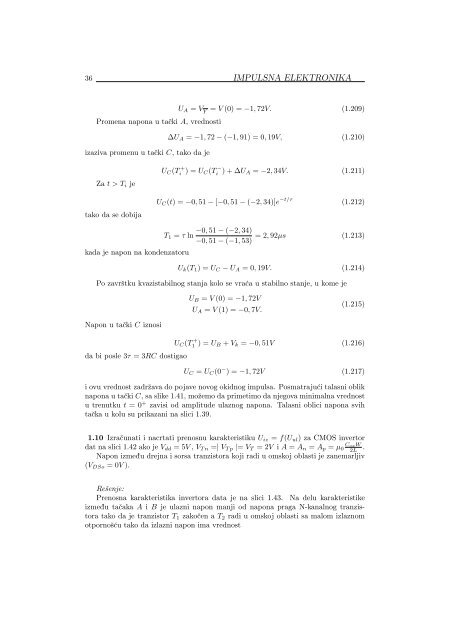

36 IMPULSNA ELEKTRONIKAU A = V Y= V (0) = −1, 72V. (1.209)Promena napona u tački A, vrednosti∆U A = −1, 72 − (−1, 91) = 0, 19V, (1.210)i<strong>za</strong>ziva promenu u tački C, tako da jeZa t > T i jetako da se dobijaU C (T + i ) = U C(T − i ) + ∆U A = −2, 34V. (1.211)U C (t) = −0, 51 − [−0, 51 − (−2, 34)]e −t/τ (1.212)T 1 = τ lnkada je napon na konden<strong>za</strong>toru−0, 51 − (−2, 34)= 2, 92µs (1.213)−0, 51 − (−1, 53)U k (T 1 ) = U C − U A = 0, 19V. (1.214)Po <strong>za</strong>vrštku kvazistabilnog stanja kolo se vraća u stabilno stanje, u kome jeU B = V (0) = −1, 72VU A = V (1) = −0, 7V.(1.215)Napon u tački C iznosida bi posle 3τ = 3RC dostigaoU C (T + 1 ) = U B + V k = −0, 51V (1.216)U C = U C (0 − ) = −1, 72V (1.217)i ovu vrednost <strong>za</strong>država do pojave novog okidnog impulsa. Posmatrajući talasni obliknapona u tački C, sa slike 1.41, možemo da primetimo da njegova minimalna vrednostu trenutku t = 0 + <strong>za</strong>visi od amplitude ulaznog napona. Talasni oblici napona svihtačka u kolu su prika<strong>za</strong>ni na slici 1.39.1.10 Izračunati i nacrtati prenosnu karakteristiku U iz = f(U ul ) <strong>za</strong> CMOS invertorCdat na slici 1.42 ako je V dd = 5V , V T n =| V T p |= V T = 2V i A = A n = A p = µ ox W0 2L .Napon izmed - u drejna i sorsa tranzistora koji radi u omskoj oblasti je <strong>za</strong>nemarljiv(V DSo = 0V ).Rešenje:Prenosna karakteristika invertora data je na slici 1.43. Na delu karakteristikeizmed - u tačaka A i B je ulazni napon manji od napona praga N-kanalnog tranzistoratako da je tranzistor T 1 <strong>za</strong>kočen a T 2 radi u omskoj oblasti sa malom izlaznomotpornošću tako da izlazni napon ima vrednost

38 IMPULSNA ELEKTRONIKAU iz = 2 + U ul + √ 5 − 2U ul <strong>za</strong> 2V ≤ U ul ≤ 2, 5V, U iz > U ul − 2 (1.224)Na delu C − D prenosne karakteristike, oba tranzistora su u <strong>za</strong>sićenju, tako daizjednačavanje struja drejna daje jednačinučijim se rešavanjem dobijaA(U ul − V T n ) 2 = A(U ul − V dd − V T p ) 2 (1.225)| U ul − 2 |=| U ul − 3 |⇔ U ul = 2, 5V (1.226)Za U ul > 2, 5V (D − E deo prenosne karakteristike) tranzistor T 1 odlazi u omskuoblast a T 2 je u <strong>za</strong>sićenju, pa se smenom struja drejna dobija kvadratna jednačina[2A (U ul − V T n )U iz − 1 ]2 U iz2 = A(U ul − V dd − V T p ) 2 , (1.227)čijim se rešavanjem na isti način kao i na B − C delu karakteristike i <strong>za</strong>državanjemsamo fizički mogućeg rešenja, dobijaU iz = U ul − 2 − √ 2U ul − 5 <strong>za</strong> 2, 5V ≤ U ul ≤ 3V, U iz ≤ U ul + 2 (1.228)Za U ul > 3V (E − F deo karakteristike), tranzistor T 1 radi u omskoj oblasti, dokje T 2 <strong>za</strong>kočen a izlazni napon iznosiU iz = V DSo ≈ 0V. (1.229)1.11 Za astabilni multivibrator sa slike 1.44 realizovan CMOS invertorima odreditifrekvenciju rada i nacrtati talasne oblike napona u tačkama A, B i C ako invertoriimaju idealizovanu prenosnu karakteristiku sa pragom V T = V (1)/2, prika<strong>za</strong>nu naslici 1.45 i ne poseduju <strong>za</strong>štitne diode ula<strong>za</strong>. V dd = V (1) = 5V , V (0) = 0V , R = 50Ki C = 1nF .Rešenje:Velika ulazna i mala izlazna otpornost, širok opseg napona napajanja i temperaturnostabilan napon praga CMOS tranzistora omogućavaju reali<strong>za</strong>ciju jednostavnihastabilnih i monostabilnih multivibratora (generatora impulsa). Osnovno kolo CMOSgeneratora poseduje dva invertora, otpornik i konden<strong>za</strong>tor. Korišćeni otpornik možeda ima vrednosti od nekoliko KΩ do desetak MΩ a kapacitivnost konden<strong>za</strong>tora je uopsegu od stotinak pF do desetak µF pa vremenska konstanta može da se podešavau širokom opsegu (od nekoliko desetina ns do nekoliko desetina sekundi). Stabilnostna promene napona napajanja i temperature je bolja nego kod odgovarajućih kolarealizovanih bipolarnim tranzistorima.Izlaz invertora 1 je kratkospojen na ulaz invertora 2, dok je izlaz invertora 2preko konden<strong>za</strong>tora ve<strong>za</strong>n na ulaz <strong>prvog</strong> invertora. Zbog ovakve strukture, <strong>za</strong> vremepromene stanja u kolu, preko konden<strong>za</strong>tora C se <strong>za</strong>tvara petlja pozitivne povratne

LOGIČKA KOLA 39sprege. Pojačanje invertora u prelaznoj oblasti je reda 10 i više, pa je pojačanje upetlji povratne sprege veće od 100 tako da je promena napona na izlazima invertoraskokovita.Slika 1.44: Slika 1.45:Neka je na izlazu invertora 1 visok napon,Tada jeU B (0 − ) = V (1) = 5V. (1.230)U C (0 − ) = V (0) = 0V. (1.231)N-kanalni MOS tranzistor invertora 1i P-kanalni MOS tranzistor invertora2 tada ne vode. Konden<strong>za</strong>tor se punistrujom baterije V dd preko P-kanalnogtranzistora na izlazu invertora 1, krozspoljni otpornik R i kontura se <strong>za</strong>tvarapreko N-kanalnog tranzistora na izlazuinvertora 2 na masu, što je prika<strong>za</strong>nona slici 1.46.Slika 1.46:Sa R DSn2 i R DSp1 su obeležene otpornosti drejn-sors uključenih tranzistora uodgovarajućem invertoru. Oba tranzistora rade u omskoj oblasti gde otpornosti drejnsorsimaju vrednosti od stotinak Ω do oko 1KΩ. S obzirom da se najčešće <strong>za</strong> spoljniotpornik R uzimaju vrednosti koje <strong>za</strong>dovoljavaju uslovR ≫ R DSn + R DSp (1.232)otpornosti tranzistora mogu biti <strong>za</strong>nemarene pri sračunavanju perioda oscilovanja(spoj drejn-sors tranzistora se menja kratkim spojem). Za t > 0 napon na ulazu<strong>prvog</strong> invertora jegde jeU A (t) = V dd − RI(t) = V dd − [V dd − U k (0)]e −t/τ (1.233)

LOGIČKA KOLA 41U drugom kvazistabilnom stanju uključeni su P-kanalni tranzistor drugog i N-kanalni tranzistor <strong>prvog</strong> invertora. Sada se konden<strong>za</strong>tor prazni po konturi koja jeprika<strong>za</strong>na na slici 1.47. Uz <strong>za</strong>nemarivanje otpornosti tranzistora u omskoj oblasti <strong>za</strong>izlazni napon <strong>prvog</strong> invertora sa slike 1.47 može se pisatiU A (t) = RI 2 (t) = [V dd + U k (T 1 )]e −t/τ (1.244)pri čemu se u prethodnom kvazistabilnom stanju konden<strong>za</strong>tor uspeo napuniti na vrednostU k (T 1 ) = U A (T 1 ) − U C (T 1 ) = V T − 0 = V T . (1.245)Iz izra<strong>za</strong> 1.244 vidimo da se konden<strong>za</strong>tor sada prazni, odnosno ulazni napon <strong>prvog</strong>invertora opada ka nuli od početne vrednosti V dd + V T . Kada ovaj napon postanejednak naponu praga uspostavlja se pozitivna povratna sprega koja opet dovodi doskokovitih promena napona na izlazima invertora. ZaU A (T 2 ) = V T (1.246)se iz izra<strong>za</strong> 1.244 <strong>za</strong> trajanje drugog kvazistabilnog stanja dobijaT 2 = τ ln V dd + V[T= RC ln 1 + V ]dd= 54, 9µs (1.247)V TV TPrema tome, period oscilovanja iznosi[(V)(ddT = T 1 + T 2 = RC ln 1 +1 + V )]dd= 109, 8µs (1.248)V dd − V T V Ta frekvencija ima vrednostf = 1 T= 9, 1KHz. (1.249)Kada je prenosna karakteristika invertora simetričnakao na slici 1.45, V T = V dd /2, trajanjenule i jedinice je jednako. U praksi, zbogtehnoloških tolerancija parametara CMOStranzistora, napon praga CMOS invertora jenajčešće u opsegu0, 45V dd ≤ V T ≤ 0, 55V dd . (1.250)Za V T = 0, 45V dd se dobijaT 1 = 51, 7µsT 2 = 58, 4µs,i(1.251)što predstavlja odstupanje od nominalne vrednosti<strong>za</strong> 5,8 %, odnosno 6,4%, respektivno.Slika 1.48:Simetrični rezultati se dobijaju i <strong>za</strong> V T = 0, 55V dd . Perioda oscilovanja iznosi

42 IMPULSNA ELEKTRONIKAT = T 1 + T 2 = 110, 1µs (1.252)i odstupa <strong>za</strong> 0,27 % od nominalne vrednosti. Smanjivanjem napona praga V T ,kvazistabilni period T 1 se smanjuje a T 2 se povećava. Tako se promene T 1 i T 2u funkciji V T med - usobno kompenzuju pa je relativna promena perioda oscilovanjaT = T 1 + T 2 <strong>za</strong> red veličine manja od odgovarajućih promena samih kvazistabilnihperioda. Talasni oblici napona u svim tačkama kola dati su na slici 1.48.Ako uzmemo u obzir realnu prenosnu karakteristikuCMOS invertora čija je aproksimacijaopisana u <strong>za</strong>datku 1.10 naponi u tačkama B iC imaju izgled dat na slici 1.49. U opseguV T n < U A < V T , gde je sa V T n obeležen pragvod - enja N-kanalnog FET-a, kada U A raste,napon U B blago opada a u opsegu V T < U A

LOGIČKA KOLA 43a) Na slici 1.51 prika<strong>za</strong>n je CMOS invertor sa <strong>za</strong>štitinim diodama D 1 i D 2 . Akoje ulazni napon invertora u opsegu−V γ < U ul < V dd + V γ , (1.253)gde je sa V γ obeležen napon uključivanja diode, <strong>za</strong>štitne diode su isključene i njihovuticaj na karakteristiku invertora može da se <strong>za</strong>nemari. Ako je ulazni napon izvandatog opsega, jedna od dioda će voditi i tada je ulazni napon invertora ograničen navrednostU ulmax = V dd + V d , (1.254)kada vodi dioda D 1 , odnosno na vrednostU ulmin = −V d (1.255)kada vodi dioda D 2 (<strong>za</strong>nemaren je pad napona na unutrašnjoj otpornosti diode).Ograničavanjem ulaznog napona invertora se štiti oksid izmed - u gejta i kanala,kako ne bi došlo do proboja do koga može doći i usled male količine elektrostatičkognaelektrisanja. Zbog veoma velike ulazne otpornosti invertora od 10 12 do 10 14 Ω, ivrlo male struje, koje mogu nastati usled elektrostatičkog pražnjenja, mogu na gejtustvoriti veliki napon od nekoliko desetina do nekoliko stotina volti. To može dovestido proboja oksida izmed - u gejta i kanala, koji je inače veoma tanak tj. tanji od 0,1µm,i potpune destrukcije tranzistora.Nažalost, diode D 1 i D 2 , koje štite gejt od proboja, kvare karaktristike astabilnihmultivibratora. Neka jeU C (0 − ) = V (1) = 5VU B (0 − ) = V (0) = 0V.(1.256)Konden<strong>za</strong>tor se preko otpornika R puni tako da napon tačke A raste dostižućinapon pragaU A (0 − ) = V T = 2, 5V (1.257)što će i<strong>za</strong>zvati promenu u kolu. Tada je napon na konden<strong>za</strong>toruNa početku narednog kvazistabilnog perioda jeU k (0 − ) = U A − U B = V T . (1.258)U B (0 + ) = V (1)U C (0 + ) = V (0).(1.259)Pad napona iz tačke C se kroz konden<strong>za</strong>tor prenosi do tačke A, gde sada naponima vrednostU A (0 + ) = U B + U k = V dd + V T . (1.260)Zbog visokog napona na ulazu invertora, V dd + V T > V dd + V d , provela je <strong>za</strong>štitnadioda D 1 . Uvek će se na početku kvazistabilnih perioda, zbog promena nastalih naizlazima invertora, javljati skok napona na ulazu invertora gde je ve<strong>za</strong>n konden<strong>za</strong>tor,zbog čega će se uključivati odgovarajuća <strong>za</strong>štitna dioda. Sve dok jeV dd + V T > U ul = U A > V dd + V γ (1.261)

44 IMPULSNA ELEKTRONIKASlika 1.52:dioda D 1 vodi i konden<strong>za</strong>tor se prazni kroz P-kanalni FET na izlazu drugog invertorai <strong>za</strong>štitnu diodu D 1 .Sa slike 1.52 vidimo da ekvivalentna otpornost preko koje se konden<strong>za</strong>tor prazniima vrednostR ek = [(R + R DS−3N ) ‖ R d1 ] + R DS−2P ≈ R d (1.262)gde nisu uzete u obzir ulazne otpornosti tranzistora.Pošto su otpornost diode i izlazna otpornost R DS tranzistora mnogo manje odvrednosti otpornika R, koji definiše trajanje kvazistabilnih perioda, vreme vod - enjadiode će biti veoma kratko ( mnogo kraće od samih kvazistabilnih perioda) pa semože <strong>za</strong>nemariti. Dakle veoma brzo konden<strong>za</strong>tor se isprazni a napon tačke A opadnetoliko da se <strong>za</strong>štitna dioda D 1 ugasi tj.U A (0 ++ ) = V dd + V γ ⇒ U k (0 ++ = V γ . (1.263)Tako je kvazistabilni period T 1 odred - en vremenom pražnjenja konden<strong>za</strong>tora prekootpornika R, po isključivanju diode D 1 , kada napon na ulazu <strong>prvog</strong> invertora opadasve do napona praga V T odakle se dobijaU A (t) = [V dd + V γ ]e −t/τ , τ = RC (1.264)T 1 = RC ln V dd + V γV T(1.265)Ako se <strong>za</strong>nemari napon provod - enja diode <strong>za</strong> V T = V (1)/2 se dobijaT 1 = RC ln 2 ≈ 0, 7RC. (1.266)U odnosu na astabilni multivibrator sa invertorom koji ne poseduje <strong>za</strong>štitine diode(<strong>za</strong>datak 1.11 T 1 ≈ 1.1RC) kvazistabilni period je nešto kraći, zbog početnog brzogpražnjenja konden<strong>za</strong>tora kroz <strong>za</strong>štitnu diodu. Na početku narednog kvazistabilnogstanja jeU B (T + 1 ) = V (0)U C (T + 1 ) = V (1)U k (T + 1 ) = U k(T − 1 ) = V T − V dd .i(1.267)

46 IMPULSNA ELEKTRONIKAOpadanjem napona praga sa V T = 0, 5V dd na V T = 0, 4V dd , dolazi do produžavanja<strong>prvog</strong> kvazistabilnog stanja <strong>za</strong> 32,18 % i skraćivanja drugog kvazistabilnog stanja na73,69 % od nominalne vrednosti. Med - utim, perioda izlaznih impulsa se pri tomepromeni <strong>za</strong> svega 2,93%. Izobličenja pravougaonog impulsa iz tačke B sa slike 1.49(poledica realne prenosne karakteristike invertora) sada su prisutna u tački D i nemajuuticaj na punjenje konden<strong>za</strong>tora.1.13 Za komparator sa slike 1.55a) odrediti nominalne vrednosti pragova okidanja i nacrtati prenosnu karakteristikusmatrajući da CMOS invertori imaju idealnu prenosnu karakteristiku sa pragompromene V T = V (1)/2.b) Odrediti opsege pragova okidanja kola ako prag promene kod invertora može daodstupa od idealne vrednosti <strong>za</strong> ±10%, kao i vrednost otpora <strong>za</strong> ±10% od nominalne.V dd = V (1) = 5V , V (0) = 0V , R 1 = 10K i R 2 = 20K.Slika 1.55:Rešenje:a) CMOS kola imaju veliku ulaznu otpornost tako da se napon na ulazu <strong>prvog</strong>invertora može dobiti iz izra<strong>za</strong>ZaU X =R 2R 1U ul + U iz = 2 R 1 + R 2 R 1 + R 2 3 U ul + 1 3 U iz (1.272)U iz = V (0) = 0V (1.273)je U X ≤ V T odnosno smenom u 1.272 se dobija23 U ul ≤ V T . (1.274)Na izlazu komparatora nastupa promena prirastu ulaznog napona kada se napon U X izjednačisa naponom praga a tada je ulazninapon jednak gornjem pragu okidanjaSlika 1.56:U ul UX =V T= V ′ = 3 2 V T = 3, 75V (1.275)

LOGIČKA KOLA 47Za U X ≥ V T na izlazu kola je visok naponski nivoU iz = V (1) = 5V, (1.276)na osnovu čega se korišćenjem izra<strong>za</strong> 1.272 dobija da pri opadanju ulaznog naponapromena izlaznog nivoa nastupa <strong>za</strong>U ul UX =V T= V ′′ = 3V T − V (1)= 1, 25V (1.277)2čime su odred - ene nominalne vrednosti pragova okidanja.b) Ukoliko u obzir uzmemo toleranciju napona praga i otpornika, <strong>za</strong> gornji pragokidanja se dobija⎧Iz izra<strong>za</strong>V ′ = R 1 + R 2R 2V T =se <strong>za</strong> donji prag okidanja dobijaa kada se uzme u obzir i tolerancija⎪⎨⎪⎩V min ′ = R 1 + R 2V T min = 3, 17VR 2V max ′ = R 1 + R 2V T max = 4, 43VR 2(1.278)R 2V ′′ R 1+ V (1) = V T (1.279)R 1 + R 2 R 1 + R 2V ′′ = R 1 + R 2R 2V T − R 1R 2V (1) (1.280)⎧V ′′ = V T − (5 − V T )R⎨1=R 2 ⎩V min ′′ = V T min − (5−V T min)R 1R 2= 0, 569VV max ′′ = V T max − (5−V T max)R 1= 1, 829VR 2(1.281)1.14 Za astabilni multivibrator sa slike 1.57, realizovan CMOS invertorima, odreditifrekvenciju oscilovanja i nacrtati talasne oblike napona u tačkama A, B, C i Dnaznačivši sve njihove karakteristične vrednosti. Smatrati da su invertori idealnihkarakteristika i da je R 3

48 IMPULSNA ELEKTRONIKASlika 1.57:što odgovara ekstremnim vrednostima napona u tački C astabilnog multivibratora, <strong>za</strong>čiju je reali<strong>za</strong>ciju potrebna invertujuća karakteristika dobijena ubacivanjem invertoraizmed - u tačaka B i D.Neka je u t = 0 − , napon tačke B visokTada jeU B = V (1) = 5V. (1.283)U D = V (0) = 0V, (1.284)pa se konden<strong>za</strong>tor C prazni a napon u tački C opada i dostiže donji prag okidanjakomparatoraU C = V ′′ = 1, 5V, (1.285)kada jeU A = V T = 2, 5V. (1.286)Posle promene stanja na izlazu komparatora je u t = 0 + :U D = V (1) = 5VU C = U C (0 − ) = 1, 5VU B = V (0) = 0V(1.287)a skokovita promena napona iz tačke B i<strong>za</strong>ziva trenutnu promenu na ulazu <strong>prvog</strong>invertoraU A (0 + ) =R 2R 1U C + U B = 1, 07V (1.288)R 1 + R 2 R 1 + R 2tako da ovaj napon održava ni<strong>za</strong>k napon u tački B.Ulazna otpornost CMOS invertora je velika tako da se konden<strong>za</strong>tor C puni prekoekvivalentne otpornostiR ek = (R 1 + R 2 ) ‖ R 3 = R 3(R 1 + R 2 )R 1 + R 2 + R 3= 4.88K ≈ 5K (1.289)ako uzmemo u obzir da je otpornost R 3 mnogo manja od R 1 i R 2 . Napon na konden<strong>za</strong>toruraste i teži ka vrednosti

LOGIČKA KOLA 49V ek1 =R 1 + R 2R 1 + R 2 + R 3U D = 4, 88V ≈ 5V (1.290)sve dok ne dod - e do okidanja naponskog komparatora, što se dešava kada jeU C (T − 1 ) = V ′ = 3, 5V. (1.291)S obzirom da se <strong>za</strong> napon tačke C u ovom kvazistabilnom stanju može pisatiU C (t) = V ek1 − [V ek1 − U C (0 + )]e −t/τ (1.292)gde je τ = CR ek = 5µs, <strong>za</strong> trajanje kvazistabilnog stanja se dobijaT 1 = τ ln V ek1 − U C (0 + )V ek1 − V ′= 4, 24µs(1.293)Na početku drugog kvazistabilnogstanja jeU B (T + 1 ) = V (1)U D (T + 1 ) = V (0)U C (T + 1 ) = U C(T − 1) = 3, 5V(1.294)Slika 1.58:iU A (T 1 + ) = R 2R 1U C + U B = 3, 93V (1.295)R 1 + R 2 R 1 + R 2I sada je ekvivalentna otpornost <strong>za</strong> pražnjenje konden<strong>za</strong>toraa pri pražnjenju napon teži ka vrednostiV ek2 =R ek = (R 1 + R 2 ) ‖ R 3 ≈ 5K, (1.296)R 3R 1 + R 2 + R 3U B = 0, 12V ≈ 0V, (1.297)tako da se <strong>za</strong> trajanje drugog kvazistabilnog stanja dobijaT 2 = τ ln V ek2 − U C (T + 1 )V ek2 − V ′′ = 4, 24µs (1.298)

50 IMPULSNA ELEKTRONIKA1.15 Astabilni multivibrator prika<strong>za</strong>n na slici 1.59 realizovan je CMOS invertorimasa idealnim <strong>za</strong>štitnim diodama na ulazu.a) Za R 2 = 250K i R 1 = 500K izračunati i nacrtati talasne oblike napona utačkama A, B, C i D.b) Odrediti koji uslov treba da <strong>za</strong>dovolji odnos vrednosti otpornika R 1 /R 2 da biu kolu postojale oscilacije a da ne dolazi do provod - enja <strong>za</strong>štitnih dioda ula<strong>za</strong>.V dd = V (1) = 5V , V (0) = 0V , V T = 0, 4V dd , V d = 0V , C = 2nF i R = 12K(R

LOGIČKA KOLA 51U Dmin = V ′ − V dd = (1 + R 2R 1)V T − V dd = −2V (1.303)Korišćenjem izra<strong>za</strong> 1.300 dobijamoU A (0 + ) =R 1R 2U Dmin + U C = V T + R 2 − R 1V dd = 0, 33V (1.304)R 1 + R 2 R 1 + R 2 R 1 + R 2Na slici 1.60 je dato kolo punjenja konden<strong>za</strong>tora.Vremenska konstanta punjenjaiznosiτ = C(R ‖ (R 1 + R 2 )) ≈ CR = 24µs,(1.305)a ekvivalentni generatorV ek1 = 5V. (1.306)Slika 1.60:Napon tačke D rasteU D (t) = V ek1 − [V ek1 − U D (0 + )]e −t/τ (1.307)sve dok napon u tački A ne dostigne napon praga invertora V T , tako da na kraju<strong>prvog</strong> kvazistabilnog perioda napon u tački D iznosi (iz izra<strong>za</strong> 1.300)U D (T − 1 ) = V ′′ = (1 + R 2R 1)V T − R 2R 1V dd = 0, 5V. (1.308)Iz izra<strong>za</strong> 1.307 se <strong>za</strong> trajanje <strong>prvog</strong> kvazistabilnog stanja dobijaT 1 = τ ln V ek1 − U D (0 + ) 5 − (−2)V ek1 − U D (T1 − = 24µs ln = 10, 6µs (1.309)) 5 − 0, 5Napon na konden<strong>za</strong>toru u ovom trenutku iznosiU k (T 1 ) = U D − U B = 0, 5V. (1.310)U drugom kvazistabilnom stanju naponi u tačkama B i C imaju vrednostU B = V (1)U C = V (0).i(1.311)Pozitivni skok napona u tački B, prenešen preko konden<strong>za</strong>tora C, i<strong>za</strong>ziva skoknapona u tački D na maksimalnu vrednostodnosnoU D (T + 1 ) = U B + U k = U Dmax = (1 + R 2R 1)V T + R 1 − R 2R 1V dd = 5, 5V, (1.312)U A (T + 1 ) = U A max=R 1R 1 + R 2U D = V T + R 1 − R 2R 1 + R 2V dd = 3, 67V. (1.313)

52 IMPULSNA ELEKTRONIKATrajanje drugog kvazistabilnogstanja definiše pražnjenje konden<strong>za</strong>toradok napon tačke A ne opadnena napon praga V T , odnosno naponu tački D ne dostigne 3V kako jeodred - eno u trenutku t = 0 − , takoda se dobijaT 2 = τ ln V ek2 − U D (T 1 + )V ek2 − U D (T2 − )0 − (5, 5)= 24µs ln = 14, 55µs0 − 3(1.314)gde je V ek2 = 0V s obzirom da jeu ovom kvazistabilnom stanju napontačke C na nivou logičke nule. Slika 1.61:Talasni oblici napona u svim tačkama kola dati su na slici 1.61.b) Da se ne bi uključivala <strong>za</strong>štitna dioda na ulazu invertora čiji je ulaz ve<strong>za</strong>n <strong>za</strong>tačku A, potrebno je da minimalna vrednost napona u ovoj tački, data izrazom 1.304,bude veća od −V d tj. od nule, odakle se <strong>za</strong> odnos R 2 /R 1 dobijaR 2R 1≥ 1 − V T /V dd1 + V T /V dd= 3 7(1.315)Slično, na početku drugog kvazistabilnog stanja, da ne bi dolazilo do uključivanja<strong>za</strong>štitne diode ve<strong>za</strong>ne <strong>za</strong> izvor napajnja potrebno je da maksimalna vrednost naponau tački A bude ograničena tj.U Amax ≤ V dd + V d . (1.316)Rešavanjem ove nejednakosti dobija se opet isti uslov dat izrazom 1.315. Maksimalnapromena napona u tački A oko napona praga V T iznosi∆U A = V T − U Amin = U Amax − V T = R 1 − R 2R 1 + R 2V dd ≥ 0 (1.317)i treba da bude veća od nule da bi postojale oscilacije u kolu, odakle se dobija uslovR 1 > R 2 , odnosno uslov <strong>za</strong> postojanje oscilacija bez uključivanja <strong>za</strong>štitnih dioda naulazu <strong>prvog</strong> invertora postoje37 ≤ R 2< 1. (1.318)R 11.16 Za monostabilni multivibrator prika<strong>za</strong>n na slici 1.62, realizovan CMOS NILIkolima sa idealizovanom prenosnom karakteristikom, čiji je napon praga V T i sa idealnim<strong>za</strong>štitinim diodama na ulazu,

LOGIČKA KOLA 53a) nacrtati talasne oblike napona u tačkama A, B, C i na izlazu kola.b) Za koliko se menja trajanje izlaznog impulsa ako napon praga može da imavrednosti iz opsega V T = 0, 3V dd − 0, 7V dd <strong>za</strong> C 2 = C = 5nF i C 2 = 0.V dd = V (1) = 5V , V (0) = 0V , V T = V dd /2, V d = 0V , R=10K i C = C 2 = 5nF .Slika 1.62:Rešenje:a) Pre pojave okidnog impulsa struje kroz konden<strong>za</strong>tore ne teku, tako da jeU ul (0 − ) = 0VU B (0 − ) = V dd = 5VU A (0 − ) = V (0) = 0V,(1.319)zbog čega ne vodi dioda D. Konden<strong>za</strong>tor C 2 se ispraznio kroz otpornik RU C (0 − ) = U k2 = 0V, (1.320)što na izlazu NILI kola dajeU iz (0 − ) = V (1) = 5V i(1.321)U k1 = U B − U iz = 0V.Pozitivni ulazni impulsU ul (0 + ) = 5V (1.322)menja stanje na izlazu NILI kolaU iz (0 + ) = V (0) = 0V (1.323)a kako se napon na konden<strong>za</strong>toru ne menja naglo, dolazi do pada napona u tački BU B (0 + ) = U iz + U k1 = 0V, (1.324)tako da jeU A (0 + ) = V (1) = 5V, (1.325)

54 IMPULSNA ELEKTRONIKAzbog čega provede dioda D, kroz koju se sa izla<strong>za</strong> NILI kola (male izlazne otpornosti)brzo puni konden<strong>za</strong>tor C 2 na vrednostU C (0 + ) = U A − V d ≈ 5V. (1.326)Konden<strong>za</strong>tor C 2 je pun i održava logičku nulu na izlazu kola tako da ulazni impulsmože da se <strong>za</strong>vrši. Za t > 0, puni se konden<strong>za</strong>tor C sa vremenskom konstantomτ = RC a napon tačke B raste ka vrednostiU B (∞) = V dd (1.327)dok ne dostigne vrednost napona praga, U B (T 1 ) = V T . Iz izra<strong>za</strong>U B (t) = U B (∞) + [U B (0 + ) − U B (∞)]e −t/τ (1.328)se <strong>za</strong> trajanje kvazistabilnog perioda dobijaT 1 = τ lnZa t > T 1 jeV ddV dd − V T(1.329)U A = V (0) = 0V. (1.330)Dioda D je inverzno polarisana jer jekonden<strong>za</strong>tor C 2 pun a anoda se nalazina nivou logičke nule. Konden<strong>za</strong>torC 2 se prazni kroz otpornik R, ali dokje napon veći od V T na izlazu kola jei daljeU iz = V (0) = 0V, (1.331)pa se nastavlja punjenje konden<strong>za</strong>toraC. Napon tačke C opadaSlika 1.63:U C (t) = U C (T 1 )e −t/τ1 ≈ V dd e −t/τ1 (1.332)i posle vremena t = T 2 dostiže vrednost V T . Iz izra<strong>za</strong> 1.332 se dobijaT 2 = τ 1 ln V ddV Ta napon tačke B dostigao je vrednost= RC ln V ddV T(1.333)U B (T 1 + T 2 ) = V dd + [V dd − U B (0 + )]e −(T1+T2)/τ > V T (1.334)Ukupno trajanje impulsa na izlazu kola iznosiT = T 1 + T 2 = τ lnV dd+ τ 1 ln V ddVdd2= RC ln(1.335)V dd − V T V T (V dd − V T )V T

LOGIČKA KOLA 55Za t > T 1 + T 2 nastavlja se pražnjenje konden<strong>za</strong>tora C 2 a kako je napon na njemumanji od V T , na izlazu kola jeU iz = V (1) = 5V. (1.336)Skok napona sa izla<strong>za</strong> kola se kroz konden<strong>za</strong>tor C prenosi do tačke BU B (T 1 + T 2 ) = U iz + U k1= V (1) + U B (T 1 + T 2 ) > V dd(1.337)a kako je ova vrednost veća od napona napajanja, uključuje se <strong>za</strong>štitna dioda naulazu NILI kola kroz koju se konden<strong>za</strong>tor C brzo prazni a napon tačke B ograničavana vrednost napona napajanja V dd . Talasni oblici napona dati su na slici 1.63.b) Za slučaj C 2 = 0 je T 2 = 0, odnosno T = T 1 . Iz izra<strong>za</strong> 1.329 i 1.333 se <strong>za</strong>trajanje generisanog izlaznog impulsa dobijaju vrednosti date u tabeli.C 2 = 5nF C 2 = 0V T T (µs) % T (µs) %0, 5V dd 69,4 0 34,7 00, 3V dd 78,03 12,4 17,83 48,60, 7V dd 78,03 12,4 60,1 73,5Primećujemo da konden<strong>za</strong>tor C 2 smanjuje uticaj tolerancije praga V T na trajanjeizlaznog impulsa.1.17 Na slici 1.64 je prika<strong>za</strong>n astabilni multivibrator realizovan pomoću idealnihCMOS invertora bez <strong>za</strong>štitnih dioda na ulazu.a) Izračunati i nacrtati vremenske dijagrame napona u tačkama A, B i C <strong>za</strong>I = 5mA.b)Odrediti trajanja kvazistabilnih stanja <strong>za</strong> slučaj da struja I strujnog izvora imamaksimalnu dozvoljenu vrednost.Poznato je: V dd = V (1) = 5V , V (0) = 0V , V T = V (1)/2, V d = 0, 5V , R d = 100Ωi C = 3, 3nF .Rešenje:a) Neka jeU B (0 − ) = V (1) ⇒ U A ≥ V TU C (0 − ) = V (0).(1.338)Tada dioda ne vodi a struja I strujnog izvora teče kroz konden<strong>za</strong>tor C. Napontačke A opada dostižući napon praga,U A (0 − ) = V T , (1.339)

56 IMPULSNA ELEKTRONIKASlika 1.64:tako da je napon na konden<strong>za</strong>toruU k (0) = U A − U B = −2, 5V. (1.340)Sada se kolo nalazi na početku kvazistabilnog stanja u kome jeU B (0 + ) = V (0) = 0VU C (0 + ) = V (1) = 5V(1.341)zbog čega sada vodi dioda. Početni napon tačke A iznosiU A (0 + ) = U B + U k = −2, 5V. (1.342)Konden<strong>za</strong>tor se puni tako da napon utački A rasteU A (t) = V ek1 − [V ek1 − U A (0 + )]e −t/τ= 4 − 6, 5e −t/τ (1.343)Na slici 1.65 je dato ekvivalentno kolo punjenjakonden<strong>za</strong>tora, gde jeR ek = R dV ek1 = U C − V d − R d · I = 4V.(1.344)Napon tačke A raste ka asimptotskojvrednosti V ek1 sve dok na kraju kvazistabilnogstanja ne dostigne vrednost naponapraga, odakle se <strong>za</strong> trajanje <strong>prvog</strong>kvazistabilnog stanja dobijaSlika 1.65:T 1 = τ ln V ek1 − U A (0 + )V ek1 − U A (T1 − ) = CR d ln 6, 5 = 484ns (1.345)1, 5

LOGIČKA KOLA 57U trenutku kada nastupa promena u kolunapon na konden<strong>za</strong>toru dostiže vrednostU k (T 1 ) = U A − U B = 2, 5V. (1.346)U drugom kvazistabilnom stanju jeU B = V (1) = 5VU C = V (0) = 0V,(1.347) Slika 1.66:tako da dioda ne može da provodi a napon tačke A ima početnu vrednostU A (T + 1 ) = U B + U k = 7, 5V. (1.348)Sada struja strujnog izvora teče kroz konden<strong>za</strong>tor, kako je dato na slici 1.66, takoda se napon tačke A menja linearno sa vremenomU A (t) = U B + U k (t) = U B + U k (T 1 ) − I C t = U A(T + 1 ) − I C t (1.349)sve dok se zbog opadanja ne izjednači sa naponom praga,U A (T − 2 ) = V T , (1.350)kada opet nastupa promena na izlazima invertora.drugog kvazistabilnog stanja dobijaIz izra<strong>za</strong> 1.349 se <strong>za</strong> trajanjeT 2 = [U A(T + 1 ) − U A(T − 2 )]CIb) Od vrednosti struje I strujnogizvora <strong>za</strong>visi samo trajanje kvazistabilnogstanja T 2 . Ova struja prazni konden<strong>za</strong>tori sigurno će napon tačke A u jednomtrenutku dostići napon praga. Med - utim,da bi u kolu postojale oscilacije potrebnoje da se u prvom kvazistabilnom stanjukonden<strong>za</strong>tor puni i da se dostigne naponV T . Kako pri punjenju napon težika vrednosti V ek1 uslov <strong>za</strong> postojanje oscilacijase svodi na=[7, 5V − 2, 5V ]C5mA= 3, 3µs (1.351)Za V ek1 = V T se iz uslovaV ek1 ≥ V T . (1.352)Slika 1.67:V (1) − V d − R d I max = V T (1.353)dobija maksimalna vrednost struje strujnog izvora <strong>za</strong> koju i dalje postoje oscilacije ukoluI max = 20mA. (1.354)

58 IMPULSNA ELEKTRONIKAZa I → I max <strong>za</strong> trajanja kvazistabilnih stanja se dobijaju vrednostiT 1 → ∞ i T 2 = 5CI max= 825ns. (1.355)1.18 Za "retrigerable"monostabilni multivibrator sa slike 1.68 nacrtati talasne oblikenapona u svim tačkama kola (A, B i C) naznačivši sve njihove karakterističnevrednosti, ako se kolo okida impulsima logičke nule trajanja T i = 0, 9µs frekvencijea) f 1 = 10kHZ ib) f 2 = 20kHZ (f = 1/T ).Smatrati da CMOS NI kola imaju idealne <strong>za</strong>štitne diode ula<strong>za</strong> i prenosnu karakteristikusa pragom promene V T .c) Odrediti minimalno trajanje okidnog impulsa T i kojim se kolo uvek vraća napočetak kvazistabilnog stanja.Poznato je: V dd = V (1) = 5V , V (0) = 0V , V T = V (1)/2, V d = V ces = 0V ,V be = V bes = 0, 6V , β = 50, C = 3nF , R = 40K i R b = 22K.Slika 1.68:Rešenje:a) U stabilnom stanju na ulazu kola je prisutan naponU ul = 5V (1.356)tako da PNP tranzistor ne može da vodi. Kroz konden<strong>za</strong>tor ne teče struja a naponiu karakterističnim tačkama kola imaju vrednostiU A (0 − ) = 0V ⇒ U C (0 − ) = V (1) = 5VU B (0 − ) = V (0) = 0VU k (0 − ) = U A − U B = 0V.(1.357)Zbog pojave okidnog impulsaprovede tranzistor T . S obzirom da je <strong>za</strong>dovoljen uslovU ul = V (0) = 0V (1.358)βR > R b (1.359)

LOGIČKA KOLA 59tranzistor radi u <strong>za</strong>sićenju sprečavajući punjenje konden<strong>za</strong>tora. Tako <strong>za</strong> 0 < t T i , kada se <strong>za</strong>vrši okidni impuls, na ulaz kola opet je doveden napon logičkejedinice zbog čega se <strong>za</strong>koči tranzistor T . Logička nula iz tačke C održavaU B = V (1) = 5V, (1.361)a zbog pražnjenja konden<strong>za</strong>tora C napon u tački A opada ka nuliU A (t) = U A (T i )e −t/τ = V (1)e −t/τ τ = RC = 120µs (1.362)Impuls koji se generiše u tački C se<strong>za</strong>vršava kada napon tačke A dostignenapon praga V T odakle se iz izra<strong>za</strong>1.362 <strong>za</strong> trajanje kvazistabilnog stanjadobijaT 1 = τ ln V (1)V T= τ ln 2 = 83.2µs(1.363)Slika 1.69:tako da u trenutku t = T − 1naponi u kolu imaju istu vrednostU B (T1 − ) = V (1) = 5VU A (T1 − ) = V T = 2, 5VU C (T1 − ) = V (0) = 0VU k (T1 − ) = U A − U B = −2, 5V.(1.364)Napon niži od V T na ulazu drugog NI kola postavlja logičku jedinicu na njegovizlaz,U C (T 1 + ) = V (1) = 5VU B (T 1 + ) = V (0) = 0V (1.365)odnosno logičku nulu u tački B. Sada je napon u tački A negativanU A (T + 1 ) = U B + U k = −2, 5V (1.366)zbog čega provede <strong>za</strong>štitna dioda na ulazu drugog NI kola ograničavajući ulazni naponna vrednostU A (T ++1 ) = −V d = 0V. (1.367)

60 IMPULSNA ELEKTRONIKAKonden<strong>za</strong>tor se kroz izlaz <strong>prvog</strong> NI kola i <strong>za</strong>štitnu diodu, zbog male vremenskekonstanteτ 1 = C(R iz−NI + R d ) → 0 (1.368)velikom strujom prepuni na novu vrednostU k (T ++1 ) = U A (T ++1 ) − U B (T ++1 ) = 0V. (1.369)Na ovaj način kolo se brzo vraća u stabilno stanje i spremno je <strong>za</strong> sledeći okidni impulskoji se javlja <strong>za</strong> T = 1/f = 100µs > T 1 , kako je prika<strong>za</strong>no na slici 1.69.b) Ako se na ulaz kola dovedu okidniimpulsi frekvencije f = 20KHz ⇒T = 1/f = 50µs, dolaziće do ponovnogokidanja monostabilnog multivibratorapre nego je <strong>za</strong>vršenokvazistabilno stanje (T 1 = 83, 2µs >50µs). Pojavom novog okidnog impulsa,pre nego je napon tačke Adostigao napon praga, uključivaće setranzistor T , koji će prazniti konden<strong>za</strong>tor,i napon dovoditi na vrednostkoju je imao i na početku kvazistabilnogstanja pri čemu nema promenena izlazu NI kola tj. produžava se trajanjegenerisanog impulsa u tački C,što je prika<strong>za</strong>no na slici 1.70.Slika 1.70:U trenutku kada stiže naredni okidni impuls napon tačke A dostiže vrednostU A (t = 50µs) = 5e −(T −T i)/τ = 5e −49,1/120 = 3, 32V. (1.370)c) Naravno, retrigerovanje će biti uspešno ako, nebitno od vrednosti dostignutognapona na konden<strong>za</strong>toru, tranzistor T uvek uspe da dovede napon tačke A navrednost sa početka kvazistabilnog stanja. Kritičan slučaj se ima kada je napon nakonden<strong>za</strong>toru najveći a to je pred kraj kvazistabilnog stanja, kada jeU Amin = V + T = 2, 5V tj. U kmax = V − T= 2, 5V. (1.371)Zbog punog konden<strong>za</strong>tora je| V ce |> V ces , (1.372)tako da je tranzistor u aktivnom režimu sa kolektorskom strujomEkvivalentni generator <strong>za</strong> kolo sa slike 1.71 iznosiI c = βI b = β V (1) − V beR b= 10mA. (1.373)V ek = RI c = 400V, (1.374)

LOGIČKA KOLA 61a napon tačke A se menja po <strong>za</strong>konuU A (t) = V ek − [V ek − U Amin ]e −t/τ(1.375)Iz uslova da je U A (t = T imin ) = V (1),tj. da tranzistor uspešno ispraznikonden<strong>za</strong>tor do kraja čime se napontačke A vraća na početnu vrednost(logičke jedinice) <strong>za</strong> minimalno trajanjeokidnog impulsa se dobijaSlika 1.71:T imin = τ ln V ek − 2, 5V ek − 5= 0, 76µs (1.376)1.19 Na slici 1.72 prika<strong>za</strong>n je retrigerabilni monostabilni multivibrator realizovanCMOS invertorima bez <strong>za</strong>štitnih dioda na ulazu. Izračunati i nacrtati talasne oblikenapona u tačkama A i B ako se na ulaz kola dovode okidni impulsi trajanja logičkenule T i = 1µs, frekvencijea) f = 1/T = 60KHzb) f = 1/T = 120KHz.Poznato je: V cc = V (1) = 5V , V (0) = 0V , V T = V (1)/2, V d = 0, 5V , R d = 50Ω,R = 20K i C = 1nF . Napon Šotki diode iznosi V dš = 0V .Slika 1.72:Rešenje:a) Pre dovod - enja okidnog impulsa, u stabilnom stanju, katoda diode D 1 je ve<strong>za</strong>nana napon napajanja tako da ne provodi. Kroz otpornik R struja ne teče (u stabilnomstanju struja kroz konden<strong>za</strong>tor uvek je jednaka nuli) pa jeU A (0 − ) = V cc = 5V (1.377)

62 IMPULSNA ELEKTRONIKAa na izlazu drugog invertora jeU B (0 − ) = V (1) = 5V, (1.378)tako da napon na konden<strong>za</strong>toru iznosiU k (0 − ) = U A − U B = 0V. (1.379)Zbog pojave niskog napona na ulazukolaU ul = 0V, (1.380)Slika 1.73:provede dioda D 1 . Napon na ulazu <strong>prvog</strong>invertora jednak je naponu vod - enjadiode, što i<strong>za</strong>ziva promenu na izlazukolaU B (0 + ) = V (0) = 0V, (1.381)koje se sada nalazi u kvazistabilnomstanju. Otpornici u kolu ograničavajuvrednost struje i time sprečavaju naglupromenu napona na konden<strong>za</strong>toruU k (0 + ) = U k (0 − ), (1.382)Slika 1.74:pa se <strong>za</strong> početni napon tačke A dobijaU A (0 + ) = U B + U k = 0V. (1.383)Kolo punjenja konden<strong>za</strong>tora je dato na slici 1.73, gde jeR ek =RR d= 49, 9ΩR + R dV ek =R dRV cc + U D = 0, 51VR + R d R + R dVremenska konstanta punjenja iznosi(1.384)τ 1 = CR ek = 49, 9ns. (1.385)Primećujemo da je 5τ 1 < T i , što znači da će konden<strong>za</strong>tor uspeti da se napuni dokraja, kada napon dostiže vrednostU A = U k (t = 5τ 1 ) = V ek = 0, 51V (1.386)a struja u kolu se svodi na nulu.U trenutku t = T i nastupa promena na ulazu kola tj. <strong>za</strong>vršava se okidni impuls.Zbog visokog napona na katodi dioda D 1 prestaje da vodi. Konden<strong>za</strong>tor sprečavanagle promene na ulazu <strong>prvog</strong> invertora, tako da je

LOGIČKA KOLA 63Sada su stvoreni uslovi <strong>za</strong> punjenje konden<strong>za</strong>torapreko otpornika R i izvoranapajanja V cc . Konden<strong>za</strong>tor se punipreko provodnog n-kanalnog FET-a naizlazu invertora, kao na slici 1.74.Kraj kvazistabilnog stanja je odred - endosti<strong>za</strong>njem praga promene V T naulazu <strong>prvog</strong> invertora odakle se dobijaU A (T + i ) = U A(T − i ) = 0, 51V < V TU B (T + i ) = V (0). (1.387)T 1 = CR ln V cc − U A (0 + )V cc − V T= 11, 7µs(1.388) Slika 1.75:Izlazni impuls u tački B ima ukupnotrajanjeT KS = T i + T 1 = 12, 7µs. (1.389)Povratkom u stabilno stanje izlazni naponje opet visok,U B (T i + T + 1) = V (1). (1.390)Napon u tački A ima najpre skok navrednostU A (T i + T + 1 ) = U B + U k = 7, 5V.(1.391)Slika 1.76:Iako je napon na katodi diode D 1 visok tj. 5V, napon na anodi je dovoljno visok daona provede tako da se preko male ekvivalentne otpornosti R ek = 49, 9Ω, i p-kanalnogFET-a na izlazu drugog invertora konden<strong>za</strong>tor brzo isprazni a napon tačke A svodina vrednost napona napajanja, kada se gasi dioda D 1 .I<strong>za</strong> ovoga su naponi u svim tačkama kola stabilni kao i u trenutku t = 0 − i dogenerisanja novog impulsa logičke nule na izlazu kola dolazi tek pojavom novog okidnogimpulsa na ulazu kola. Ovo je upravo slučaj <strong>za</strong> f = 60KHZ, kada ulazni okidniimpulsi imaju perioduT = 1 = 16, 67µs (1.392)fa odgovarajući talasni oblici napona su prika<strong>za</strong>ni na slici 1.75.b) Ako se frekvencija ulaznih impulsa poveća na f = 120KHz, perioda iznosiT = 1 = 8, 33µs (1.393)f

64 IMPULSNA ELEKTRONIKAi kraća je od trajanja kvazistabilnog stanja. Sada dolazi do retrigerovanja kola tj. pre<strong>za</strong>vršetka kvazistabilnog stanja javlja se novi okidni impuls. Talasni oblici napona <strong>za</strong>ovaj slučaj su dati na slici 1.76. Sa slike vidimo da novi okidni impuls na ulaz kolastiže pre nego napon na konden<strong>za</strong>toru dostigne napon praga NI kola zbog čega nemapromene na izlazu u tački B.Sada se zbog pojave okidnogimpulsa stiču uslovi da provededioda D 1 , med - utim, kako je naizlazu drugog invertora napon ni<strong>za</strong>ksada je uključen n-kanalni FET.Struja pražnjenja konden<strong>za</strong>toraima suprotan smer od struje drejnaFET-a, kako je prika<strong>za</strong>no na slici1.77. Konden<strong>za</strong>tor bi se isprazniouspešno jer bi provela diodapodloga-drejn. Slika 1.77:Da se ovo ne bi dešavalo na izlaz kola se vezuje Šotki dioda koja ima napon vod - enjaniži od p-n spoja, tako da se konden<strong>za</strong>tor u ovom kolu prazni, kod retrigerovanja, krozŠotki diodu. Na ovaj način se napon na konden<strong>za</strong>toru vraća na vrednost 0,51V, kojuje imao i na početku kvazistabilnog perioda a izlazni impuls se produžava.1.20 Astabilni multivibrator realizovan CMOS invertorom prika<strong>za</strong>n je na slici 1.78.Prenosna karakteristika invertora data je na slici 1.79. Izračunati i nacrtati talasneoblike napona u tačkama A, B i C. V dd = 5V , V (1) = V dd , V (0) = 0V , R = 10K,R c = 1K, R b = 82K, C = 100nF , V be = V bes = 0, 6V , | V ces |= 0V i β = 50.Slika 1.78: Slika 1.79:Rešenje:Ako jeU A (0 − ) = V (0) = 0V (1.394)

LOGIČKA KOLA 65tranzistor ne vodi, te se kroz otpornik R i izlaz logičkog kola konden<strong>za</strong>tor C prazni.Pri opadanju napona na ulazu invertora (tačka B) sa prenosne karakteristike se vidida promena u kolu nastupa <strong>za</strong>U B (0 − ) = 1, 7V. (1.395)Kako tranzistor ne vodi, nema kolektorske struje niti pada napona na otporniku R c ,tako da jeU C (0 − ) = U B = 1, 7V. (1.396)Na početku drugog kvazistabilnog stanja naponi u kolu imaju sledeće vrednosti:U A (0 + ) = V (1) = 5V (1.397)a konden<strong>za</strong>tor sprečava nagle promene napona u tački B, tako da jeU B (0 + ) = U B (0 − ) = 1, 7V. (1.398)Spoj ba<strong>za</strong>-emitor tranzistora T sada je direktno polarisan i on vodi sa baznomstrujomtako da kolektorska struja ima vrednostI b = U A(0 + ) − V ebR b= 53, 66µA, (1.399)I c = βI b = 2, 68mA. (1.400)Slika 1.80:Ova struja stvara pad napona na otporniku R c zbog čega napon tačke C imavrednostTranzistor radi u aktivnom režimu jer jeU C (0 + ) = U B (0 + ) + R c I c = 3, 38V. (1.401)U ec = U A − U C = 1, 62V > V ces , (1.402)med - utim zbog punjenja konden<strong>za</strong>tora ovaj napon opada. Tranzistor je na granici<strong>za</strong>sićenja kada jeU ec = V ces = 0V, (1.403)

66 IMPULSNA ELEKTRONIKAodnosno <strong>za</strong>U B = U A − V ces − R c I c = 2, 32V, (1.404)što se dešava u trenutku t = T 1 . Ekvivalentno kolo <strong>za</strong> period 0 < t < T 1 dato je naslici 1.80, gde jeV ek1 = U A (0 + ) + RI c = 31, 8V. (1.405)Struja u kolu opadaI(t) = I 0 e −t/τ 1, (1.406)gde početna vrednost struje vremenska konstanta imaju vrednostiI 0 = V ek1 − U B (0 + )RS obzirom da je= 3, 01mA a τ 1 = RC = 1ms. (1.407)U B (t) = V ek1 − RI(t) = V ek1 − [V ek1 − U B (0 + )]e −t/τ 1(1.408)tranzistor stiže na granicu <strong>za</strong>sićenja posle vremenaT 1 = τ 1 ln V ek1 − U B (0 + )V ek1 − U B (T1 − = 20, 81µs (1.409))Slika 1.81:Za T 1 + T 2 > t > T 1 tranzistor je u <strong>za</strong>sićenju a ekvivalentno kolo punjenja konden<strong>za</strong>toraje prika<strong>za</strong>no na slici 1.81, gde jeV ek2 =R cU A +R U C = 5VR + R c R + R cR ek =RR c= 909, 1ΩR + R c(1.410)Punjenje konden<strong>za</strong>tora se nastavlja sve dok se u trenutku t = T 1 + T 2 ne dostignenaponU B = 3, 1V, (1.411)tako da se <strong>za</strong> trajanje dela <strong>prvog</strong> kvazistabilnog stanja u kome tranzistor radi u<strong>za</strong>sićenju dobija

LOGIČKA KOLA 67Slika 1.82:T 2 = CR ek ln V ek2 − U B (T 1 )5 − 2, 32= 90, 91 ln = 31, 3µs (1.412)V ek2 − U B (T 2 ) 5 − 3, 1kada nastupa promena u kolu posle koje jeU A (T + 2) = 0V, (1.413)a konden<strong>za</strong>tor sprečava promenu napona u tački B,U B (T 2 + ) = U C(T 2 + ) = U B(T2 − ) = 3, 1V, (1.414)a toliki je i napon tačke C, jer sada tranzistor ne vodi te ne postoji pad napona naotporniku R c . Konden<strong>za</strong>tor se prazni kroz otpornik R i izlaz logičkog kolaU B (t) = U B (T + 2 )e−t/τ 1(1.415)da bi na kraju drugog kvazistabilnog stanja dostigao vrednostU B (T − 3) = 1, 7V (1.416)odakle se dobijaT 3 = τ 1 ln U B(T 2 )= 600, 8µs (1.417)U B (T 3 )Talasni oblici napona u tačkama A, B i C prika<strong>za</strong>ni su na slici 1.82.1.21 U oscilatoru sa slike 1.83 upotrebljeni CMOS invertori imaju idealne <strong>za</strong>štitnediode ula<strong>za</strong> i prenosnu karakteristiku prika<strong>za</strong>nu na slici 1.84. Odrediti trajanjekvazistabilnih stanja i izračunati i nacrtati talasne oblike napona u tačkama A, Bi C. V cc = 5V , V d = V be = V bes = V ces = 0V , R b = 50K, R = 4K, β = 20 iC = 10nF .

68 IMPULSNA ELEKTRONIKASlika 1.83: Slika 1.84:Rešenje:Analizu kola krećemo od trenutka t = 0 − kada je na izlazu invertora u tački CnaponU C (0 − ) = V (1) = 5V. (1.418)Tranzistor T 2 vodi i svojom kolektorskom strujom prazni konden<strong>za</strong>tor tako da napontačke A opada. Kada se napon tačke A spusti ispod 3V vidimo, sa prenosne karakteristike1.84, da na izlazu <strong>prvog</strong> invertora u tački B napon počinje da raste dostigavšiu trenutku t = 0 − vrednostU B (0 − ) = 1VU A (0 − ) = 2, 5V<strong>za</strong>U k (0 − ) = U A − U C = −2, 5V,med - utim ovo nema uticaja na napon u tački C gde je sve do sada napon bioi(1.419)U C (0 − ) = 5V. (1.420)jer je napon na ulazu drugog invertora sve vreme manji od 2V. Dalji pad naponana ulazu <strong>prvog</strong> invertora i<strong>za</strong>ziva nagli skok napona na njegovom izlazu čime se stičuuslovi <strong>za</strong> naglu promenu napona u tački C jer je kružno pojačanje sistema veće odjedinice.Posle promene stanja u kolu naponi iznoseU C (0 + ) = V (0) = 0VU A (0 + ) = U C + U k = −2, 5V < −V d ,(1.421)tako da zbog negativnog napona na ulazu invertora provede <strong>za</strong>štitna dioda. S obziromda pretpostavljamo da su izlazna otpornost invertora kao i otpornost <strong>za</strong>štitne diodejednake nuli, velikom strujom kroz <strong>za</strong>štitnu diodu doći će do pražnjenja konden<strong>za</strong>toraC, tako da jei<strong>za</strong> čega se <strong>za</strong>štitna dioda gasi.U A (0 ++ ) = 0V = U k (0 ++ ) (1.422)

LOGIČKA KOLA 69Zbog niskog napona u tački C sadavodi tranzistor T 1 sa kolektorskomstrujomI c1 = V cc − V eb − U Cβ = 2mAR b(1.423)Parametri ekvivalentnog kola suR ek = R = 4K iV ek = U B + RI c1 = 13Vpa napon tačke A raste(1.424)Slika 1.85:U A (t) = V ek − [V ek − U A (0 ++ )]e −t/τ 1, (1.425)gde je τ 1 = R ek C = 40µs, sve dok ne dostigne 2V <strong>za</strong> šta je potrebno vremeZa t > T 1 radna tačka <strong>prvog</strong> invertoraje na prenosnoj karakteristici napotezu D−E, odnosno kolo tada imadiferencijalno pojačanje A d = −2, sobzirom da je jednačina prave kojaprolazi kroz tačke D i ET 1 = τ 1 ln V ek − U A (0++)V ek − U A (T1 − = 6, 68µs (1.426))U iz = U B = 9 − 2U ul = 9 − 2U A ,(1.427)tako da se sa slike 1.86 može odreditiekvivalentna otpornostSa slike 1.85 vidimo da jeR ek1 = R d = U 0J 0=U 0U 0 −A d U 0RSlika 1.86:= R1 − A d= R 3(1.428)na osnovu čega se dobijaU A (∞) = U B (∞) + RI c1 = 9 − 2U A (∞) + RI c1 (1.429)U A (∞) = 3 + RI c13Kako se napon tačke A sada menja po <strong>za</strong>konu= 17 V. (1.430)3U A (t) = U A (∞) − [U A (∞) − U A (T 1 )]e −t/τ 2(1.431)

70 IMPULSNA ELEKTRONIKAgde je τ 2 = R d C = 13, 33µs, a promena u kolu nastupa kada napon tačke A dostignevrednost napona pragadobija seU A (t = T 1 + T 2 ) = 2, 5V (1.432)T 2 = R d C lnKvazistabilno stanje u kome je napontačke C ni<strong>za</strong>k ima trajanjeT KS1 = T 1 + T 2 = 8, 63µs. (1.434)U A (∞) − U A (T 1 )= 1, 95µs (1.433)U A (∞) − U A (T 1 + T 2 )I<strong>za</strong> toga nastupa regenerativan proces,s obzirom da je kružno pojačanjesistema veće od jedinice, posle čegaje napon tačke C visok, pa voditranzistor T 2 . Kao i u trenutku t =0, i sada se skokovita promena naponaiz tačke C pojavljuje na ulazu<strong>prvog</strong> invertora, u tački A, zbogčega se uključuje <strong>za</strong>štitna dioda <strong>prvog</strong>invertora kroz koju se konden<strong>za</strong>torprazni a napon na njegovomulazu biva ograničen na vrednostSlika 1.87:U A (T 1 + T ++2 ) = V cc . (1.435)Anali<strong>za</strong> kola u drugom kvazistabilnom stanju je slična, s tim da na slici 1.85 trebapromeniti smer struje strujnog izvora i stavitia u izrazu 1.87 U B menjati saU B = 0V (1.436)U B = 6 − 2U A (1.437)(što odgovara jednačini prave kroz tačke F i G), tako da se zbog identične kolektorskestruje tranzistora T 2 i simetrične prenosne karakteristike invertora, zbog čegaje dinamičko pojačanje na delu prenosne karakteristige F − G takod - eA d = −2, (1.438)dobija identično vreme <strong>za</strong> trajanje drugog kvazistabilnog stanja tj.T KS2 = T KS1 gde je T 3 = T 1 i T 4 = T 2 . (1.439)Talasni oblici napona u svim tačkama kola prika<strong>za</strong>ni su na slici 1.87, gde su uočljivaizobličenja napona u tački B pred kraj kvazistabilnih stanja a posledica su ne idealneprenosne karakteristike invertora.

LOGIČKA KOLA 711.22 Za Start/Stop astabilni multivibrator sa slike1.88, realizovanog CMOS NIkolima sa idealnim <strong>za</strong>štitnim diodama ula<strong>za</strong>, izračunati i nacrtati vremenske dijagramenapona u tačkama A, B, C i D pri promenama stanja na S/S ulazu.V dd = V (1) = 5V , V (0) = 0V , V T = V (1)/2, V d = 0V , C=10nF, R=10K i R 1 = 1M.Slika 1.88:jeRešenje:ZaS/S = V (0) = 0V (1.440)U C (0 − ) = V (1) = 5VU A (0 − ) = V (0) = 0Va oscilacije u kolu ne postoje, tako da je napon na konden<strong>za</strong>toru(1.441)U k (0 − ) = U B − U A = 5V, (1.442)jer zbog velike ulazne otpornosti CMOS kola ne teče struja kroz otpornike R i R 1tako da jeU B (0 − ) = U D (0 − ) = U C = 5V. (1.443)Kada se na ulaz S/S dovede napon logičke jedinice, NI kolo počinje da radi kaoinvertor napona u tački D. S obzirom da je u tački D prisutan napon logičke jedinice,na izlazu NI kola jeU C (0 + ) = V (0) = 0V, (1.444)zbog čega jeU A (0 + ) = V (1) = 5V. (1.445)Otpornici u kolu ograničavaju struju i tako onemogućavaju naglu (trenutnu) promenunapona na konden<strong>za</strong>toru pa jeU k (0 + ) = U k (0 − ) = 5VU B (0 + ) = U A + U k = 10V.a(1.446)

72 IMPULSNA ELEKTRONIKASlika 1.89:Napon na ulazu drugog NI kola je dovoljno visok da se uključi <strong>za</strong>štitna dioda nanjegovom ulazu, ograničavajući napon tačke D na vrednostU D (0 ++ ) = V dd + V d = 5V. (1.447)Dok <strong>za</strong>štitna dioda vodi, napon tačke D biće konstantan a konden<strong>za</strong>tor se praznipreko ekvivalentne otpornostiR ek = R ‖ R 1 = 9, 901K ≈ 10K (1.448)tako da napon tačke B opada od početne vrednosti 10V ka asimptotskoj vrednostiV ek1 =RR + R 1U D = 0, 05V ≈ 0V (1.449)U B (t) = V ek1 − [V ek1 − U B (0 + )]e −t/τ1 , τ 1 = CR ek ≈ 100µs (1.450)Zaštitna dioda se gasi kada jeI d = 0 ⇒ U B (T − 1 ) = U D(T − 1) = 5V (1.451)na osnovu čega se iz izra<strong>za</strong> 1.450 dobijaT 1 = τ 1 ln 0 − 100 − 5 = τ 1 ln 2 = 69, 3µs (1.452)Za t > T 1 <strong>za</strong>štitna dioda više ne vodi, kroz otpornik R 1 ne teče struja, takoda su naponi tačaka B i D identični. Sada se konden<strong>za</strong>tor nastavlja da prazni savremenskom konstantomτ 2 = CR = 100µs. (1.453)S obzirom da je R 1 ≫ R praktično smo pri pisanju izra<strong>za</strong> 1.450 <strong>za</strong>nemarili strujukroz R 1 , tako da se isti izraz može koristiti i <strong>za</strong> t > T 1 kada <strong>za</strong>štitna dioda ne vodi.Kvazistabilno stanje se <strong>za</strong>vršava kada, zbog pražnjenja konden<strong>za</strong>tora, napon na ulazuNI kola opadne na vrednost napona praga tj.U D (T − 2 ) = U B(T − 2 ) = V T = 2, 5V (1.454)

LOGIČKA KOLA 73odakle se iz izra<strong>za</strong> 1.450 dobijaa napon na konden<strong>za</strong>toru iznosiT 2 = τ 2 ln 0 − 10 = RC ln 4 = 138, 6µs (1.455)0 − 2, 5U k (T − 2 ) = U B − U A = 2, 5 − 5 = −2, 5V. (1.456)Kolo prelazi u drugo kvazistabilno stanje u kome jeU C = V (1) = 5VU A = V (0) = 0V,i(1.457)dok je napon tačke B na početku ovog kvazistabilnog stanja jednakU B (T + 2 ) = U A + U k = −2, 5V < −V d , (1.458)zbog čega provede <strong>za</strong>štitna dioda na ulazu NI kola koja je ve<strong>za</strong>na na masu ograničivšinapon tačke D na vrednostU D (T ++2 ) = −V d = 0V. (1.459)Vremenska konstanta punjenja konden<strong>za</strong>tora je τ 3 = τ 1 = CR ek a napon paste kavrednostiV ek2 =RR + R 1U D + R 1R + R 1U C = 0 + 4, 95 = 4, 95V ≈ 5V (1.460)Kada napon tačke B dostigne vrednostgasi se <strong>za</strong>štitna dioda na ulazu NI kola, posleU B (T − 3 ) = U D(T − 3 ) = −V d (1.461)T 3 = τ 3 ln V ek2 − (−2, 5)= 40, 5µs (1.462)V ek2 − (−U D )a konden<strong>za</strong>tor nastavlja punjenje samo kroz otpornik R dok napon na ulazu NI kolane dostigne napon praga čime se <strong>za</strong>vršava ovo kvazistabilno stanje posleT 4 = τ 2 ln5 − (−2, 5)5 − 2, 5= τ 2 ln 3 = 109, 9µs (1.463)Na kraju ovog kvazistabilnog stanja napon na konden<strong>za</strong>toru iznosiU k (T − 4 ) = U B − U A = 2, 5 − 0 = 2, 5V. (1.464)Na početku generisanja svakog sledećeg impulsa u tački A početni napon u tački BiznosiU B (T + 4 ) = U A + U k = 5 + 2, 5 = 7, 5V, (1.465)a ne 10V kao u slučaju <strong>prvog</strong> generisanog impulsa, tako da <strong>za</strong>štitna dioda vodi

74 IMPULSNA ELEKTRONIKAT 5 = τ 1 ln 0 − 7, 50 − 5 = τ 1 ln 1, 5 = 40, 5µs (1.466)umesto 69, 3µs, koliko je vodila dok se generisao prvi izlazni impuls. Generisanjeimpulsa prestaje, a naponi u svim tačkama se vraćaju na vrednosti koje su imali ustabilnom stanju, kada se na ulaz S/S dovede napon logičke nule.1.23 Na slici 1.90 je dat izrazito nesimetričan astabilni multivibrator realizovanCMOS NI kolima. Odrediti odnos trajanja kvazistabilnih perioda i izračunati i nacrtatitalasne oblike napona u tačkama A, B i C smatrajućida kola imaju idealne <strong>za</strong>štitnediode ula<strong>za</strong>. Parametri kola su: V dd = 5V , V (1) = V dd , V (0) = 0V , V T = V dd /2,V d = 0V , A = 250µA/V 2 , | V T p |= 1V , R = 50K i C = 5nF .Slika 1.90:Rešenje:Počećemo analizu kola iz kvazistabilnog stanja u kome jeTada jeU B (0 − ) = V (1) = 5V. (1.467)U C (0 − ) = V (0) = 0V (1.468)a p-kanalni FET vodi i puni konden<strong>za</strong>tor, s obzirom da mu je napon gejt-sors veći odnapona praga| U GS |>| V T p | . (1.469)Napon tačke A raste do vrednostiU A (0 − ) = V T = 2, 5V = V k (0 − ) (1.470)kada nastupa promena u kolu. U narednom kvazistabilnom stanju jeU B (0 + ) = V (0) = 0V, (1.471)

LOGIČKA KOLA 75pa tranzistor više ne vodi jer jeU C (0 + ) = V (1) = 5V ⇔ U GS = 0V < V T p . (1.472)Napon u tački A je sada veći od napona napajanjaU A (0 + ) = U C + U k = 7, 5V > V dd (1.473)zbog čega provede <strong>za</strong>štitna dioda na ulazu NI kola (uključila bi se i dioda drejnpodlogaFET-a) ograničivši napon na vrednost napona napajanjatako da se konden<strong>za</strong>tor isprazni tj.Vreme pražnjenja <strong>za</strong>nemarujemo jer jeU A (0 ++ ) = V dd = 5V, (1.474)U k (0 ++ ) = 0V = U A − U C . (1.475)τ pr = C[R iz−NI + (R iz−NI + R) ‖ R d ] → 0, (1.476)posle čega se <strong>za</strong>štitna dioda gasi. Pad napona tačke A i pražnjenje konden<strong>za</strong>torase nastavlja kroz otpornik R i izlaz izlaznog NI kola sve dok se napon ne spusti navrednostU A (T1 − ) = V T = 2, 5V, (1.477)čime se <strong>za</strong> trajanje ovog kvazistabilnog stanja dobijaT 1 = RC ln U A(0 ++ )U A (T1 − = RC ln 2 = 173, 3µs (1.478))Napon na konden<strong>za</strong>toru dostiže vrednostU k (T − 1 ) = U A − U C = −2, 5V. (1.479)Posle promene stanja u kolu na početku drugog kvazistabilnog stanja jetako da FET vodi a zbog niskog napona tačke A,U B (T 1 + ) = V (1) = 5VU C (T 1 + ) = V (0) = 0V, (1.480)U A (T + 1 ) = U C + U k = −2, 5V < −V d , (1.481)uključuje se <strong>za</strong>štitna dioda ve<strong>za</strong>na na masu ograničavajući napon na vrednosta konden<strong>za</strong>tor se vrlo brzo isprazniU A (T ++1 ) = −V d = 0V (1.482)U k (T ++1 ) = U A − U C = 0V. (1.483)

76 IMPULSNA ELEKTRONIKAU prvom delu ovog kvazistabilnog stanja napon drejn-sors je dovoljno veliki daFET radi u aktivnom režimu (oblast <strong>za</strong>sićenih karakteristika) sa konstantnom strujomdrejnaI d = A(| U GS | − | V T p |) 2 = A(5 − 1) 2 = 4mA (1.484)Početna struja kroz otpornik R ima vrednostI R = (U C − U A )= 100µA (1.485)Ri ona opada sa rastom napona tačke A tako da je minimalno 40 puta manja od strujeFET-a i može biti <strong>za</strong>nemarena. U tom slučaju se konden<strong>za</strong>tor puni konstantnomstrujom drejna tj. napon se menja približno linearnoU A (t) = U A (T ++1 ) + I dC t = 8 · 105 t (1.486)sve dok je FET u oblasti <strong>za</strong>sićenihkarakteristika. Uslov rada u ovojoblasti je| U DS |≥| U GS | − | V T p | (1.487)tako da se konden<strong>za</strong>tor puni do vrednostiU SD = 5 − 1 = 4V⇒ U D = V dd − 4 = 1V(1.488)pa se iz izra<strong>za</strong> 1.486 dobija vreme punjenjaT ′ 2 = C I d=1= 1, 25µs8 · 10−5 (1.489)Slika 1.91:Za t > T ′ 2 FET je u omskoj oblasti (ne<strong>za</strong>sićenih karakteristika) gde je struja drejnapromenljiva zbog uticaja promenljivog napona U DS . Integralna jednačina koja opisujedalje punjenje konden<strong>za</strong>tora ima oblikU A (t) = 1 C+ A C∫ t0∫ t0I d (t)dt =| V T p |[2(V dd + V T p )(V dd − U A (t)) − (V dd − U A (t)) 2] dtkoju treba rešiti uz uslov da je <strong>za</strong> t = T ′′2 napon tačke A dostigao vrednost(1.490)U A (T ′′2 ) = V T = V dd /2 (1.491)

LOGIČKA KOLA 77krenuvši od početne vrednostiDiferenciranjem izra<strong>za</strong> 1.490 dobija seU A (0) =| V T p |= 1V. (1.492)U A ′ = 2A(V dd + V T p )[(V dd − U A ) − (V dd − U A ) 2 ]C2(V dd + V T p )(1.493)što posle sred - ivanja poprima oblik Rikatijeve diferencijalne jednačineU A ′ + 2V T pAC U A + A C U A 2 = AV dd(V dd + 2V T p )CLako se uočava partikularno rešenje, U ′ A = 0 (1.494)U A = V dd , (1.495)tako da se posle smeneU A = V dd + 1 z(1.496)dobija linearna diferencijalna jednačinačije rešenje ima oblikz ′ − 2A(V T p + V dd )z = A C C(1.497)z = e2A(V dd + V T p )t [∫ dd + V T p )ACC e−2A(V t ]C dt + C1(1.498)Smenom ovog rešenja u izraz 1.496 <strong>za</strong> U A i korišćenjem početnog uslova (U A (0) =1V ), odred - uje se konstanta C 1 , da bi se na kraju dobio izraz <strong>za</strong> napon tačke AU A (t) = V dd +odakle se iz uslova 1.491 sračunava11[ 2A(V dd + V T p )t ] (1.499)1 − 3e C2(V dd + V T p )T 2 ′′ C=2A(V dd + V T p ) ln 5V dd + 4V T p= 0, 84µs (1.500)3V ddtako da drugo kvazistabilno stanje trajeT 2 = T ′ 2 + T ′′2 = 2, 09µs (1.501)Odgovarajući talasni oblici napona su dati na slici 1.91.

78 IMPULSNA ELEKTRONIKASlika 1.92:1.24 Aktivni elementi generatora impulsa na slici 1.92 su dvoulazna NI CMOSlogička kola. Odrediti frekvenciju impulsa na izlazu ako se može uzeti da je naponpraga CMOS kola V T = V dd /2 i da su otpornosti uključenih tranzistora <strong>za</strong>nemarljive.Nacrtati impulsne oblike napona u obeleženim tačkama kola. Svi ulazi CMOS kolaimaju <strong>za</strong>štitne diode prema linijama <strong>za</strong> napajanje. Naponski nivoi logičke jedinice inule iznose V (1) = V dd i V (0) = 0V , respektivno.Rešenje:Prva dva CMOS NI kola iskorišćena su <strong>za</strong> reali<strong>za</strong>ciju astabilnog multivibratorai ovaj deo kola se može analizirati potpuno ne<strong>za</strong>visno od ostatka mreže. S obziromda je na ulaz <strong>prvog</strong> NI kola ve<strong>za</strong>n otpornik 10R, u vremenskom intervalu kada vodi<strong>za</strong>štitna dioda na ulazu ovog NI kola, ekvivalentna otpornost preko koje se praznikonden<strong>za</strong>tor iznosiR ek = 10R ‖ R ≈ R (1.502)tako da se može <strong>za</strong>nemariti uticaj vod - enja <strong>za</strong>štitne diode. Neka jeU B (0 − ) = V dd = 5V ⇒ U C (0 − ) = 0V. (1.503)Napon tačke A raste zbog punjenja konden<strong>za</strong>tora C preko izla<strong>za</strong> <strong>prvog</strong> NI kola idostiže vrednostU A (0 − ) = V T = U k (0 − ). (1.504)Daljom analizom mreže ćemo utvrditi da u trenucima kada nastupa promena u kolu,napon u tačkama D i E je visok tako da je na izlazu kola prisutna logička nula tj.U iz = U F (0 − ) = 0V. (1.505)Regenerativni proces, u kolu astabilnog multivibratora, obezbed - uje naglu promenunapona na izlazima NI kola tako da jeU B (0 + ) = V (0) = 0VU C (0 + ) = V dd .i(1.506)Kako se napon na konden<strong>za</strong>toru ne može naglo da promeni sada je

LOGIČKA KOLA 79U A (0 + ) = U C + U k = V dd + V T > V dd . (1.507)Napon na ulazu NI kola je dovoljno visok da vodi <strong>za</strong>štitna dioda sve dok se napontačke A ne spusti ispod vrednosti napona napajanja. Vremenski interval u kome <strong>za</strong>štitnadioda vodi nećemo analizirati posebno zbog velike vrednosti otpornika ve<strong>za</strong>nogna ulazu <strong>prvog</strong> NI kola. Zato možemo pisati da u toku celog kvazistabilnog stanjavažiU A (t) = U B − [U B − U A (0 + )]e −t/τ = (V dd + V T )e −t/τ (1.508)Prvo kvazistabilno stanje se <strong>za</strong>vršava kada napon tačke A opadne na vrednostnapona praga V T , tako da jeNa kraju kvazistabilnog stanja jeT 1 = τ ln V dd + V TV T= τ ln 3 ≈ 1, 1RC (1.509)U k (T − 1 ) = U A − U C = V T − V dd . (1.510)Da vidimo šta se dešavalo unutar ovog kvazistabilnog stanja na izlazu kola. Skoknapona iz tačke C se kroz konden<strong>za</strong>tor prenosi do tačke D, gde je napon već bio visok(veći od V T ).Zbog pozitivnog skoka naponauključiće se <strong>za</strong>štitnadioda na ulazu četvrtog NIkola i kroz nju se vrlo brzokonden<strong>za</strong>tor isprazni a napontačke D svodi na naponnapajanja. Sve ovo neutiče na izlazni napon kola.Med - utim, u trenutku t =0 + javlja se pad napona naizlazu trećeg NI kola. Padnapona se prenosi dalje i naizlaz diferencijatora (tačkaE), tako da se zbogU E (0 + ) = 0V (1.511)menja stanje na izlazu kolai sada jeU F (0 + ) = V dd = 5V.(1.512)Trajanje pozitivnog izlaznogimpulsa je odred - eno punjenjemkonden<strong>za</strong>tora Slika 1.93:

80 IMPULSNA ELEKTRONIKAV E (t) = V dd − [V dd − V E (0 + )]e −t/τ = V dd [1 − e −t/τ ] (1.513)dok napon na ulazu ne dostigne napon praga NI kola, tako da jeT i = τ lnV ddV dd − V T= RC ln 2 ≈ 0, 7RC (1.514)U ovom trenutku se menja samo stanje na izlazu kola a do kraja kvazistabilnogstanja T 1 se nastavlja punjenje konden<strong>za</strong>tora kada napon dostiže vrednostV E (T 1 ) = V dd [1 − e −T1/τ ] = V dd [1 − e −τ ln 3/τ ≈ 0, 95V dd (1.515)Na početku drugog kvazistabilnog stanja u kolu astabilnog multivibratora situacijaje sledeća:U B (T + 1 ) = V ddU C (T + 1 ) = 0V ⇒ U A(T + 1 ) = U C + U k = V T − V dd < 0V,(1.516)zbog čega se opet uključuje <strong>za</strong>štitna dioda na ulazu <strong>prvog</strong> invertora. Anali<strong>za</strong> kola jeslična kao i u prvom kvazistabilnom stanju a <strong>za</strong> trajanje drugog kvazistabilnog stanjase dobijaT 2 = τ ln 2V dd − V TV dd − V T= RC ln 3 ≈ 1, 1RC = T 1 (1.517)I izlazno kolo je simetrično, tako da u toku trajanja drugog kvazistabilnog stanja,pozitivan impuls na izlazu kola (tačka F ), trajanja T i , biva generisan pod uticajemizla<strong>za</strong> diferencijatora čiji je izlaz u tački D. Na osnovu ovoga vidimo da je periodaizlaznih impulsaT = T 1 = T 2 , (1.518)odnosno frekvencija iznosif = 1/T = 0, 9RC . (1.519)1.25 Za kolo sa slike 1.94a) odrediti napone V 1 , V 2 , polaritet ulaznog napona U ul i vrednost konden<strong>za</strong>toraC 2 tako da prvi deo kola bude monostabilni multivibrator sa trajanjem kvazistabilnogstanja T 1 = 5ms.b) Odrediti konden<strong>za</strong>tor C 3 tako da impuls u tački F kasni 2ms. Nacrtati signaleu svim tačkama kola u intervalu od 8ms od trenutka kada se na U ul dovede signal kojipobudi monostabilni multivibrator.V dd = V (1) = 15V , V (0) = 0V , V T = V dd /2, R 2 = 100K, R 3 = 1K, R 4 = 20K iR 5 = 200K.Rešenje:a) Da bi ulazno NI kolo moglo da reaguje na signal doveden na ulaz U ul potrebnoje da napon tačke C bude veći od napona praga NI kola tj.U C (0 − ) = V (1). (1.520)

LOGIČKA KOLA 81Slika 1.94:U stabilnom stanju kroz konden<strong>za</strong>tor C 2 ne teče struja tako da jeNeka jeU B (0 − ) = V 2 < V T . (1.521)V 2 = 0V ⇒ U k2 (0 − ) = 0V. (1.522)Da bi se stanje u kolu promenilo potreban je pozitivan skok napona u tački B a ondolazi kao posledica pada napona u tački A što znači da je u stabilnom stanju, tj. preokidanja kola napon tačke A veći od napona praga V T . Neka jeU A (0 − ) = V dd , (1.523)a kolo se dakle okida okidnim impulsom logičke nule tako da jeU ul (0 − ) = V ddU A (0 − ) = V 1 = V ddU B (0 − ) = V 2 = 0V.(1.524)Padom ulaznog naponamenja se stanje na izlazu diferencijatora,U ul (0 + ) = 0V (1.525)U A (0 + ) = U A (0 − ) + ∆U ul = 0V, (1.526)zbog čega napon na izlazu NI kola odlazi na nivo logičke jedinice. Sada jeU B (0 + ) = U NI−iz + U k2 = V dd ⇒ U C (0 + ) = V (0) = 0V (1.527)čime je krenulo generisanje impulsa u tački C. Diferencijator ima malu vremenskukonstantu,tako da se u tački A napon brzo vraća na vrednostτ d = R 1 C 1 → 0, (1.528)U A (t > 5τ d ) = V 1 = V dd . (1.529)Monostabilno kolo se vraća u stabilno stanje posle T 1 = 5ms, kada se u tački C ponovouspostavlja nivo logičke jedinice, zbog izjednačavanja napona tačke B sa naponompraga V T na osnovu čega se odred - uje vrednost konden<strong>za</strong>tora C 2

82 IMPULSNA ELEKTRONIKAT 1 = 5ms = C 2 R 2 ln U B(∞) − U B (0 + )U B (∞) − U B (T − 1 ) = C 2R 2 ln 0 − V dd0 − V T= C 2 R 2 ln 2⇒ C 2 = T 1R 2 ln 2 = 72nF. (1.530)Kada bi u stabilnom stanju napon tačke F iznosionapon tačke E bi imao vrednostU F (0 − ) = V (0) = 0V (1.531)R 5U E (0 − ) = U C (0 − )> V T (1.532)R 3 + R 4 + R 5jer kroz konden<strong>za</strong>tor C 3 u stabilnom stanju ne teče struja, na osnovu čega se <strong>za</strong>ključujeda u stabilnom stanju naponi imaju vrednostiU F = U E = U D = U C = V (1). (1.533)Kašnjenje impulsa u tački F , u odnosu na tačku C, unosi integrator R 3 C 3 čiji se izlazninapon iz tačke D vodi na ulaz naponskog komparatora sačinjenog od dva invertora(dvoulazna NI kola sa kratkospojenim ulaznim priključcima) i otpornika R 4 i R 5 .Promena stanja na izlazu komparatora nastaje kada napon tačke E dostiže vrednostnapona praga V T ,odakle se <strong>za</strong> pragove okidanja lakodobijaV ′ = V T + V T − U F (0)R 5R 4 = 8.25VV ′′ = V T + V T − U F (1)R 4 = 6, 75VR 5(1.534)Kada krene generisanje impulsalogičke nule u tački C,U C (0 + ) = V (0), (1.535)konden<strong>za</strong>tor C 3 sprečava nagle promenena izlazu kola tj.U D (0 + ) = U D (0 − ) = V dd= V E (0 + ) = V F (0 + ),(1.536)pa se ne menjaju ni naponi utačkama E i F . Vremenska konstantapunjenja konden<strong>za</strong>tora C 3 je Slika 1.95:

LOGIČKA KOLA 83τ 3 = C 3 [(R 4 + R 5 ) ‖ R 3 ] = 2, 49ms. (1.537)Punjenje se odvija ka asimptotskoj vrednostiU D (∞) =R 3R 3U F =V (1) = 0, 068V (1.538)R 3 + R 4 + R 5 R 3 + R 4 + R 5Iz izra<strong>za</strong> 1.530 vidimo da do promene u kolu dolazi kada jeodakle se dobijaU D = V ′′ = 6, 75V (1.539)odnosnoT 2 = 2ms = τ 3 ln U D(∞) − U D (0 + )U D (∞) − U D (T − 2 ) = τ 3 ln U D(∞) − V ddU D (∞) − V ′′ (1.540)S obzirom da jeC 3 =T 2[R 3 ‖ (R 4 + R 5 )] ln 0,068−150,068−6,75= 2, 5µF (1.541)<strong>za</strong> 0 < t < 2ms jeU E =U E =R 5R 4U D + U F (1.542)R 4 + R 5 R 4 + R 5R 5R 4U D + V dd (1.543)R 4 + R 5 R 4 + R 5a kako je napon tačke C na nivou logičke nule napon tačke E teži kajer je sadaU E (∞) 1 =R 3 + R 4R 3 + R 4 + R 5V (1) = 1, 425V (1.544)U F = V (1). (1.545)Za 2ms < t < 5ms nastavlja se pražnjenje konden<strong>za</strong>tora C 3 ali jeU F = V (0) = 0V. (1.546)Negativni skok iz tačke F , iz izra<strong>za</strong> 1.542 vidimo, i<strong>za</strong>ziva trenutni pad i u tački Ena vrednostU E (2ms + R 5) = V ′′ = 6, 136V. (1.547)R 4 + R 5Vremenska konstanta pražnjenja konden<strong>za</strong>tora C 3 je ostala ista a napon tačke Esada konvergira ka vrednostiU E (∞) 2 = U E (∞) 1 − (7, 5 − 6, 136) = 0, 062V, (1.548)odnosnoU D (∞) 1 = U E(∞)R 5[R 4 + R 5 ] = 0, 068V. (1.549)

84 IMPULSNA ELEKTRONIKANa osnovu ovoga se lako odred - uje dostignuti napon u tački D posle proteklih 5msU D (5ms) = U D (∞) 1 − [U D (∞) 1 − V dd ]e −5ms/τ 3= 2, 09V (1.550)a iz izra<strong>za</strong> 1.542 se dobijaZa t = 5ms + jeU E (5ms) = 1, 9V. (1.551)U C = V dd (1.552)a U F je još uvek na logičkoj nuli tako da napon tačke D počinje da raste ka vrednostiU D (∞) 2 =R 4 + R 5R 3 + R 4 + R 5U C = 14, 93V. (1.553)Posle vremena T 3 napon tačke D se izjednačava sa gornjim pragom komparatoratako da jeT 3 = τ 3 ln U D(∞) 2 − 2, 09= 1, 63ms (1.554)U D (∞) 2 − 8, 25Dakle napon u tački F se vraća na visok logički nivo posle 5ms + T 3 = 6, 63ms odpojave okidnog impulsa na ulazu kolaU F (6, 63ms + ) = V ddU E (6, 63ms − ) = V T = 7, 5V(1.555)tj. napon tačke E je dostigao napon praga logičkog kola. Sada skok napona u tačkiF i<strong>za</strong>ziva trenutnu promenu napona u tački E na novu vrednostU E (6, 63ms + ) = U E (6, 63ms − ) +posle čega ovaj napon raste do napona napajanja.R 4R 4 + R 5U F = 8, 86V, (1.556)1.26 Na ulaz CMOS invertora sa slike 1.96 se dovode pravougaoni impulsi frekvencijef = 4MHz amplitude 5V. Približno odrediti srednju snagu gubitaka u kolu ako jeV dd = 5V i C = 100pF a otpornost tranzistora u omskoj oblasti iznosi R o = 750Ω.Rešenje:S obzirom da tranzistori u kolu sa slike 1.96 vode istovremeno samo u prelaznomrežimu koji ćemo <strong>za</strong>nemarivati, kolo ima strukturu integratora čiji se konden<strong>za</strong>torpuni preko izlazne otpornosti tranzistora T 2 a prazni kroz tranzistor T 1 . Vremenskidijagram izlaznog napona u stacionarnom stanju prika<strong>za</strong>n je na slici 1.97. Kada je naulazu prisutan napon logičke jedinice U ul = 5V , vodi tranzistor T 2 , a konden<strong>za</strong>tor sepuni ka naponu napajanja V dd sa vremenskom konstantomAko promena na ulazu nastupa posle poluperiodeτ = CR o = 75ns. (1.557)

LOGIČKA KOLA 85T 1 = 12f= 125ns (1.558)na konden<strong>za</strong>toru je dostignut naponU iz = V dd − V 0 . (1.559)S obzirom na vezuV dd − V 0T 1 = τ lnV dd − (V dd − V 0 )= τ ln V (1.560)dd − V 0V 0<strong>za</strong> vrednost minimalnog napona nakonden<strong>za</strong>toru se dobija Slika 1.96:V ddV 0 =1 + e T 1/CR oV dd== 0, 79V1 + e 1/2fCR o(1.561)U toku jedne poluperiode promenaenergije na konden<strong>za</strong>toru iznosiSlika 1.97:[]∆E = 12C Vmax 2 − Vmin2 = 1 []2 C (V dd − V 0 ) 2 − V02pa se <strong>za</strong> srednju snagu gubitaka dobija(1.562)P = ∆ET 1= 2∆Es = fCV dd (V dd − 2V 0 ) = 6, 84mW (1.563)