Schaltnetze und Schaltwerke (update 9.1.03) - FZK

Schaltnetze und Schaltwerke (update 9.1.03) - FZK

Schaltnetze und Schaltwerke (update 9.1.03) - FZK

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

Hartmut Gemmeke<br />

Forschungszentrum Karlsruhe, IPE<br />

gemmeke@ipe.fzk.de<br />

Tel.: 07247-82-5635<br />

WS2002/2003<br />

Einführung in die Elektronik<br />

für Physiker<br />

<strong>Schaltnetze</strong> <strong>und</strong> <strong>Schaltwerke</strong><br />

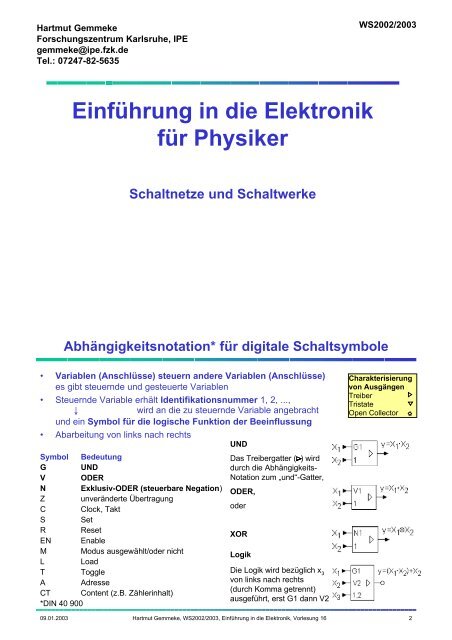

Abhängigkeitsnotation* für digitale Schaltsymbole<br />

• Variablen (Anschlüsse) steuern andere Variablen (Anschlüsse)<br />

es gibt steuernde <strong>und</strong> gesteuerte Variablen<br />

• Steuernde Variable erhält Identifikationsnummer 1, 2, ...,<br />

↓<br />

wird an die zu steuernde Variable angebracht<br />

<strong>und</strong> ein Symbol für die logische Funktion der Beeinflussung<br />

• Abarbeitung von links nach rechts<br />

UND<br />

Symbol Bedeutung<br />

G UND<br />

V ODER<br />

N Exklusiv-ODER (steuerbare Negation)<br />

Z unveränderte Übertragung<br />

C Clock, Takt<br />

S Set<br />

R Reset<br />

EN Enable<br />

M Modus ausgewählt/oder nicht<br />

L Load<br />

T Toggle<br />

A Adresse<br />

CT Content (z.B. Zählerinhalt)<br />

*DIN 40 900<br />

Das Treibergatter ( ) wird<br />

durch die Abhängigkeits-<br />

Notation zum „<strong>und</strong>“-Gatter,<br />

ODER,<br />

oder<br />

XOR<br />

Logik<br />

∆<br />

Die Logik wird bezüglich x 3<br />

von links nach rechts<br />

(durch Komma getrennt)<br />

ausgeführt, erst G1 dann V2<br />

Charakterisierung<br />

von Ausgängen<br />

Treiber<br />

Tristate<br />

Open Collector<br />

09.01.2003 Hartmut Gemmeke, WS2002/2003, Einführung in die Elektronik, Vorlesung 16 2

Beispiele zur Abhängigkeitsnotation I<br />

• Zwei 2:1 Multiplexer<br />

ein Steuereingang beeinflusst mehrere Eingänge,<br />

der Negationsstrich über der Nummer der<br />

Steuervariablen zeigt an , dass die negierte<br />

Steuervariable in der Verknüpfung zu benutzen ist. Das<br />

≥1 Zeichen bezeichnet das „oder“ für den Ausgang. Die<br />

horizontalen Trennstriche teilen die einzelnen<br />

Logikbereiche für den Ausgang ab.<br />

a<br />

G1<br />

d 0 1<br />

d 1 1<br />

d 2 1<br />

d 3 1<br />

≥1 y 0=a . d 0 +a . d 1<br />

≥1 y 1=a . d 2 +a . d 3<br />

• 4:1 Multiplexer<br />

hier sind zwei Steueranschlüsse a 0 <strong>und</strong> a 1 durch die<br />

geschweifte Klammer zu einer Steuervariablen mit dem<br />

0<br />

Wertebereich 0bis 3=<br />

zusammengefasst, d.h. d 0 wird<br />

3<br />

nur erfasst, wenn a 0 <strong>und</strong> a 1 = 0 sind, oder d 3 , wenn a 0<br />

<strong>und</strong> a 1 = 1 sind.<br />

a 0 0<br />

a 1 1<br />

d 0 0<br />

d 1 1<br />

d 2 2<br />

d 3 3<br />

G 0 3<br />

≥1 y=a 0 . a 1<br />

. d0 +...<br />

09.01.2003 Hartmut Gemmeke, WS2002/2003, Einführung in die Elektronik, Vorlesung 16 3<br />

Beispiele zur Abhängigkeitsnotation II<br />

Vorwärts-/Rückwärtszähler mit synchronen<br />

Ladeeingängen <strong>und</strong> steuernder Wirkung<br />

eines Inhaltes (Content CT)<br />

• 3 Betriebsarten (0 - 2) Modus M:<br />

0 (Load=0 & Up=0): abwärts zählen (-), wenn<br />

Enable(4) = 1<br />

1 synchron mit dem Takt (C) Daten D laden<br />

1, 5 D (D für Daten zusätzlich eingeführte<br />

Identifikation für die Eingänge d 0 - d 3 )<br />

2 Notation 2,4+ bedeutet Zählerstand<br />

inkrementieren, wenn Enable(4) = 1<br />

• Übertragsausgang* CO wird vom<br />

Zählerinhalt CT gesteuert, d.h. = 1 wenn:<br />

– Wenn beim Vorwärtszählen (Modus 2) der<br />

Zählerinhalt 15 beträgt (2,4 CT=15) bzw.<br />

– Wenn beim Abwärtszählen (Modus 0) der<br />

Inhalt des Zählers 0 ist (0,4 CT=0)<br />

– In beiden Fällen muss Enable(4) = 1 sein<br />

*counter overrange<br />

Load<br />

Up/Down<br />

Enable<br />

Clk<br />

d<br />

d<br />

d<br />

d<br />

0<br />

1<br />

2<br />

3<br />

0⎫<br />

0<br />

⎬M<br />

1⎭<br />

2<br />

04 , CT = 0/ 24 , CT = 15 CO<br />

EN4<br />

04 , − / 1, C5/ 24 , +<br />

15 , D<br />

15 , D<br />

15 , D<br />

15 , D<br />

09.01.2003 Hartmut Gemmeke, WS2002/2003, Einführung in die Elektronik, Vorlesung 16 4

Systematik digitaler Schaltungen<br />

1. <strong>Schaltnetze</strong><br />

x 1<br />

= digitale Schaltungen ohne Speicher<br />

x 2<br />

.<br />

= kombinatorische Logik<br />

.<br />

.<br />

.<br />

= Vektoren boolescher Funktionen<br />

.<br />

.<br />

.<br />

.<br />

.<br />

.<br />

2. <strong>Schaltwerke</strong> (finit state machine, FSM)<br />

.<br />

= <strong>Schaltnetze</strong> für m Eingangsvariable,<br />

n Zustands- <strong>und</strong> o Ausgangs-Variable<br />

+ Speicher für Zustandsvariablen Z<br />

+ Rückführung der Zustandsvariablen m<br />

auf den Eingang<br />

Schaltnetz<br />

X<br />

+ Taktgeber<br />

→ Y = f(X,Z)<br />

= Ausgangsvektor<br />

→ X = Eingangsvektor<br />

→ Z(t k ) = letzter Zustandsvektor<br />

zur Zeit t k<br />

Schaltnetz<br />

y 1<br />

y 2<br />

.<br />

.<br />

Ausgangsvektor<br />

.<br />

.<br />

.<br />

y = f(x 1 ,...x n<br />

.<br />

)<br />

.<br />

y m<br />

x n<br />

Z(t k +1)<br />

n<br />

Z(t k )<br />

o<br />

Y(X,Z)<br />

Zustandsvariablen<br />

Speicher<br />

φ Takt<br />

09.01.2003 Hartmut Gemmeke, WS2002/2003, Einführung in die Elektronik, Vorlesung 16 5<br />

Beispiele für <strong>Schaltnetze</strong> I<br />

• Dekoder 1 aus 4<br />

• Anwendung: aus binärer Adresse ein Gatter oder Chip selektieren:<br />

n<br />

a 1<br />

a 0<br />

y 3<br />

y 2<br />

y 1<br />

y 0<br />

Negation<br />

0<br />

1<br />

2<br />

3<br />

0 0<br />

0 1<br />

1 0<br />

1 1<br />

a0⋅a1 a0 ⋅a1 a0⋅a1 a0⋅a1<br />

0 0 0 1<br />

0 0 1 0<br />

0 1 0 0<br />

1 0 0 0<br />

einlagiges<br />

Netz<br />

09.01.2003 Hartmut Gemmeke, WS2002/2003, Einführung in die Elektronik, Vorlesung 16 6

Beispiele für <strong>Schaltnetze</strong> II<br />

• Multiplexer 4:1<br />

– Es gibt verschiedene Eingangsinformationen d 0 – d 3 .<br />

Eine Datenleitung d i soll mit den binären Selektoren<br />

a 0 , a 1 , d.h. einem Dekoder, ausgewählt <strong>und</strong> auf eine<br />

Ausgangsleitung y geschaltet werden<br />

a 0 0<br />

a 1 1<br />

d 0 0<br />

d 1 1<br />

d 2 2<br />

d 3 3<br />

G 0 3<br />

≥1 y=a 0 . a 1<br />

. d0 +...<br />

09.01.2003 Hartmut Gemmeke, WS2002/2003, Einführung in die Elektronik, Vorlesung 16 7<br />

Rechenwerk als Beispiel für <strong>Schaltnetze</strong> I<br />

• Halbaddierer (ohne Übertrag einer Vorstufe):<br />

– 0 + 0 = 0, Summe Σ =0<br />

– 1 + 0 = 0 + 1 = 1, Summe Σ =1<br />

– 1 + 1 = 10, d.h. Summe Σ =0 <strong>und</strong> Carry (Übertrag) C = 1<br />

a b<br />

0 0<br />

0 1<br />

1 0<br />

1 1<br />

Σ C<br />

0 0<br />

1 0<br />

1 0<br />

0 1<br />

Σ = a ⊕ b<br />

C = a ⋅ b<br />

09.01.2003 Hartmut Gemmeke, WS2002/2003, Einführung in die Elektronik, Vorlesung 16 8

Rechenwerk als Beispiel für <strong>Schaltnetze</strong> II<br />

• Volladdierer ⇔ Carry der Vorstufe berücksichtigt<br />

0 0 0<br />

0 0 1<br />

0 1 0<br />

0 1 1<br />

1 0 0<br />

1 0 1<br />

1 1 0<br />

1 1 1<br />

Σ i<br />

C i<br />

C i -1 a i b i<br />

Symbol für Volladdierer<br />

0 0<br />

1 0<br />

1 0<br />

0 1<br />

1 0<br />

0 1<br />

0 1<br />

1 1<br />

C<br />

Σ<br />

1<br />

2<br />

Σ i<br />

= (a i<br />

⊕ b i<br />

) ⊕ C i-1<br />

C i<br />

= a i<br />

⋅ b i<br />

+ C i-1<br />

⋅ (a i<br />

⊕ b i<br />

)<br />

09.01.2003 Hartmut Gemmeke, WS2002/2003, Einführung in die Elektronik, Vorlesung 16 9<br />

Rechenwerke III<br />

• Beispiel: duale Addition von A = 13 <strong>und</strong> B = 9 mit einem 4-Bit Addierer<br />

• A = 13 1 1 0 1<br />

• B = 9 1 0 0 1<br />

--------------------------------<br />

• 1 0 1 1 0 = Σ<br />

C 4 = Übertrag für den nächsten Addierer<br />

• Binäre Zahlendarstellung mit beliebigen Vorzeichen<br />

– „führendes“ Bit = Vorzeichen: 0 = + , 1 = −<br />

– Standard-Darstellung: a = ( sign(a), ⎜a⎟ ) (Problem, 0 kommt 2-mal vor, Rechenwerk muss für<br />

Subtraktion umgestellt werden)<br />

• Subtraktion = Addition einer negativen Zahl<br />

⇒ Zweier-Komplement = Einer-Komplement +1<br />

• z.B. Darstellung von -1 oder eine Subtraktion 13 - 1 =12<br />

sign sign<br />

• 1 0 0 0 0 1 13 0 1 1 0 1<br />

• 1-Komplement 1 1 1 1 0 -1 1 1 1 1 1<br />

• +1 0 0 0 0 1<br />

---------------------------------------------------------------------------------------------------------<br />

• -1 = 1 1 1 1 1 Σ = 12 (1) 0 1 1 0 0<br />

09.01.2003 Hartmut Gemmeke, WS2002/2003, Einführung in die Elektronik, Vorlesung 16 10

Rechenwerke IV<br />

• Zahlendarstellung für n = 4 im 2er-Komplement<br />

– positive Zahlen bis 2 n –1 negative Zahlen bis 2 n<br />

0 0 0 0 0 0 0 0 0 0 0 0<br />

1 0 0 0 0 1 -1 1 1 1 1 1<br />

2 0 0 0 1 0 -2 1 1 1 1 0<br />

3 0 0 0 1 1 -3 1 1 1 0 1<br />

: :<br />

15 0 1 1 1 1 -15 1 0 0 0 1<br />

-16 1 0 0 0 0<br />

• 4-Bit Volladdierer in Hardware<br />

Summe<br />

0<br />

• Summe A+B für C 0<br />

= 0<br />

• Differenz (A-B) = A + B + 1<br />

mit C 0<br />

= 1 !!<br />

Differenz<br />

1<br />

09.01.2003 Hartmut Gemmeke, WS2002/2003, Einführung in die Elektronik, Vorlesung 16 11<br />

Schaltwerk = sequentielle Logik<br />

• Beschreibung:<br />

– Schaltung<br />

– Zustandsfolge-Tabelle, -Funktion<br />

– Flussdiagramm<br />

– Zustandsdiagramm, -graph<br />

• Zustandsdiagramm besteht aus<br />

Power-on<br />

Zustandsdiagramm<br />

S 0 S 1<br />

x 0<br />

S 2<br />

– Knoten, die den Zustand S k<br />

beschreiben, <strong>und</strong><br />

– Kanten, die die Übergangsbedingungen<br />

x i zwischen den<br />

Zuständen definieren.<br />

• Beispiel: für ein Zustandsdiagramm<br />

– S0: Anfangszustand nach Power-on<br />

– S1: Übergangszustand<br />

– S2: Verzweigungszustand<br />

– S3: Wartezustand<br />

x 3<br />

x 3<br />

x 2<br />

x 1<br />

x 2<br />

S 3<br />

09.01.2003 Hartmut Gemmeke, WS2002/2003, Einführung in die Elektronik, Vorlesung 16 12

Beispiele <strong>Schaltwerke</strong> I<br />

Asynchrones RS-Flip-Flop mit NOR-Gattern (ungetaktet)<br />

Schaltung Wahrheitstafel Impulsdiagramm Flussdiagramm<br />

R<br />

S<br />

≥1<br />

≥1<br />

q<br />

q<br />

S<br />

R<br />

0 0<br />

0 1<br />

1 0<br />

1 1<br />

Q<br />

Q -1<br />

0<br />

1<br />

(0)<br />

S=R=1 nicht definiert,<br />

schaltungsabhängig<br />

[s,r]=[0,x],([1,1])<br />

q=0<br />

s<br />

r<br />

q<br />

t<br />

t<br />

t<br />

n<br />

y<br />

s = 0<br />

n<br />

q = 0<br />

s = 0<br />

n<br />

r = 0<br />

y<br />

y<br />

n<br />

[s,r] = [0,1]<br />

q=1<br />

[s,r]=[x,0]<br />

[s,r] = [1,0]<br />

für<br />

beliebigen<br />

Zustand x<br />

Zustandsdiagramm<br />

q<br />

S<br />

R<br />

q<br />

Schaltungssymbol<br />

r = 0<br />

y<br />

q = 1<br />

09.01.2003 Hartmut Gemmeke, WS2002/2003, Einführung in die Elektronik, Vorlesung 16 13<br />

Beispiele <strong>Schaltwerke</strong> II<br />

• Beispiel: RS-Flipflop mit NAND-Gattern<br />

• Anwendung:<br />

Entprellung einer mechanischen Taste<br />

(Tastatur schwingt nach) <strong>und</strong> hat eine<br />

mechanische Umschaltzeit t u<br />

• Wegen der Beschaltung tritt der Zustand<br />

S=R=0 nicht ein<br />

S<br />

R<br />

0 0<br />

0 1<br />

1 0<br />

1 1<br />

Q<br />

(1)<br />

0<br />

1<br />

Q -1<br />

09.01.2003 Hartmut Gemmeke, WS2002/2003, Einführung in die Elektronik, Vorlesung 16 14

<strong>Schaltwerke</strong>: Elementare Kippschaltungen<br />

• Definition: Kippschaltung = digitale Schaltung mit sprunghaftem<br />

Übertragungsverhalten<br />

– Schwellwertschalter (Schmitt-Trigger, haben durch Mitkopplung Hysterese)<br />

– stabile Kippschaltung (durch Rückkopplung selbsthaltend)<br />

– monostabile Kippschaltung (fällt nach bestimmter Haltezeit wieder in den stabilen<br />

Gr<strong>und</strong>zustand zurück)<br />

– bistabile Kippschaltung (Flipflop)<br />

– astabile Kippschaltung (Multivibrator)<br />

• Bedeutsam für die<br />

Schaltungstechnik<br />

sind insbesondere<br />

die bistabilen<br />

Kippschaltungen<br />

ungetaktet<br />

z.B.: NOR-Basis-FF<br />

zustandsgesteuert<br />

z.B.:synchrone RS-FF<br />

Bistabile Kippglieder<br />

(Flipflop)<br />

taktgesteuert<br />

flankengesteuert<br />

(dynamisch)<br />

einflankengesteuert<br />

z.B.: D-FF<br />

zweiflankengesteuert<br />

z.B.: JK-MS-FF<br />

09.01.2003 Hartmut Gemmeke, WS2002/2003, Einführung in die Elektronik, Vorlesung 16 15<br />

Synchrone (getaktete) Flipflops<br />

1. Über C Taktzustandsgesteuerte Flipflops<br />

(transparente synchrone FF)<br />

– RS-Flipflop<br />

• C = 0 entspricht R=S=1 <strong>und</strong> damit<br />

Q = Q(t-1)<br />

• C = 1 entspricht asynchronem<br />

RS-Flipflop<br />

• Schaltsymbol in Abhängigkeitsnotation:<br />

– D-Flipflop oder D-Latch (Halteschaltung)<br />

• C = 1 Q = D, Q = D, für C = 1 wirkt<br />

Rückkopplung für D = 0 als invertiertes<br />

Signal als „Reset“ auf R´ des RS-Flipflops<br />

• C = 0 Q = D(t-1) Q = D(t-1)<br />

• Schaltsymbol in Abhängigkeitsnotation:<br />

09.01.2003 Hartmut Gemmeke, WS2002/2003, Einführung in die Elektronik, Vorlesung 16 16

Taktflankengesteuerte Flipflops<br />

• digitale Differenziation einer Flanke<br />

mit 3 Ingredienzien:<br />

1. Ungerade Zahl von Invertern, um<br />

verzögertes (um T‘-T) <strong>und</strong> invertiertes<br />

Signal zu erzeugen<br />

2. „UND“-Gatter, um Vorderflanke heraus<br />

zu differenzieren<br />

3. „NOR“-Gatter für die Rückflanke<br />

• Anwendung:<br />

– flankengetriggertes RS- oder D-<br />

Flipflop entspricht Zustandsflipflop mit<br />

T = Clock <strong>und</strong><br />

– Clock´ = A 1 Übernahme von R, S oder<br />

D mit steigender Flanke L → H oder<br />

– Clock´ = A 2 (verzögerte) Übernahme<br />

mit fallender Flanke H → L<br />

• Problem<br />

– Verzögerung ist abhängig von<br />

verwendeter Technologie<br />

T<br />

T<br />

T'<br />

A 1<br />

A 2<br />

1 1 1<br />

T'-T<br />

=> Master-Slave Flip-Flops<br />

T'<br />

&<br />

≥1<br />

A 1<br />

A 2<br />

t<br />

t<br />

t<br />

t<br />

09.01.2003 Hartmut Gemmeke, WS2002/2003, Einführung in die Elektronik, Vorlesung 16 17<br />

Flipflops mit Zwischenspeicherung<br />

a) Zwischenspeicherung des Eingangszustandes<br />

b) Eingang verriegeln<br />

c) Zwischenspeicher ausgeben<br />

⇒ Optimale Zeitauflösung für Definition der Flanke<br />

⇒ 2 Flipflops: Master- <strong>und</strong> Slave-Flipflop<br />

beim Übergang von C H⇒ L wird der Masterzustand eingefroren<br />

<strong>und</strong> der Slave (sowie Ausgang) folgt dem Master, RS-MS-FF:<br />

• Anwendung: Register oder D-Flipflop<br />

09.01.2003 Hartmut Gemmeke, WS2002/2003, Einführung in die Elektronik, Vorlesung 16 18

• JK-Flipflop = flankengesteuertes RS-Flipflop + Rückkopplung<br />

⇒ J=K=1 Toggle = automatischer Wechsel des Ausgangszustands mit jedem Takt<br />

C<br />

L/H<br />

J<br />

K<br />

0 0<br />

0 1<br />

1 0<br />

1 1<br />

0 0<br />

Q n 0<br />

0 Q n<br />

Q n Q n<br />

Q n+1<br />

Q n<br />

0<br />

1<br />

Q n<br />

• JK-Master-Slave Flipflops<br />

R<br />

– Entkopplung von Ein- <strong>und</strong> Ausgang<br />

– Zusätzlich:<br />

• Preset <strong>und</strong> Clear<br />

S<br />

JK-Flipflop<br />

bei positiver Taktflanke<br />

übernimmt der Master<br />

den Eingang<br />

bei negativer Taktflanke<br />

übernimmt der Slave<br />

den Master<br />

Anwendung: Zähler, Schieberegister („Toggle“-Funktion wird benötigt)<br />

09.01.2003 Hartmut Gemmeke, WS2002/2003, Einführung in die Elektronik, Vorlesung 16 19<br />

Allgemeine Multifunktionsflipflops<br />

Beispiel für Abhängigkeitsnotation<br />

• Flipflop mit folgenden Funktionen:<br />

– Halte altes Q<br />

– T = Toggle<br />

– L = Lade D<br />

D = Data<br />

C = Clock<br />

L<br />

0<br />

0<br />

1<br />

1<br />

T<br />

0<br />

1<br />

0<br />

1<br />

Q n+1<br />

Q n<br />

Q n<br />

D<br />

D<br />

• Bezeichnungen an Schaltsymbolen:<br />

– Dynamischer Eingang, reagiert auf 0 ⇒ 1<br />

– Dynamischer Eingang mit Negation, reagiert auf 1 ⇒ 0<br />

– Verzögerter Ausgang (solange wie Eingang auf 1 steht)<br />

09.01.2003 Hartmut Gemmeke, WS2002/2003, Einführung in die Elektronik, Vorlesung 16 20

Die wesentlichen Flipflop-Typen<br />

Übernimmt Information<br />

beim Taktübergang L/H.<br />

Gekennzeichnet durch ( )<br />

j=k=1 ⇒ toggle<br />

Ausgang mit 2 ter<br />

Flanke ( )<br />

09.01.2003 Hartmut Gemmeke, WS2002/2003, Einführung in die Elektronik, Vorlesung 16 21<br />

Komplexe Digitalschaltungen: asynchrone Dualzähler<br />

Kombination von kombinatorischen (Boolesche Logik) <strong>und</strong><br />

sequentiellen Schaltungskomponenten<br />

1. Zähler (gezählt werden die Pulse N)<br />

– Gr<strong>und</strong>element eines Zählers ist z.B. ein JK-Master-Slave Flipflop<br />

oder ein einflankengetriggertes D-Flipflop (Master-Slave)<br />

– Notwendig ist die Toggle Funktion J = K = 1 bzw. D-Flipflop mit D Q<br />

asynchrone Dualzähler:<br />

Vorwärtszähler:<br />

Slave ändert seinen<br />

Zustand bei<br />

negativer Flanke<br />

von N<br />

Rückwärtszähler:<br />

Slave ändert seinen<br />

Zustand bei<br />

positiver Flanke<br />

von N<br />

09.01.2003 Hartmut Gemmeke, WS2002/2003, Einführung in die Elektronik, Vorlesung 16 22

Synchrone Binärzähler<br />

1. Zählimpulse werden gleichzeitig auf alle Takteingänge der Zählerstufen<br />

gegeben ⇒ synchrones Umschalten der Kippstufen<br />

2. Kippstufe darf erst umschalten, wenn alle vorhergehenden Stufen auf „1“<br />

sind entspricht J = K = 1, sonst J = K = 0 entspricht keine Änderung<br />

Übertrag für die<br />

nächste Zählstufe<br />

– keine Verzögerung zwischen Takt <strong>und</strong> Zählresultat<br />

– Untersetzer = Frequenzteiler<br />

– 4-Bit-Zähler = 1:16 Umsetzer<br />

– Beliebiger Untersetzungsfaktor durch „UND-Gatter“<br />

der Q i verknüpft für ein CLR-Signal, z.B.: 1:10<br />

– Abhängig von der Stufe (Eingang oder Ausgang), auf<br />

die das Clear wirkt, ist CLR= Q 1 . Q 3 oder Q 0 . Q 3<br />

09.01.2003 Hartmut Gemmeke, WS2002/2003, Einführung in die Elektronik, Vorlesung 16 23<br />

Schieberegister (FIFO=first in first out)<br />

Bei jedem Taktimpuls wird die Information um eine Stelle weitergeschoben<br />

Parallele Auslese über Q A<br />

... Q D<br />

.<br />

JK-MS-Flipflop<br />

J = K entspricht Verhalten von<br />

einem D-Flipflop Q(t+1) = J<br />

(j,k)=(0,1) & Takt ↓ => Q=0<br />

(j,k)=(1,0) & Takt ↓ => Q=1<br />

• Seriell ⇒ Parallel-Wandlung<br />

– Schieberegister mit Parallel-Ausgang<br />

– Entspricht Ring Buffer<br />

• Parallel ⇒ Seriell-Wandlung<br />

– Schieberegister mit Parallel-Eingang<br />

09.01.2003 Hartmut Gemmeke, WS2002/2003, Einführung in die Elektronik, Vorlesung 16 24