Einführung in die Elektronik für Physiker

Einführung in die Elektronik für Physiker

Einführung in die Elektronik für Physiker

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

Hartmut Gemmeke<br />

Forschungszentrum Karlsruhe, IPE<br />

hartmut.gemmeke@kit.de<br />

Tel.: 07247-82-5635<br />

<strong>E<strong>in</strong>führung</strong> <strong>in</strong> <strong>die</strong> <strong>Elektronik</strong> <strong>für</strong><br />

<strong>Physiker</strong><br />

JFET - MOSFET<br />

11. Feldeffekt-Transistoren<br />

Ausgangskennl<strong>in</strong>ie und typische Kenndaten<br />

Vergleich der verschiedenen FETs und mit Bipolartransistor<br />

Grundschaltungen des FETs: Source-, stromgegengekopplelte Source-<br />

Schaltung, Source-Folger (Dra<strong>in</strong>schaltung)<br />

Anwendungen des JFETs als steuerbarer Widerstand, Konstantstromquelle<br />

Zerstörung des FETs durch elektrostatische Entladung<br />

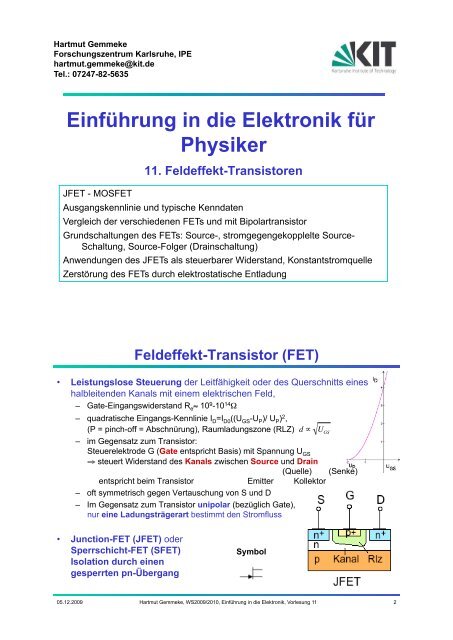

Feldeffekt-Transistor (FET)<br />

• Leistungslose Steuerung der Leitfähigkeit oder des Querschnitts e<strong>in</strong>es<br />

halbleitenden Kanals mit e<strong>in</strong>em elektrischen Feld,<br />

– Gate-E<strong>in</strong>gangswiderstand R e ! 10 9 -10 14 "<br />

– quadratische E<strong>in</strong>gangs-Kennl<strong>in</strong>ie I D =I D0 ((U GS -U P )/ U P ) 2 ,<br />

(P = p<strong>in</strong>ch-off = Abschnürung), Raumladungszone (RLZ)<br />

d " U GS<br />

– im Gegensatz zum Transistor:<br />

Steuerelektrode G (Gate entspricht Basis) mit Spannung UGS # steuert Widerstand des Kanals zwischen Source<br />

!<br />

und Dra<strong>in</strong><br />

(Quelle) (Senke)<br />

entspricht beim Transistor Emitter Kollektor<br />

– oft symmetrisch gegen Vertauschung von S und D<br />

– Im Gegensatz zum Transistor unipolar (bezüglich Gate),<br />

nur e<strong>in</strong>e Ladungsträgerart bestimmt den Stromfluss<br />

• Junction-FET (JFET) oder<br />

Sperrschicht-FET (SFET)<br />

Isolation durch e<strong>in</strong>en<br />

gesperrten pn-Übergang<br />

Symbol<br />

05.12.2009 Hartmut Gemmeke, WS2009/2010, <strong>E<strong>in</strong>führung</strong> <strong>in</strong> <strong>die</strong> <strong>Elektronik</strong>, Vorlesung 11 2

MOSFET (Metal-Oxide-Semiconductor)<br />

• auch IGFET (<strong>in</strong>sulated Gate FET) genannt<br />

• Eigenschaften und Kennl<strong>in</strong>ien ähnlich dem<br />

Sperrschicht-FET<br />

• Gate ist durch Metalloxid vom Substrat<br />

getrennt, <strong>die</strong>lektrische Isolation<br />

# R e ! 10 12 -10 15 "<br />

# Cave: Reibungs-Elektrizität! Kle<strong>in</strong>ste<br />

Ströme, bzw. Ladungen an C gate zerstören FET<br />

• MOS und JFET´s haben große Exemplar-<br />

streuung <strong>in</strong>sbesondere von U P<br />

Unterschiede zwischen MOS und JFET:<br />

• E<strong>in</strong>gangswiderstand Re – JFET Re > 109 "<br />

– MOSFET Re > 1012 •<br />

"<br />

Rauschen:<br />

– JFET hat e<strong>in</strong> sehr ger<strong>in</strong>ges Rauschen<br />

• Die Temperaturabhängigkeit<br />

ist ger<strong>in</strong>ger als beim<br />

Bipolartransistor:<br />

=> Anwendung <strong>in</strong> Vorverstärkern<br />

– MOSFET: 1/f-Rauschen groß bei $ 100kHz<br />

dUP /dT = -1 mV/K<br />

– Transistoren 1/f-Rauschen groß bei $ 1kHz, siehe Kap.15<br />

05.12.2009 Hartmut Gemmeke, WS2009/2010, <strong>E<strong>in</strong>führung</strong> <strong>in</strong> <strong>die</strong> <strong>Elektronik</strong>, Vorlesung 11 3<br />

05.12.2009 Hartmut Gemmeke, WS2009/2010, <strong>E<strong>in</strong>führung</strong> <strong>in</strong> <strong>die</strong> <strong>Elektronik</strong>, Vorlesung 11 4<br />

bulk<br />

MOSFET-Anreicherungstyp<br />

• n-Kanal-Anreicherungs-Typ (nur <strong>für</strong> MOSFET und nicht <strong>für</strong> JFET<br />

möglich):<br />

– positive Gate-Spannung<br />

=> negative M<strong>in</strong>oritäts-Ladungsträger werden zur isolierten Gate-Elektrode gezogen<br />

=> n-Kanal zwischen den beiden n-Inseln Source und Dra<strong>in</strong>.<br />

– spannungsloser Zustand oder<br />

angelegte negative Gate-Spannung<br />

=> zwei gegene<strong>in</strong>ander geschaltete Dioden ! selbstsperrend<br />

=> stromlos<br />

Symbol<br />

bulk

MOSFET-Verarmungstyp<br />

bzw. selbstleitender Depletion MOSFET<br />

• Auch bei U GS = 0 Strom (wie JFET)<br />

%U GS > 0 vergrößert den Strom und<br />

%U GS < 0 verr<strong>in</strong>gert den Strom.<br />

Der Querschnitt und <strong>die</strong> Leitfähigkeit<br />

des Kanals wird verändert<br />

• Ger<strong>in</strong>ge Gate-Dra<strong>in</strong> Kapazität<br />

# HF-Anwendungen<br />

Symbol<br />

05.12.2009 Hartmut Gemmeke, WS2009/2010, <strong>E<strong>in</strong>führung</strong> <strong>in</strong> <strong>die</strong> <strong>Elektronik</strong>, Vorlesung 11 5<br />

Wie funktioniert <strong>die</strong> Grenzschicht zum Kanal?<br />

E<strong>in</strong>gesperrte Ladungen im SiO 2 können Elektronen im Bereich der<br />

Grenzschicht zum Si b<strong>in</strong>den und so e<strong>in</strong>en Kanal ausbilden. In jedem Falle<br />

bestimmen sie <strong>die</strong> p<strong>in</strong>ch-off (Abschnür-) Spannung.<br />

E<strong>in</strong>gesperrte Ladungen bestimmen<br />

Rauschen<br />

05.12.2009 Hartmut Gemmeke, WS2009/2010, <strong>E<strong>in</strong>führung</strong> <strong>in</strong> <strong>die</strong> <strong>Elektronik</strong>, Vorlesung 11 6<br />

bulk<br />

Perspektivische Darstellung e<strong>in</strong>es<br />

MOS-FETs

Ausgangskennl<strong>in</strong>ie<br />

• Selbstleitender FET, U k = Kniespannung<br />

Anlaufbereich Abschnürbereich<br />

05.12.2009 Hartmut Gemmeke, WS2009/2010, <strong>E<strong>in</strong>führung</strong> <strong>in</strong> <strong>die</strong> <strong>Elektronik</strong>, Vorlesung 11 7<br />

Zur Illustration das<br />

weite Spektrum der<br />

FET-Daten:<br />

Typische Kenndaten von FETs<br />

Typ BF245B IRF530<br />

Technologie n-Kanal Sperrschicht-FET,<br />

selbstleitend<br />

MOS-FET,<br />

selbstsperrend<br />

Grenzdaten:<br />

Dra<strong>in</strong>strom I Dmax 25 mA 10 A<br />

Gate-Source-Spg. U GSmax -30 V ± 20 V<br />

Verlustleistung P max 300 mW 75 W<br />

Kenndaten:<br />

Schwellenspannung U p -1,5 … -4,5 V 1,5 … 3,5 V<br />

Dra<strong>in</strong>strom I DS 6 … 15 mA 5 A<br />

Maximale Steilheit S S 5 mA/V 5 A/V<br />

M<strong>in</strong>imaler Widerstand R DSon 200 ! 0,14 !<br />

Max. Gatesperrstrom I Gmax 5 nA 0,5 mA<br />

Max. Dra<strong>in</strong>sperrstrom I Dmax 10 nA 1 mA<br />

E<strong>in</strong>gangskapazität C eS 4 pF 750 pF<br />

Ausgangskapazität C aS 1,6 pF 300 pF<br />

Rückwirkungskapazität C rS 1,1 pF 50 pF<br />

Rauschen F 1,5 dB<br />

Steilheitsgrenzfrequenz f S 700 MHz<br />

E<strong>in</strong>schaltverzögerung t on 30 ns<br />

05.12.2009 Hartmut Gemmeke, WS2009/2010, <strong>E<strong>in</strong>führung</strong> <strong>in</strong> <strong>die</strong> <strong>Elektronik</strong>, Vorlesung 11 8

Überblick über <strong>die</strong> verschiedenen FET-Typen<br />

Selbstleitende FET´s <strong>für</strong> U GS = 0 Symbol mit && selbstsperrende FET´s mit - - -!<br />

Beim<br />

Mosfet s<strong>in</strong>d<br />

Source und<br />

Bulk<br />

zumeist<br />

verbunden:<br />

Bulk-Kanal-<br />

Diode ist<br />

gesperrt!!!<br />

05.12.2009 Hartmut Gemmeke, WS2009/2010, <strong>E<strong>in</strong>führung</strong> <strong>in</strong> <strong>die</strong> <strong>Elektronik</strong>, Vorlesung 11 9<br />

Vergleich: Bipolartransistor - JFET<br />

Pr<strong>in</strong>zipschaltung<br />

ohne Gegenkopplung<br />

Exemplarstreuung<br />

der<br />

E<strong>in</strong>gangsspannung<br />

Exemplarstreuung<br />

der Verstärkung<br />

Emitterschaltung Sourceschaltung<br />

U BE = 0,6V ±50mV<br />

!U BE = kle<strong>in</strong><br />

$ max<br />

= 2bis<br />

4<br />

$ m<strong>in</strong><br />

05.12.2009 Hartmut Gemmeke, WS2009/2010, <strong>E<strong>in</strong>führung</strong> <strong>in</strong> <strong>die</strong> <strong>Elektronik</strong>, Vorlesung 11 10<br />

"<br />

#U P = 2bis6V<br />

!U P =gro$<br />

Smax<br />

= 2bis<br />

4<br />

Sm<strong>in</strong><br />

Fertigungstoleranzen <strong>für</strong> FETs s<strong>in</strong>d größer als <strong>für</strong> Bipolartransistoren !

!<br />

!<br />

Transistor # FET<br />

I C " I D<br />

I E "I S<br />

Source-Schaltung<br />

S = #I C<br />

#U BE<br />

I B "I G $0 r B "r G $%<br />

U CE "U DS<br />

U BE " U GS<br />

V u = dU a<br />

dU e<br />

" S = #I D<br />

#U GS<br />

Sr = #IB "S<br />

#U r =<br />

CE<br />

#IG $0<br />

#UDS rC "rD & " S ' r $ %<br />

GS<br />

= ( dID' RD r ( DS)<br />

= (S ' ( R<br />

dU D rDS) GS<br />

Z $ R r<br />

a D DS<br />

ID =<br />

ID0 UP (U ) , 2<br />

+ GS<br />

+ .<br />

* U<br />

. " U = U ' 1(<br />

P -<br />

GS P I ) ,<br />

+ D .<br />

+ I .<br />

* D0 -<br />

S = #I I<br />

D D0<br />

= 2<br />

#UGS UP U P (U GS<br />

U P<br />

= 2<br />

U P<br />

I D 'I D0<br />

dI G " 0<br />

dI<br />

D<br />

= S # dU<br />

GS<br />

+ 1<br />

# dU<br />

r DS<br />

DS<br />

05.12.2009 Hartmut Gemmeke, WS2009/2010, <strong>E<strong>in</strong>führung</strong> <strong>in</strong> <strong>die</strong> <strong>Elektronik</strong>, Vorlesung 11 11<br />

!<br />

r DSon "50 # 200$<br />

S FET < 10mA<br />

V , S BipolarTr<br />

Stromgegenkopplung bei Sourceschaltung<br />

• Arbeitspunkte<strong>in</strong>stellung durch Gleichstromgegenkopplung<br />

Stromgegenkopplung wird <strong>für</strong> ' > R S(C S aufgehoben<br />

Arbeitspunkt gegeben durch I D und U G=0<br />

V u= = "U a<br />

"U e<br />

z.B.: I D0 = 10 mA,<br />

I D = 3 mA,<br />

U P = -3V<br />

=><br />

= #dI D $R D r DS<br />

dU GS +dI D $R S<br />

V u= = # S$R D r DS<br />

1+S$R S<br />

V u% = #S $ R D r DS (R S & Z S<br />

[ ]<br />

[ ]<br />

V u= = !1,4" R D k#<br />

V u $ = !3,7 "R D k#<br />

= #dUGS $S$RD rDS dUGS $ ( 1+S$RS )<br />

'>R SC S ( ( ( & 0)<br />

05.12.2009 Hartmut Gemmeke, WS2009/2010, <strong>E<strong>in</strong>führung</strong> <strong>in</strong> <strong>die</strong> <strong>Elektronik</strong>, Vorlesung 11 12<br />

!<br />

"U = UP # 1$<br />

GS I % (<br />

' D<br />

'<br />

*<br />

& I *<br />

D0 )<br />

= $3V # 1$ 3mA % (<br />

' * = $1,36V<br />

& 10mA )<br />

"R S = U GS<br />

I D<br />

S = 2<br />

U P<br />

!<br />

= 1,36V<br />

+ 450,<br />

3mA<br />

S = "I D<br />

"U GS<br />

# ID0 #ID = 2<br />

mA<br />

# 10mA#3mA = 3,7<br />

3V V<br />

% 1A<br />

V

!<br />

!<br />

!<br />

Sourcefolger (Dra<strong>in</strong>schaltung)<br />

Verstärkung wie beim Bipolartransistor als Emitterfolger!<br />

R S

Grundschaltungen des FET<br />

05.12.2009 Hartmut Gemmeke, WS2009/2010, <strong>E<strong>in</strong>führung</strong> <strong>in</strong> <strong>die</strong> <strong>Elektronik</strong>, Vorlesung 11 15<br />

Messung der Steuerkennl<strong>in</strong>ie e<strong>in</strong>es JFET‘s<br />

U<br />

GS<br />

= U<br />

P<br />

" 1# I $ '<br />

& D )<br />

&<br />

% I )<br />

D0 (<br />

aus ID =<br />

ID0 UGS #U $ ' 2<br />

& P )<br />

&<br />

% U<br />

)<br />

P (<br />

Der benutzte JFET BF145 ist e<strong>in</strong> n-Kanal<br />

JFET und darf daher nur mit negativer<br />

Gate-Spannung betrieben werden, damit<br />

<strong>die</strong> Gate-Diode gesperrt bleibt!<br />

Der Dra<strong>in</strong>strom I D ergibt sich aus dem<br />

Spannungsabfall u y am bekannten<br />

Source-Widerstand R S als Funktion von<br />

U GS .<br />

Damit lassen sich I D0 und U P bestimmen.<br />

Die maximale Steilheit S max lässt sich<br />

ebenfalls graphisch ablesen und aus der<br />

Formel <strong>für</strong> S=dI D /dU GS =S(U GS , I D0 , U P )<br />

berechnen. Was ergibt der Vergleich?<br />

!<br />

ux=UGS<br />

uy=RS!iD<br />

05.12.2009 Hartmut Gemmeke, WS2009/2010, <strong>E<strong>in</strong>führung</strong> <strong>in</strong> <strong>die</strong> <strong>Elektronik</strong>, Vorlesung 11 16<br />

+<br />

12V<br />

ue

!<br />

!<br />

!<br />

JFET als steuerbarer Widerstand<br />

• Im Anlaufgebiet unterhalb der Kniespannung U K gilt (ohmscher Bereich):<br />

U < U = U<br />

DS K GS "UP , I =<br />

D I D0<br />

2<br />

U<br />

P 2# UGS "U $<br />

2'<br />

& ( P )#UDS "U<br />

%<br />

DS )<br />

(<br />

Kanalwiderstand r DS ist nichtl<strong>in</strong>ear:<br />

r DS<br />

ua = ue "<br />

R1 + rDS r DS = U DS<br />

I D<br />

=<br />

r DSm<strong>in</strong> $ U P<br />

2"I D0<br />

U P 2<br />

( )<br />

ID0 " 2" ( USt #UP )#UDS <strong>für</strong> U St = U GS = 0<br />

U =<br />

GS 1<br />

2 USt +U ( DS),<br />

wenn R " R >> r<br />

2 3 DS<br />

und der quadratische Term <strong>in</strong> U fällt heraus<br />

DS<br />

I =<br />

D ID0 U 2<br />

P USt +U %<br />

2 (<br />

& ( DS)#U<br />

DS $2UP #UDS $UDS) =<br />

'<br />

*<br />

ID0 U 2<br />

P # USt $2U ( P ) #U<br />

DS<br />

r DS = U DS<br />

ID =<br />

Nach L<strong>in</strong>earisierung:<br />

05.12.2009 Hartmut Gemmeke, ! WS2009/2010, <strong>E<strong>in</strong>führung</strong> <strong>in</strong> <strong>die</strong> <strong>Elektronik</strong>, Vorlesung 11 17<br />

U P 2<br />

I D0 (U St $2U P )<br />

Messung der Ausgangskennl<strong>in</strong>ie e<strong>in</strong>es JFETs<br />

• Schaltung zur oszilloskopischen<br />

Darstellung der Ausgangskennl<strong>in</strong>ie<br />

I D = f(U DS) <strong>für</strong> e<strong>in</strong>e konstante<br />

Steuerspannung e<strong>in</strong>es JFETs (R 1 =<br />

!, R 2 = 0)<br />

Der m<strong>in</strong>imale Kanalwiderstand r DS<br />

ist zu bestimmen. Wie gross ist r DS<br />

und wann wird <strong>die</strong>ser Wert erreicht?<br />

1<br />

= 2 k "<br />

• Demonstration der L<strong>in</strong>earitätsverbesserung<br />

im Anlaufbereich des<br />

FETs (R1 = R2 = 1 M")<br />

=> Der FET als e<strong>in</strong>stellbarer<br />

l<strong>in</strong>earer Widerstand <strong>für</strong> R1 ! R2 UGS 2 #U P #U $<br />

'<br />

2<br />

&<br />

DS)<br />

mit k =ID0 /UP %<br />

(<br />

r DS<br />

1:2<br />

05.12.2009 Hartmut Gemmeke, WS2009/2010, <strong>E<strong>in</strong>führung</strong> <strong>in</strong> <strong>die</strong> <strong>Elektronik</strong>, Vorlesung 11 18<br />

-<br />

10k<br />

R2<br />

R1<br />

G<br />

UGS<br />

100<br />

!<br />

D<br />

S<br />

RS<br />

ux=UDS<br />

uy=RS!iD

!<br />

• Arbeitspunktauswahl:<br />

Verstärkungsregelung mit JFET<br />

– kle<strong>in</strong>ster Widerstand von FET N 1 bei U GS = 0V und<br />

größte Verstärkung von T 1 !<br />

– Um symmetrische Aussteuerung<br />

zu ermöglichen, <strong>für</strong> U GS = 0V U a ! 5V<br />

mit Basisvorspannung e<strong>in</strong>regeln! -12V<br />

05.12.2009 Hartmut Gemmeke, WS2009/2010, <strong>E<strong>in</strong>führung</strong> <strong>in</strong> <strong>die</strong> <strong>Elektronik</strong>, Vorlesung 11 19<br />

JFET als Konstantstromquelle<br />

• JFET als Konstantstromquelle ohne Hilfsspannung:<br />

ID = ID0 1" U 2<br />

# &<br />

GS<br />

% ( ,<br />

$ UP '<br />

UGS UP =1"<br />

ID ID0 RS = UGS ID = UP ID #<br />

% 1"<br />

$<br />

I &<br />

D<br />

(<br />

ID 0 '<br />

µ = S) r DS ist <strong>die</strong> maximale Verstärkung, weitgehend unabhängig von I D , da<br />

S = *ID *UGS + ID und rDS = *UDS *ID +1/ ID <strong>in</strong> der Nähe der Kniespannung (11.17)<br />

z.B.: ID =1mA, ID0 =10 mA, UP = "3V, µ = 200<br />

, RS = 3V<br />

1mA 1"<br />

#<br />

%<br />

$<br />

r DS = µ /S = µ ) U P<br />

2 I D 0 ) I D<br />

1mA &<br />

( = 2,05 k-<br />

10 mA '<br />

Za = rDS( 1+ S ) RS) = rDS + µ ) RS = 95 k- + 200 ) 2,05 k- . 500k-<br />

=<br />

200 ) 3V<br />

= 95 k-<br />

2 10 mA )1mA<br />

nach Tietze - Schenk<br />

Innenwiderstand von Bipolar und FET Stromquellen <strong>für</strong> 1mA<br />

05.12.2009 Hartmut Gemmeke, WS2009/2010, <strong>E<strong>in</strong>führung</strong> <strong>in</strong> <strong>die</strong> <strong>Elektronik</strong>, Vorlesung 11 20

!<br />

Zerstörung von FETs durch elektrost. Entladung<br />

• Elektrostatische Aufladung von Personen <strong>in</strong> e<strong>in</strong>er typischen<br />

Arbeitsumgebung: Schaltung soll elektrostatische Aufladung von<br />

zum<strong>in</strong>dest 2kV überstehen:<br />

# Durchbruch des Gateoxyds oder<br />

# Überhitzung der Leiterbahnen<br />

• FET human body model<br />

• E<strong>in</strong>gangswiderstand R e der Schaltung<br />

sehr groß und Kapazität C e sehr kle<strong>in</strong>:<br />

Q = U " C Body = 2000 V "1,510 #10 F = 310 #7 C<br />

$ = R Haut " C Body =1,5 k%"150 pF = 2,2510 #7 s<br />

I = Q/$ &1,5A<br />

• Lösung:<br />

• Schutzdioden<br />

• Schutz gegen ESD* am Arbeitsplatz<br />

* Electrostatic discharge<br />

150pF<br />

05.12.2009 Hartmut Gemmeke, WS2009/2010, <strong>E<strong>in</strong>führung</strong> <strong>in</strong> <strong>die</strong> <strong>Elektronik</strong>, Vorlesung 11 21<br />

2kV<br />

1,5k"