Forschungsbericht 2015

Forschungsbericht 2015 der Technischen Hochschule Ingolstadt (THI)

Forschungsbericht 2015 der Technischen Hochschule Ingolstadt (THI)

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

Luftfahrt<br />

Luftfahrt<br />

PowerPC-based microprocessors) will soon no longer be<br />

available. The following highly integrated components might<br />

serve as alternative solutions:<br />

• Microcontrollers and SoC‘s (Systems on a Chip) are promising<br />

candidates. Especially in the automotive domain high<br />

performance devices with a long availability are available<br />

on the market. Internal RAM and flash memory reduces<br />

the number of pins and therefore production costs as well<br />

as the access time of the processor to the memory. There<br />

are even redundant systems in which pairs of processors<br />

operate in tandem (“lock step architecture”) with source to<br />

sink error correction mechanisms for internal data transfers.<br />

There are, however, some points that need to be clarified:<br />

the integration of aviation-specific interfaces into a reduced<br />

pin count SoC systems and<br />

the analysis on internal concurrent data transfers.<br />

• FPGAs (Field Programmable Gate Array) with embedded<br />

processors offer a high-performance and a flexible integration<br />

of application specific interfaces to the processor core.<br />

In many instances (especially in “soft core” processors),<br />

the computer core itself can be configured to meet specific<br />

application demands. Long-term availability and independence<br />

from hardware distributors is possible if the circuit<br />

design (intellectual property) can be utilized on various<br />

FPGA architectures.<br />

Zugriffszeit des Prozessors auf den Speicher. Es existieren Produkte in<br />

denen sich Paare von Prozessoren in Hardware gegenseitig überwachen<br />

(Lock Step Architektur) und in denen Fehlerkorrekturmechanismen eine<br />

Quellen-zu-Senke – Sicherung der internen Datentransfers übernehmen.<br />

Dennoch gibt es viele offene Punkte wie z. B. die Anbindung Luftfahrtspezifischer<br />

Interfaces an ein Pin-reduziertes SoC oder die Analyse intener,<br />

konkurrierender Datentransfers.<br />

Anforderungen erfüllen und in neue Avionikrechner eingebunden<br />

werden<br />

Können die bereits auf den Microcontrollern vorhandenen<br />

Kommunikationssysteme als CCDL verwendet werden<br />

Welche Möglichkeiten bieten sich, neue Kommunikationssysteme als<br />

CCDL zu entwickeln<br />

• Can the communications systems that are already implemented<br />

on current microcontrollers be used in CCDL applications<br />

• What possibilities are available for the development of new<br />

CCDL communication systems<br />

3. Software Reconfiguration<br />

Cooperative research project “Sagitta”<br />

Cooperation partner: Airbus Defence & Space<br />

In modern aircraft there is a great number of functions<br />

that support the pilot during each phase of flight. Depending<br />

on the phase of the flight and the task to execute, functions<br />

are activated or deactivated by the pilot. Some functions, for<br />

example, might be required during takeoff or landing phases<br />

or some are only required during certain mission phases of<br />

the flight.<br />

When the functions are activated or deactivated there<br />

is a direct relationship with the required calculation time. In<br />

today’s static configuration of multi-core software systems<br />

in aviation and automotive industry, maximum calculation<br />

times are reserved for these functions, as phases are not<br />

considered. In order to use the resources of the computer<br />

platform more effectively, however, the next logical step<br />

would be the development of static software systems configurations<br />

into reconfigurable software systems.<br />

In such reconfigurable software systems, functions are<br />

grouped according to their logical dependencies and then<br />

combined into independent logical<br />

function sets. During runtime the required logical function<br />

sets are loaded dynamically by the scheduler of the Operating<br />

System and the system is accordingly reconfigured.<br />

This reconfiguration makes it possible to use processor<br />

power that is, during this specific phase of flight, not used<br />

by any function and therefore increase the efficiency of the<br />

avionic system.<br />

A scheduler that offers the required reconfiguration<br />

capability is the HAMS, the “Hierarchical Asynchronous<br />

Multicore Scheduler“ with its offline generated knowledgebase<br />

(see figure 2) where predefined functions sets are<br />

defined as software configurations along with the information<br />

regarding the phases. During runtime these phases are<br />

evaluated by the second level scheduler and the appropriate<br />

function sets are loaded into the first level scheduler of the<br />

individual core of the multi-processor system. Any reconfiguration<br />

of functions is executed in real time, i.e. without<br />

missing a time slot.<br />

By software reconfiguration the multi-core processor<br />

can be utilized more efficiently and therefore a smaller multicore<br />

processor can be selected.<br />

FPGAs (Field Programmable Gate Arrays) mit eingebetteten Prozessoren<br />

bieten eine performante und flexible Anbindung von anwendungsspezifischen<br />

Schnittstellen an den Rechnerkern. In vielen Fällen (insbesondere<br />

bei „Soft Core“ Prozessoren) kann auch der Rechnerkern selbst anwendungsspezifisch<br />

konfiguriert werden. Eine langfristige Verfügbarkeit und<br />

eine Unabhängigkeit vom Hardware-Lieferanten ist gegeben, wenn der<br />

Schaltungsentwurf (IP: Intellectual Property) auf unterschiedlichen FPGA-<br />

Strukturen implementiert werden kann.<br />

3. Rekonfigurierbare Software<br />

Kooperatives Forschungsprojekt „Sagitta“<br />

Kooperationspartner Airbus Defence & Space<br />

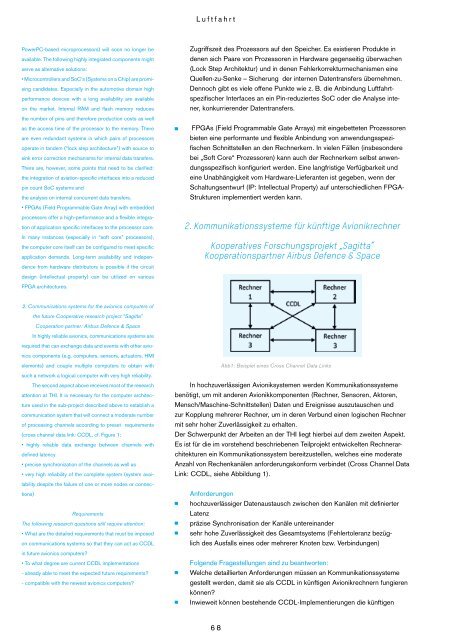

2. Kommunikationssysteme für künftige Avionikrechner<br />

Kooperatives Forschungsprojekt „Sagitta“<br />

Kooperationspartner Airbus Defence & Space<br />

Abb2: Übersicht HAMS Scheduler<br />

2. Communications systems for the avionics computers of<br />

the future Cooperative research project “Sagitta”<br />

Cooperation partner: Airbus Defence & Space<br />

In highly reliable avionics, communications systems are<br />

required that can exchange data and events with other avionics<br />

components (e.g. computers, sensors, actuators, HMI<br />

elements) and couple multiple computers to obtain with<br />

such a network a logical computer with very high reliability.<br />

The second aspect above receives most of the research<br />

attention at THI. It is necessary for the computer architecture<br />

used in the sub-project described above to establish a<br />

communication system that will connect a moderate number<br />

of processing channels according to preset requirements<br />

(cross channel data link: CCDL, cf. Figure 1:<br />

• highly reliable data exchange between channels with<br />

defined latency<br />

• precise synchronization of the channels as well as<br />

• very high reliability of the complete system (system availability<br />

despite the failure of one or more nodes or connections)<br />

Requirements<br />

The following research questions still require attention:<br />

• What are the detailed requirements that must be imposed<br />

on communications systems so that they can act as CCDL<br />

in future avionics computers<br />

• To what degree are current CCDL implementations<br />

- already able to meet the expected future requirements<br />

- compatible with the newest avionics computers<br />

Abb1: Beispiel eines Cross Channel Data Links<br />

In hochzuverlässigen Avioniksystemen werden Kommunikationssysteme<br />

benötigt, um mit anderen Avionikkomponenten (Rechner, Sensoren, Aktoren,<br />

Mensch/Maschine-Schnittstellen) Daten und Ereignisse auszutauschen und<br />

zur Kopplung mehrerer Rechner, um in deren Verbund einen logischen Rechner<br />

mit sehr hoher Zuverlässigkeit zu erhalten.<br />

Der Schwerpunkt der Arbeiten an der THI liegt hierbei auf dem zweiten Aspekt.<br />

Es ist für die im vorstehend beschriebenen Teilprojekt entwickelten Rechnerarchitekturen<br />

ein Kommunikationssystem bereitzustellen, welches eine moderate<br />

Anzahl von Rechenkanälen anforderungskonform verbindet (Cross Channel Data<br />

Link: CCDL, siehe Abbildung 1).<br />

Anforderungen<br />

hochzuverlässiger Datenaustausch zwischen den Kanälen mit definierter<br />

Latenz<br />

präzise Synchronisation der Kanäle untereinander<br />

sehr hohe Zuverlässigkeit des Gesamtsystems (Fehlertoleranz bezüglich<br />

des Ausfalls eines oder mehrerer Knoten bzw. Verbindungen)<br />

Folgende Fragestellungen sind zu beantworten:<br />

Welche detaillierten Anforderungen müssen an Kommunikationssysteme<br />

gestellt werden, damit sie als CCDL in künftigen Avionikrechnern fungieren<br />

können<br />

Inwieweit können bestehende CCDL-Implementierungen die künftigen<br />

In Flugzeugen gibt es eine Vielzahl an Funktionen, die den Luftfahrzeugführer<br />

während seines Fluges in jeder Phase unterstützen können. Diese Funktionen<br />

werden abhängig von der jeweiligen Phase aktiviert oder deaktiviert. So<br />

werden einige Funktionen nur während der Start- oder Landephase, andere<br />

wiederum nur während spezifischer Flugphasen im Missionsgebiet angeboten.<br />

Nachdem die Funktionen nur phasenabhängig aktiviert werden, folgt eine direkte<br />

Abhängigkeit der Rechenzeit einer Funktion von der Phase. In den heutigen<br />

statisch konfigurierten Multi-Core Software Systemen der Luftfahrt- und Automobilindustrie<br />

werden phasenunabhängige maximale Rechenzeiten für diese<br />

Funktionen reserviert. Um die Rechenkapazität einer eingebetteten Rechenplattform<br />

im softwarebasierten System besser auszuschöpfen, ist der nächste<br />

logische Schritt, die statische Software System Konfiguration für das softwarebasierte<br />

System zu einer rekonfigurierbaren Software System Konfiguration<br />

weiterzuentwickeln.<br />

In einem rekonfigurierbaren Software System werden die Funktionen während<br />

der Entwicklung der Softwarearchitektur auf ihre logische Abhängigkeit hin<br />

überprüft und in unabhängige, komplementär rechnende, logische Funktionssets<br />

zusammengefasst. Zur Laufzeit werden phasenabhängig die benötigten logischen<br />

Funktionssets dynamisch vom Scheduler des Betriebssystems geladen<br />

oder entladen und somit das System rekonfiguriert. Durch diese Eigenschaft ist<br />

es möglich, temporär nicht von Funktionen ausgenutzte Rechenzeit phasenabhängig<br />

anderweitig zu nutzen, um das Ziel der höheren Effizienz zu erreichen.<br />

Ein Scheduler, der diese Möglichkeit bietet, ist der „Hierarchische Assynchrone<br />

Multicore Scheduler“ HAMS mit seiner offline generierten Knowledgebase (siehe<br />

Abbildung 2), in der die vorab definierten Softwarekonfigurationen als phasenabhängige<br />

Funktionssets mit den Informationen zu der jeweiligen Phase abgelegt<br />

sind. Zur Laufzeit werden die Phasen in dem Second Level Scheduler bestimmt<br />

und die entsprechenden Funktionssets in die First Level Scheduler der einzelnen<br />

Cores des Mehrprozessorsystems geladen. Eventuell erforderliche Verschiebungen<br />

von Funktionen zwischen Cores werden in Echtzeit, d. h. ohne Ausfall eines<br />

Rechenzyklus, durchgeführt. Durch die dynamische Rekonfiguration können die<br />

Mehrprozessorsysteme besser ausgelastet werden, was wiederum Einsparun-<br />

68 69