Projekte zur Vorlesung Programmierbare Logik im WS06/07 ...

Projekte zur Vorlesung Programmierbare Logik im WS06/07 ...

Projekte zur Vorlesung Programmierbare Logik im WS06/07 ...

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

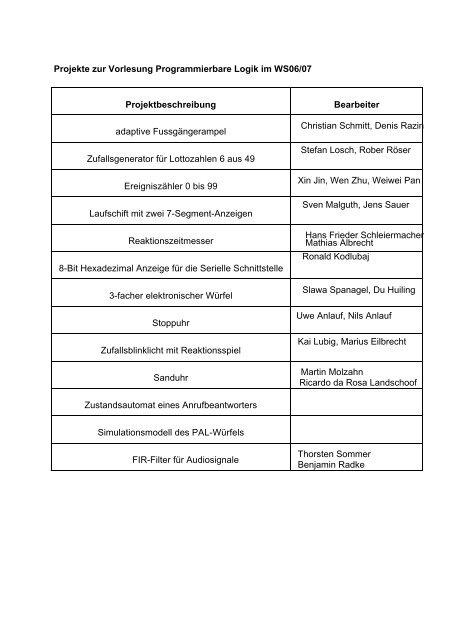

<strong>Projekte</strong> <strong>zur</strong> <strong>Vorlesung</strong> <strong>Programmierbare</strong> <strong>Logik</strong> <strong>im</strong> <strong>WS06</strong>/<strong>07</strong>Projektbeschreibungadaptive FussgängerampelZufallsgenerator für Lottozahlen 6 aus 49Ereigniszähler 0 bis 99Laufschift mit zwei 7-Segment-AnzeigenReaktionszeitmesser8-Bit Hexadez<strong>im</strong>al Anzeige für die Serielle Schnittstelle3-facher elektronischer WürfelStoppuhrZufallsblinklicht mit ReaktionsspielSanduhrBearbeiterChristian Schmitt, Denis RazinStefan Losch, Rober RöserXin Jin, Wen Zhu, Weiwei PanS ven Malguth, Jens SauerHans Frieder SchleiermacherMathias AlbrechtRonald KodlubajSlawa Spanagel, Du HuilingUwe Anlauf, Nils AnlaufKai Lubig, Marius EilbrechtMartin MolzahnRicardo da Rosa LandschoofZustandsautomat eines AnrufbeantwortersS<strong>im</strong>ulationsmodell des PAL-WürfelsFIR-Filter für AudiosignaleThorsten SommerBenjamin Radke

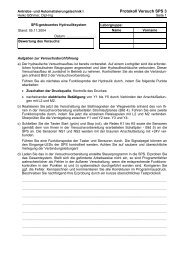

Name: Vorname: Mat.-Nr.: Datum:Name: Vorname: Mat.-Nr.:Entwerfen Sie eine Steuerung für eine adaptive Fussgängerampel.Die Fussgänger bekommen Grün, nachdem sie einen Anforderungsknopf betätigt haben.Bei nochmaliger Anforderung nach Durchlauf einer Grünphase für die Fussgänger ist eineAnsprechverzögerung vorzusehen(=> Bevorzugung der PKW‘s). Die Steuerung ist miteinem Schaltwerk zu realisieren. Es ist ein synchroner Reset vorzusehen.Folgende Komponenten sind zu erstellen:• Beschreibung des Entwurfs (Blockschaltbild/Zustandsdiagramm).• Implementierung des Entwurfs (VHDL Quelltext).• S<strong>im</strong>ulation des Entwurfs (Funktion und/oder Zeitverhalten).Dokumentieren Sie auf max<strong>im</strong>al 4 DIN-A4 Seiten:1. Blockschaltbild oder Zustandsdiagramm des Entwurfs2. das/die Modul/e mit der VHDL-Beschreibung3. das Modul der Testbench (wenn erforderlich)4. das Zeitverhalten anhand eines T<strong>im</strong>ingdiagrammes5. die notwendigen HardwareressourcenAm vereinbarten Termin <strong>zur</strong> Abgabe des Projekts sind folgende Teile vorzustellen, bzw.abzugeben:• Eine mündliche Präsentation (ca. 8 min. pro Person).• Abgabe der schriftlichen Dokumentation von max<strong>im</strong>al 4 DIN-A4 Seiten in Papierform.• Abgabe der schriftlichen Dokumentation und des Projekts auf elektronischemDatenträger.• Funktion des programmierten Baustein auf einem Exper<strong>im</strong>entierboard.Voraussetzungen für die Anerkennung des Entwurfs :• Teilnahme an der Wahlvorlesung "<strong>Programmierbare</strong> <strong>Logik</strong>",• Erfolgreiche Lösung der gestellten Aufgabe (eine für ein bis zwei Teilnehmer),• Saubere und prägnante Dokumentation und Präsentation des Testaufbaus.• Kenntlich machen, welcher Teilnehmer welchen Aufgabenteil gelöst hat.

Name: Vorname: Mat.-Nr.: Datum:Name: Vorname: Mat.-Nr.:Entwerfen Sie einen Zufallsgenerator für Lottozahlen 6 aus 49. Es darf keine Zahlmehrfach "gezogen" werden.Der Zufallgenerator kann mit Hilfe eines Zählers der mit einer Taktfrequenz > 1 kHzarbeitet realisiert werden. Der Zählvorgang wird mit einem Taster manuell gestartet undgestoppt.Folgende Komponenten sind zu erstellen:• Beschreibung des Entwurfs (Blockschaltbild/Zustandsdiagramm).• Implementierung des Entwurfs (VHDL Quelltext).• S<strong>im</strong>ulation des Entwurfs (Funktion und/oder Zeitverhalten).Dokumentieren Sie auf max<strong>im</strong>al 4 DIN-A4 Seiten:1. Blockschaltbild oder Zustandsdiagramm des Entwurfs2. das/die Modul/e mit der VHDL-Beschreibung3. das Modul der Testbench (wenn erforderlich)4. das Zeitverhalten anhand eines T<strong>im</strong>ingdiagrammes5. die notwendigen HardwareressourcenAm vereinbarten Termin <strong>zur</strong> Abgabe des Projekts sind folgende Teile vorzustellen, bzw.abzugeben:• Eine mündliche Präsentation (ca. 8 min. pro Person).• Abgabe der schriftlichen Dokumentation von max<strong>im</strong>al 4 DIN-A4 Seiten in Papierform.• Abgabe der schriftlichen Dokumentation und des Projekts auf elektronischemDatenträger.• Funktion des programmierten Baustein auf einem Exper<strong>im</strong>entierboard.Voraussetzungen für die Anerkennung des Entwurfs :• Teilnahme an der Wahlvorlesung "<strong>Programmierbare</strong> <strong>Logik</strong>",• Erfolgreiche Lösung der gestellten Aufgabe (eine für ein bis zwei Teilnehmer),• Saubere und prägnante Dokumentation und Präsentation des Testaufbaus.• Kenntlich machen, welcher Teilnehmer welchen Aufgabenteil gelöst hat.

Name: Vorname: Mat.-Nr.: Datum:Name: Vorname: Mat.-Nr.:Entwerfen Sie einen Ereigniszähler von 0 bis 99 mit entprelltem Taster. Es soll Vor- undRückwärts gezählt und der Zählstand auf 0 <strong>zur</strong>ückgesetzt oder auf einen wählbaren Wertgesetzt werden können (z.B. durch längeres drücken des Tasters). Zusätzlich zum Tasterist ein externer Eingang vorzusehen.Folgende Komponenten sind zu erstellen:• Beschreibung des Entwurfs (Blockschaltbild/Zustandsdiagramm).• Implementierung des Entwurfs (VHDL Quelltext).• S<strong>im</strong>ulation des Entwurfs (Funktion und/oder Zeitverhalten).Dokumentieren Sie auf max<strong>im</strong>al 4 DIN-A4 Seiten:1. Blockschaltbild oder Zustandsdiagramm des Entwurfs2. das/die Modul/e mit der VHDL-Beschreibung3. das Modul der Testbench (wenn erforderlich)4. das Zeitverhalten anhand eines T<strong>im</strong>ingdiagrammes5. die notwendigen HardwareressourcenAm vereinbarten Termin <strong>zur</strong> Abgabe des Projekts sind folgende Teile vorzustellen, bzw.abzugeben:• Eine mündliche Präsentation (ca. 8 min. pro Person).• Abgabe der schriftlichen Dokumentation von max<strong>im</strong>al 4 DIN-A4 Seiten in Papierform.• Abgabe der schriftlichen Dokumentation und des Projekts auf elektronischemDatenträger.• Funktion des programmierten Baustein auf einem Exper<strong>im</strong>entierboard.Voraussetzungen für die Anerkennung des Entwurfs :• Teilnahme an der Wahlvorlesung "<strong>Programmierbare</strong> <strong>Logik</strong>",• Erfolgreiche Lösung der gestellten Aufgabe (eine für ein bis zwei Teilnehmer),• Saubere und prägnante Dokumentation und Präsentation des Testaufbaus.• Kenntlich machen, welcher Teilnehmer welchen Aufgabenteil gelöst hat.

Name: Vorname: Mat.-Nr.: Datum:Name: Vorname: Mat.-Nr.:Entwerfen Sie die Ansteuerung für eine Laufschriftanzeige mit zwei 7-Segment-Anzeigen.Es ist ein fest programmierter Text auszugeben. Z.B. „VHDL-Projekt“ oder„Bearbeitername“. Dafür ist eine selbst definierte Zeichentabelle mit den benutztenZeichen für die 7-Segment-Anzeigen zu erstellen.Folgende Komponenten sind zu erstellen:• Beschreibung des Entwurfs (Blockschaltbild/Zustandsdiagramm).• Implementierung des Entwurfs (VHDL Quelltext).• S<strong>im</strong>ulation des Entwurfs (Funktion und/oder Zeitverhalten).Dokumentieren Sie auf max<strong>im</strong>al 4 DIN-A4 Seiten:1. Blockschaltbild oder Zustandsdiagramm des Entwurfs2. das/die Modul/e mit der VHDL-Beschreibung3. das Modul der Testbench (wenn erforderlich)4. das Zeitverhalten anhand eines T<strong>im</strong>ingdiagrammes5. die notwendigen HardwareressourcenAm vereinbarten Termin <strong>zur</strong> Abgabe des Projekts sind folgende Teile vorzustellen, bzw.abzugeben:• Eine mündliche Präsentation (ca. 8 min. pro Person).• Abgabe der schriftlichen Dokumentation von max<strong>im</strong>al 4 DIN-A4 Seiten in Papierform.• Abgabe der schriftlichen Dokumentation und des Projekts auf elektronischemDatenträger.• Funktion des programmierten Baustein auf einem Exper<strong>im</strong>entierboard.Voraussetzungen für die Anerkennung des Entwurfs :• Teilnahme an der Wahlvorlesung "<strong>Programmierbare</strong> <strong>Logik</strong>",• Erfolgreiche Lösung der gestellten Aufgabe (eine für ein bis zwei Teilnehmer),• Saubere und prägnante Dokumentation und Präsentation des Testaufbaus.• Kenntlich machen, welcher Teilnehmer welchen Aufgabenteil gelöst hat.

Name: Vorname: Mat.-Nr.: Datum:Name: Vorname: Mat.-Nr.:Entwerfen Sie einen Reaktionszeitmesser.Nach dem Aufleuchten eines Startsignals wird die Zeit bis zum Betätigen des Tastersbest<strong>im</strong>mt und ausgegeben. "Fehlstarts" sind zu erkennen und anzuzeigen.Folgende Komponenten sind zu erstellen:• Beschreibung des Entwurfs (Blockschaltbild/Zustandsdiagramm).• Implementierung des Entwurfs (VHDL Quelltext).• S<strong>im</strong>ulation des Entwurfs (Funktion und/oder Zeitverhalten).Dokumentieren Sie auf max<strong>im</strong>al 4 DIN-A4 Seiten:1. Blockschaltbild oder Zustandsdiagramm des Entwurfs2. das/die Modul/e mit der VHDL-Beschreibung3. das Modul der Testbench (wenn erforderlich)4. das Zeitverhalten anhand eines T<strong>im</strong>ingdiagrammes5. die notwendigen HardwareressourcenAm vereinbarten Termin <strong>zur</strong> Abgabe des Projekts sind folgende Teile vorzustellen, bzw.abzugeben:• Eine mündliche Präsentation (ca. 8 min. pro Person).• Abgabe der schriftlichen Dokumentation von max<strong>im</strong>al 4 DIN-A4 Seiten in Papierform.• Abgabe der schriftlichen Dokumentation und des Projekts auf elektronischemDatenträger.• Funktion des programmierten Baustein auf einem Exper<strong>im</strong>entierboard.Voraussetzungen für die Anerkennung des Entwurfs :• Teilnahme an der Wahlvorlesung "<strong>Programmierbare</strong> <strong>Logik</strong>",• Erfolgreiche Lösung der gestellten Aufgabe (eine für ein bis zwei Teilnehmer),• Saubere und prägnante Dokumentation und Präsentation des Testaufbaus.• Kenntlich machen, welcher Teilnehmer welchen Aufgabenteil gelöst hat.

Name: Vorname: Mat.-Nr.: Datum:Name: Vorname: Mat.-Nr.:Entwerfen Sie eine Schaltung <strong>zur</strong> Anzeige von 8-Bit <strong>im</strong> Hexadez<strong>im</strong>alcode, die über dieserielle Schnittstelle an das Exper<strong>im</strong>entierboard übertragen werden.Folgende Komponenten sind zu erstellen:• Beschreibung des Entwurfs (Blockschaltbild/Zustandsdiagramm).• Implementierung des Entwurfs (VHDL Quelltext).• S<strong>im</strong>ulation des Entwurfs (Funktion und/oder Zeitverhalten).Dokumentieren Sie auf max<strong>im</strong>al 4 DIN-A4 Seiten:1. Blockschaltbild oder Zustandsdiagramm des Entwurfs2. das/die Modul/e mit der VHDL-Beschreibung3. das Modul der Testbench (wenn erforderlich)4. das Zeitverhalten anhand eines T<strong>im</strong>ingdiagrammes5. die notwendigen HardwareressourcenAm vereinbarten Termin <strong>zur</strong> Abgabe des Projekts sind folgende Teile vorzustellen, bzw.abzugeben:• Eine mündliche Präsentation (ca. 8 min. pro Person).• Abgabe der schriftlichen Dokumentation von max<strong>im</strong>al 4 DIN-A4 Seiten in Papierform.• Abgabe der schriftlichen Dokumentation und des Projekts auf elektronischemDatenträger.• Funktion des programmierten Baustein auf einem Exper<strong>im</strong>entierboard.Voraussetzungen für die Anerkennung des Entwurfs :• Teilnahme an der Wahlvorlesung "<strong>Programmierbare</strong> <strong>Logik</strong>",• Erfolgreiche Lösung der gestellten Aufgabe (eine für ein bis zwei Teilnehmer),• Saubere und prägnante Dokumentation und Präsentation des Testaufbaus.• Kenntlich machen, welcher Teilnehmer welchen Aufgabenteil gelöst hat.

Name: Vorname: Mat.-Nr.: Datum:Name: Vorname: Mat.-Nr.:Entwerfen Sie einen 3-fachen elektronischen Würfel mit Anzeige der gewürfeltenAugenzahl über die 7-Segment-Anzeige.Folgende Komponenten sind zu erstellen:• Beschreibung des Entwurfs (Blockschaltbild/Zustandsdiagramm).• Implementierung des Entwurfs (VHDL Quelltext).• S<strong>im</strong>ulation des Entwurfs (Funktion und/oder Zeitverhalten).Dokumentieren Sie auf max<strong>im</strong>al 4 DIN-A4 Seiten:1. Blockschaltbild oder Zustandsdiagramm des Entwurfs2. das/die Modul/e mit der VHDL-Beschreibung3. das Modul der Testbench (wenn erforderlich)4. das Zeitverhalten anhand eines T<strong>im</strong>ingdiagrammes5. die notwendigen HardwareressourcenAm vereinbarten Termin <strong>zur</strong> Abgabe des Projekts sind folgende Teile vorzustellen, bzw.abzugeben:• Eine mündliche Präsentation (ca. 8 min. pro Person).• Abgabe der schriftlichen Dokumentation von max<strong>im</strong>al 4 DIN-A4 Seiten in Papierform.• Abgabe der schriftlichen Dokumentation und des Projekts auf elektronischemDatenträger.• Funktion des programmierten Baustein auf einem Exper<strong>im</strong>entierboard.Voraussetzungen für die Anerkennung des Entwurfs :• Teilnahme an der Wahlvorlesung "<strong>Programmierbare</strong> <strong>Logik</strong>",• Erfolgreiche Lösung der gestellten Aufgabe (eine für ein bis zwei Teilnehmer),• Saubere und prägnante Dokumentation und Präsentation des Testaufbaus.• Kenntlich machen, welcher Teilnehmer welchen Aufgabenteil gelöst hat.

Name: Vorname: Mat.-Nr.: Datum:Name: Vorname: Mat.-Nr.:Entwerfen Sie eine Stoppuhr, deren Anzeige automatisch zwischen hundertstel Sekundenund Sekunden umschaltet. Alle Funktionen wie Start, Stop und Zurücksetzen sind übereinen Taster zu realisieren.Folgende Komponenten sind zu erstellen:• Beschreibung des Entwurfs (Blockschaltbild/Zustandsdiagramm).• Implementierung des Entwurfs (VHDL Quelltext).• S<strong>im</strong>ulation des Entwurfs (Funktion und/oder Zeitverhalten).Dokumentieren Sie auf max<strong>im</strong>al 4 DIN-A4 Seiten:1. Blockschaltbild oder Zustandsdiagramm des Entwurfs2. das/die Modul/e mit der VHDL-Beschreibung3. das Modul der Testbench (wenn erforderlich)4. das Zeitverhalten anhand eines T<strong>im</strong>ingdiagrammes5. die notwendigen HardwareressourcenAm vereinbarten Termin <strong>zur</strong> Abgabe des Projekts sind folgende Teile vorzustellen, bzw.abzugeben:• Eine mündliche Präsentation (ca. 8 min. pro Person).• Abgabe der schriftlichen Dokumentation von max<strong>im</strong>al 4 DIN-A4 Seiten in Papierform.• Abgabe der schriftlichen Dokumentation und des Projekts auf elektronischemDatenträger.• Funktion des programmierten Baustein auf einem Exper<strong>im</strong>entierboard.Voraussetzungen für die Anerkennung des Entwurfs :• Teilnahme an der Wahlvorlesung "<strong>Programmierbare</strong> <strong>Logik</strong>",• Erfolgreiche Lösung der gestellten Aufgabe (eine für ein bis zwei Teilnehmer),• Saubere und prägnante Dokumentation und Präsentation des Testaufbaus.• Kenntlich machen, welcher Teilnehmer welchen Aufgabenteil gelöst hat.

Name: Vorname: Mat.-Nr.: Datum:Name: Vorname: Mat.-Nr.:Entwerfen Sie ein Zufallsblinklicht mit Reaktionsspiel, bei dem der Taster be<strong>im</strong>Aufleuchten eines best<strong>im</strong>mten Segments der 7-Segment-Anzeigen betätigt werden muss.Folgende Komponenten sind zu erstellen:• Beschreibung des Entwurfs (Blockschaltbild/Zustandsdiagramm).• Implementierung des Entwurfs (VHDL Quelltext).• S<strong>im</strong>ulation des Entwurfs (Funktion und/oder Zeitverhalten).Dokumentieren Sie auf max<strong>im</strong>al 4 DIN-A4 Seiten:1. Blockschaltbild oder Zustandsdiagramm des Entwurfs2. das/die Modul/e mit der VHDL-Beschreibung3. das Modul der Testbench (wenn erforderlich)4. das Zeitverhalten anhand eines T<strong>im</strong>ingdiagrammes5. die notwendigen HardwareressourcenAm vereinbarten Termin <strong>zur</strong> Abgabe des Projekts sind folgende Teile vorzustellen, bzw.abzugeben:• Eine mündliche Präsentation (ca. 8 min. pro Person).• Abgabe der schriftlichen Dokumentation von max<strong>im</strong>al 4 DIN-A4 Seiten in Papierform.• Abgabe der schriftlichen Dokumentation und des Projekts auf elektronischemDatenträger.• Funktion des programmierten Baustein auf einem Exper<strong>im</strong>entierboard.Voraussetzungen für die Anerkennung des Entwurfs :• Teilnahme an der Wahlvorlesung "<strong>Programmierbare</strong> <strong>Logik</strong>",• Erfolgreiche Lösung der gestellten Aufgabe (eine für ein bis zwei Teilnehmer),• Saubere und prägnante Dokumentation und Präsentation des Testaufbaus.• Kenntlich machen, welcher Teilnehmer welchen Aufgabenteil gelöst hat.

Name: Vorname: Mat.-Nr.: Datum:Name: Vorname: Mat.-Nr.:Entwerfen Sie eine Sanduhr, deren Ablaufzeit über die Zeit die der Starttasterfestgehalten wird zu programmieren ist. Visualisieren Sie den Ablauf der Zeit mit denbeiden 7-Segment LED-Anzeigen.Folgende Komponenten sind zu erstellen:• Beschreibung des Entwurfs (Blockschaltbild/Zustandsdiagramm).• Implementierung des Entwurfs (VHDL Quelltext).• S<strong>im</strong>ulation des Entwurfs (Funktion und/oder Zeitverhalten).Dokumentieren Sie auf max<strong>im</strong>al 4 DIN-A4 Seiten:1. Blockschaltbild oder Zustandsdiagramm des Entwurfs2. das/die Modul/e mit der VHDL-Beschreibung3. das Modul der Testbench (wenn erforderlich)4. das Zeitverhalten anhand eines T<strong>im</strong>ingdiagrammes5. die notwendigen HardwareressourcenAm vereinbarten Termin <strong>zur</strong> Abgabe des Projekts sind folgende Teile vorzustellen, bzw.abzugeben:• Eine mündliche Präsentation (ca. 8 min. pro Person).• Abgabe der schriftlichen Dokumentation von max<strong>im</strong>al 4 DIN-A4 Seiten in Papierform.• Abgabe der schriftlichen Dokumentation und des Projekts auf elektronischemDatenträger.• Funktion des programmierten Baustein auf einem Exper<strong>im</strong>entierboard.Voraussetzungen für die Anerkennung des Entwurfs :• Teilnahme an der Wahlvorlesung "<strong>Programmierbare</strong> <strong>Logik</strong>",• Erfolgreiche Lösung der gestellten Aufgabe (eine für ein bis zwei Teilnehmer),• Saubere und prägnante Dokumentation und Präsentation des Testaufbaus.• Kenntlich machen, welcher Teilnehmer welchen Aufgabenteil gelöst hat.

Name: Vorname: Mat.-Nr.: Datum:Name: Vorname: Mat.-Nr.:Entwerfen Sie einen Zustandsautomaten für einen Anrufbeantworter. Der aktuelleZustand ist auf der LED-Anzeige zu visualisieren.Folgende Komponenten sind zu erstellen:• Beschreibung des Entwurfs (Blockschaltbild/Zustandsdiagramm).• Implementierung des Entwurfs (VHDL Quelltext).• S<strong>im</strong>ulation des Entwurfs (Funktion und/oder Zeitverhalten).Dokumentieren Sie auf max<strong>im</strong>al 4 DIN-A4 Seiten:1. Blockschaltbild oder Zustandsdiagramm des Entwurfs2. das/die Modul/e mit der VHDL-Beschreibung3. das Modul der Testbench (wenn erforderlich)4. das Zeitverhalten anhand eines T<strong>im</strong>ingdiagrammes5. die notwendigen HardwareressourcenAm vereinbarten Termin <strong>zur</strong> Abgabe des Projekts sind folgende Teile vorzustellen, bzw.abzugeben:• Eine mündliche Präsentation (ca. 8 min. pro Person).• Abgabe der schriftlichen Dokumentation von max<strong>im</strong>al 4 DIN-A4 Seiten in Papierform.• Abgabe der schriftlichen Dokumentation und des Projekts auf elektronischemDatenträger.• Funktion des programmierten Baustein auf einem Exper<strong>im</strong>entierboard.Voraussetzungen für die Anerkennung des Entwurfs :• Teilnahme an der Wahlvorlesung "<strong>Programmierbare</strong> <strong>Logik</strong>",• Erfolgreiche Lösung der gestellten Aufgabe (eine für ein bis zwei Teilnehmer),• Saubere und prägnante Dokumentation und Präsentation des Testaufbaus.• Kenntlich machen, welcher Teilnehmer welchen Aufgabenteil gelöst hat.

Name: Vorname: Mat.-Nr.: Datum:Name: Vorname: Mat.-Nr.:Entwerfen Sie ein S<strong>im</strong>ulationsmodell für den elektronischen PAL-Würfel aus Kapitel 1, derdie Funktion und das Zeitverhalten <strong>im</strong> XC9572XL-10 CPLD des Exper<strong>im</strong>entierboardsautomatisch untersucht und anzeigt (z.B. mit Assert Anweisungen).Folgende Komponenten sind zu erstellen:• Beschreibung des Entwurfs (Blockschaltbild/Zustandsdiagramm).• Implementierung des Entwurfs (VHDL Quelltext).• S<strong>im</strong>ulation des Entwurfs (Funktion und/oder Zeitverhalten).Dokumentieren Sie auf max<strong>im</strong>al 4 DIN-A4 Seiten:1. Blockschaltbild oder Zustandsdiagramm des Entwurfs2. das/die Modul/e mit der VHDL-Beschreibung3. das Modul der Testbench (wenn erforderlich)4. das Zeitverhalten anhand eines T<strong>im</strong>ingdiagrammes5. die notwendigen HardwareressourcenAm vereinbarten Termin <strong>zur</strong> Abgabe des Projekts sind folgende Teile vorzustellen, bzw.abzugeben:• Eine mündliche Präsentation (ca. 8 min. pro Person).• Abgabe der schriftlichen Dokumentation von max<strong>im</strong>al 4 DIN-A4 Seiten in Papierform.• Abgabe der schriftlichen Dokumentation und des Projekts auf elektronischemDatenträger.• Funktion des programmierten Baustein auf einem Exper<strong>im</strong>entierboard.Voraussetzungen für die Anerkennung des Entwurfs :• Teilnahme an der Wahlvorlesung "<strong>Programmierbare</strong> <strong>Logik</strong>",• Erfolgreiche Lösung der gestellten Aufgabe (eine für ein bis zwei Teilnehmer),• Saubere und prägnante Dokumentation und Präsentation des Testaufbaus.• Kenntlich machen, welcher Teilnehmer welchen Aufgabenteil gelöst hat.

Name: Vorname: Mat.-Nr.: Datum:Name: Vorname: Mat.-Nr.:Entwerfen Sie ein selbst gestelltes Projekt. Der Anforderungsgrad ist mit dem Prüferabzust<strong>im</strong>men.Folgende Komponenten sind zu erstellen:• Beschreibung des Entwurfs (Blockschaltbild/Zustandsdiagramm).• Implementierung des Entwurfs (VHDL Quelltext).• S<strong>im</strong>ulation des Entwurfs (Funktion und/oder Zeitverhalten).Dokumentieren Sie auf max<strong>im</strong>al 4 DIN-A4 Seiten:1. Blockschaltbild oder Zustandsdiagramm des Entwurfs2. das/die Modul/e mit der VHDL-Beschreibung3. das Modul der Testbench (wenn erforderlich)4. das Zeitverhalten anhand eines T<strong>im</strong>ingdiagrammes5. die notwendigen HardwareressourcenAm vereinbarten Termin <strong>zur</strong> Abgabe des Projekts sind folgende Teile vorzustellen, bzw.abzugeben:• Eine mündliche Präsentation (ca. 8 min. pro Person).• Abgabe der schriftlichen Dokumentation von max<strong>im</strong>al 4 DIN-A4 Seiten in Papierform.• Abgabe der schriftlichen Dokumentation und des Projekts auf elektronischemDatenträger.• Funktion des programmierten Baustein auf einem Exper<strong>im</strong>entierboard.Voraussetzungen für die Anerkennung des Entwurfs :• Teilnahme an der Wahlvorlesung "<strong>Programmierbare</strong> <strong>Logik</strong>",• Erfolgreiche Lösung der gestellten Aufgabe (eine für ein bis zwei Teilnehmer),• Saubere und prägnante Dokumentation und Präsentation des Testaufbaus.• Kenntlich machen, welcher Teilnehmer welchen Aufgabenteil gelöst hat.