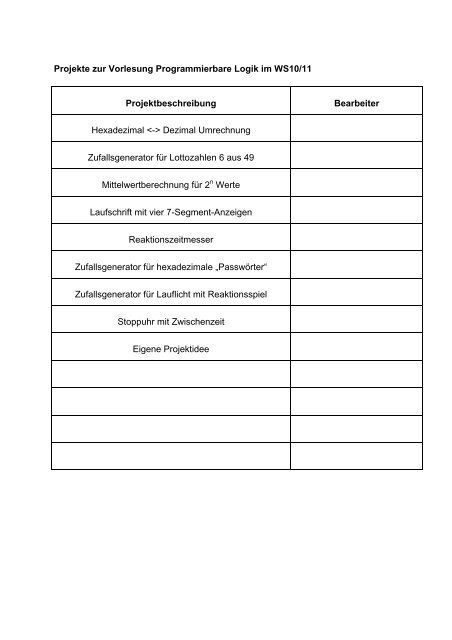

Projekte zur Vorlesung Programmierbare Logik im WS10/11 ...

Projekte zur Vorlesung Programmierbare Logik im WS10/11 ...

Projekte zur Vorlesung Programmierbare Logik im WS10/11 ...

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

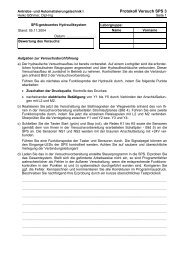

Name: Vorname: Mat.-Nr.: Datum:Name: Vorname: Mat.-Nr.:Entwerfen Sie eine Steuerung für eine Schaltwerk (Zähler) der vom Hexadez<strong>im</strong>al- in dasDez<strong>im</strong>al-System und umgekehrt umrechnet. Die Zwischenergebnisse sollten angezeigtwerden, so dass die Funktion der Schaltung verfolgt werden kann.Folgende Komponenten sind zu erstellen:• Beschreibung des Entwurfs (Blockschaltbild/Zustandsdiagramm).• Implementierung des Entwurfs (VHDL Quelltext).Dokumentieren Sie auf max<strong>im</strong>al 4 DIN-A4 Seiten:1. Blockschaltbild und/oder Zustandsdiagramm des Entwurfs2. das/die Modul/e mit der VHDL-Beschreibung3. die notwendigen HardwareressourcenAm vereinbarten Termin <strong>zur</strong> Abgabe des Projekts sind folgende Teile vorzustellen, bzw.abzugeben:• Eine mündliche Präsentation (ca. 8 min. pro Person).• Abgabe der schriftlichen Dokumentation von max<strong>im</strong>al 4 DIN-A4 Seiten in Papierform.• Abgabe der schriftlichen Dokumentation und des Projekts auf elektronischemDatenträger oder <strong>im</strong> StudIP.• Funktion des programmierten Baustein auf einem Exper<strong>im</strong>entierboard.Voraussetzungen für die Anerkennung des Entwurfs :• Teilnahme an der Wahlvorlesung "<strong>Programmierbare</strong> <strong>Logik</strong>",• Erfolgreiche Lösung der gestellten Aufgabe (eine für ein bis zwei Teilnehmer),• Saubere und prägnante Dokumentation und Präsentation des Testaufbaus.• Kenntlich machen, welcher Teilnehmer welchen Aufgabenteil gelöst hat.

Name: Vorname: Mat.-Nr.: Datum:Name: Vorname: Mat.-Nr.:Entwerfen Sie einen Zufallsgenerator für Lottozahlen 6 aus 49. Es darf keine Zahlmehrfach "gezogen" werden.Folgende Komponenten sind zu erstellen:• Beschreibung des Entwurfs (Blockschaltbild/Zustandsdiagramm).• Implementierung des Entwurfs (VHDL Quelltext).Dokumentieren Sie auf max<strong>im</strong>al 4 DIN-A4 Seiten:1. Blockschaltbild und/oder Zustandsdiagramm des Entwurfs2. das/die Modul/e mit der VHDL-Beschreibung3. die notwendigen HardwareressourcenAm vereinbarten Termin <strong>zur</strong> Abgabe des Projekts sind folgende Teile vorzustellen, bzw.abzugeben:• Eine mündliche Präsentation (ca. 8 min. pro Person).• Abgabe der schriftlichen Dokumentation von max<strong>im</strong>al 4 DIN-A4 Seiten in Papierform.• Abgabe der schriftlichen Dokumentation und des Projekts auf elektronischemDatenträger oder <strong>im</strong> StudIP.• Funktion des programmierten Baustein auf einem Exper<strong>im</strong>entierboard.Voraussetzungen für die Anerkennung des Entwurfs :• Teilnahme an der Wahlvorlesung "<strong>Programmierbare</strong> <strong>Logik</strong>",• Erfolgreiche Lösung der gestellten Aufgabe (eine für ein bis zwei Teilnehmer),• Saubere und prägnante Dokumentation und Präsentation des Testaufbaus.• Kenntlich machen, welcher Teilnehmer welchen Aufgabenteil gelöst hat.

Name: Vorname: Mat.-Nr.: Datum:Name: Vorname: Mat.-Nr.:Entwerfen Sie eine Mittelwertberechung die für eine Reihe von zeitlichaufeinanderfolgenden Hexadez<strong>im</strong>alzahlen den Mittelwert best<strong>im</strong>mt. Es kann <strong>im</strong>mer nurAnzahl an Zahlen die ein ganzzahliges Vielfaches von 2 ist verarbeitet werden.Der Entwurf sollte so erfolgen, dass die Funktion über die Siebensegmentanzeige verfolgtwerden kann.Folgende Komponenten sind zu erstellen:• Beschreibung des Entwurfs (Blockschaltbild/Zustandsdiagramm).• Implementierung des Entwurfs (VHDL Quelltext).Dokumentieren Sie auf max<strong>im</strong>al 4 DIN-A4 Seiten:1. Blockschaltbild und/oder Zustandsdiagramm des Entwurfs2. das/die Modul/e mit der VHDL-Beschreibung3. die notwendigen HardwareressourcenAm vereinbarten Termin <strong>zur</strong> Abgabe des Projekts sind folgende Teile vorzustellen, bzw.abzugeben:• Eine mündliche Präsentation (ca. 8 min. pro Person).• Abgabe der schriftlichen Dokumentation von max<strong>im</strong>al 4 DIN-A4 Seiten in Papierform.• Abgabe der schriftlichen Dokumentation und des Projekts auf elektronischemDatenträger oder <strong>im</strong> StudIP.• Funktion des programmierten Baustein auf einem Exper<strong>im</strong>entierboard.•Voraussetzungen für die Anerkennung des Entwurfs :• Teilnahme an der Wahlvorlesung "<strong>Programmierbare</strong> <strong>Logik</strong>",• Erfolgreiche Lösung der gestellten Aufgabe (eine für ein bis zwei Teilnehmer),• Saubere und prägnante Dokumentation und Präsentation des Testaufbaus.• Kenntlich machen, welcher Teilnehmer welchen Aufgabenteil gelöst hat.

Name: Vorname: Mat.-Nr.: Datum:Name: Vorname: Mat.-Nr.:Entwerfen Sie die Ansteuerung für eine Laufschrift mit vier 7-Segment-Anzeigen.Es ist ein fest programmierter Text vorwärts oder rückwärts laufend auszugeben. Z.B.„VHDL-Projekt“ oder „Bearbeitername“. Dafür ist eine selbst definierte Zeichentabelle mitden benutzten Zeichen für die 7-Segment-Anzeigen zu erstellen.Folgende Komponenten sind zu erstellen:• Beschreibung des Entwurfs (Blockschaltbild/Zustandsdiagramm).• Implementierung des Entwurfs (VHDL Quelltext).Dokumentieren Sie auf max<strong>im</strong>al 4 DIN-A4 Seiten:1. Blockschaltbild und/oder Zustandsdiagramm des Entwurfs2. das/die Modul/e mit der VHDL-Beschreibung3. die notwendigen HardwareressourcenAm vereinbarten Termin <strong>zur</strong> Abgabe des Projekts sind folgende Teile vorzustellen, bzw.abzugeben:• Eine mündliche Präsentation (ca. 8 min. pro Person).• Abgabe der schriftlichen Dokumentation von max<strong>im</strong>al 4 DIN-A4 Seiten in Papierform.• Abgabe der schriftlichen Dokumentation und des Projekts auf elektronischemDatenträger oder <strong>im</strong> StudIP.• Funktion des programmierten Baustein auf einem Exper<strong>im</strong>entierboard.Voraussetzungen für die Anerkennung des Entwurfs :• Teilnahme an der Wahlvorlesung "<strong>Programmierbare</strong> <strong>Logik</strong>",• Erfolgreiche Lösung der gestellten Aufgabe (eine für ein bis zwei Teilnehmer),• Saubere und prägnante Dokumentation und Präsentation des Testaufbaus.• Kenntlich machen, welcher Teilnehmer welchen Aufgabenteil gelöst hat.

Name: Vorname: Mat.-Nr.: Datum:Name: Vorname: Mat.-Nr.:Entwerfen Sie einen Reaktionszeitmesser.Nach dem Aufleuchten eines manuell erzeugten Startsignals wird die Zeit bis zumBetätigen des Tasters best<strong>im</strong>mt und ausgegeben. "Fehlstarts" sind zu erkennen undanzuzeigen.Folgende Komponenten sind zu erstellen:• Beschreibung des Entwurfs (Blockschaltbild/Zustandsdiagramm).• Implementierung des Entwurfs (VHDL Quelltext).Dokumentieren Sie auf max<strong>im</strong>al 4 DIN-A4 Seiten:1. Blockschaltbild und/oder Zustandsdiagramm des Entwurfs2. das/die Modul/e mit der VHDL-Beschreibung3. die notwendigen HardwareressourcenAm vereinbarten Termin <strong>zur</strong> Abgabe des Projekts sind folgende Teile vorzustellen, bzw.abzugeben:• Eine mündliche Präsentation (ca. 8 min. pro Person).• Abgabe der schriftlichen Dokumentation von max<strong>im</strong>al 4 DIN-A4 Seiten in Papierform.• Abgabe der schriftlichen Dokumentation und des Projekts auf elektronischemDatenträger oder <strong>im</strong> StudIP.• Funktion des programmierten Baustein auf einem Exper<strong>im</strong>entierboard.Voraussetzungen für die Anerkennung des Entwurfs :• Teilnahme an der Wahlvorlesung "<strong>Programmierbare</strong> <strong>Logik</strong>",• Erfolgreiche Lösung der gestellten Aufgabe (eine für ein bis zwei Teilnehmer),• Saubere und prägnante Dokumentation und Präsentation des Testaufbaus.• Kenntlich machen, welcher Teilnehmer welchen Aufgabenteil gelöst hat.

Name: Vorname: Mat.-Nr.: Datum:Name: Vorname: Mat.-Nr.:Entwerfen Sie einen Zufallsgenerator für ein Lauflicht. Die Geschwindigkeit des Lauflichtsmuss einstellbar sein. In einem Reaktionsspiel ist es mit einem Taster zu bestätigen,wenn eine vorgegebene LED aufleuchtet.Folgende Komponenten sind zu erstellen:• Beschreibung des Entwurfs (Blockschaltbild/Zustandsdiagramm).• Implementierung des Entwurfs (VHDL Quelltext).Dokumentieren Sie auf max<strong>im</strong>al 4 DIN-A4 Seiten:1. Blockschaltbild und/oder Zustandsdiagramm des Entwurfs2. das/die Modul/e mit der VHDL-Beschreibung3. die notwendigen HardwareressourcenAm vereinbarten Termin <strong>zur</strong> Abgabe des Projekts sind folgende Teile vorzustellen, bzw.abzugeben:• Eine mündliche Präsentation (ca. 8 min. pro Person).• Abgabe der schriftlichen Dokumentation von max<strong>im</strong>al 4 DIN-A4 Seiten in Papierform.• Abgabe der schriftlichen Dokumentation und des Projekts auf elektronischemDatenträger oder <strong>im</strong> StudIP.• Funktion des programmierten Baustein auf einem Exper<strong>im</strong>entierboard.Voraussetzungen für die Anerkennung des Entwurfs :• Teilnahme an der Wahlvorlesung "<strong>Programmierbare</strong> <strong>Logik</strong>",• Erfolgreiche Lösung der gestellten Aufgabe (eine für ein bis zwei Teilnehmer),• Saubere und prägnante Dokumentation und Präsentation des Testaufbaus.• Kenntlich machen, welcher Teilnehmer welchen Aufgabenteil gelöst hat.

Name: Vorname: Mat.-Nr.: Datum:Name: Vorname: Mat.-Nr.:Entwerfen Sie eine Stoppuhr mit der auch Zwischenzeiten genommen werden könnnen.Folgende Komponenten sind zu erstellen:• Beschreibung des Entwurfs (Blockschaltbild/Zustandsdiagramm).• Implementierung des Entwurfs (VHDL Quelltext).Dokumentieren Sie auf max<strong>im</strong>al 4 DIN-A4 Seiten:1. Blockschaltbild und/oder Zustandsdiagramm des Entwurfs2. das/die Modul/e mit der VHDL-Beschreibung3. die notwendigen HardwareressourcenAm vereinbarten Termin <strong>zur</strong> Abgabe des Projekts sind folgende Teile vorzustellen, bzw.abzugeben:• Eine mündliche Präsentation (ca. 8 min. pro Person).• Abgabe der schriftlichen Dokumentation von max<strong>im</strong>al 4 DIN-A4 Seiten in Papierform.• Abgabe der schriftlichen Dokumentation und des Projekts auf elektronischemDatenträger oder <strong>im</strong> StudIP.• Funktion des programmierten Baustein auf einem Exper<strong>im</strong>entierboard.Voraussetzungen für die Anerkennung des Entwurfs :• Teilnahme an der Wahlvorlesung "<strong>Programmierbare</strong> <strong>Logik</strong>",• Erfolgreiche Lösung der gestellten Aufgabe (eine für ein bis zwei Teilnehmer),• Saubere und prägnante Dokumentation und Präsentation des Testaufbaus.• Kenntlich machen, welcher Teilnehmer welchen Aufgabenteil gelöst hat.

Name: Vorname: Mat.-Nr.: Datum:Name: Vorname: Mat.-Nr.:Entwerfen Sie ein selbst gestelltes Projekt.Der Anforderungsgrad ist mit dem Prüfer abzust<strong>im</strong>men.Folgende Komponenten sind zu erstellen:• Beschreibung des Entwurfs (Blockschaltbild/Zustandsdiagramm).• Implementierung des Entwurfs (VHDL Quelltext).Dokumentieren Sie auf max<strong>im</strong>al 4 DIN-A4 Seiten:1. Blockschaltbild und/oder Zustandsdiagramm des Entwurfs2. das/die Modul/e mit der VHDL-Beschreibung3. die notwendigen HardwareressourcenAm vereinbarten Termin <strong>zur</strong> Abgabe des Projekts sind folgende Teile vorzustellen, bzw.abzugeben:• Eine mündliche Präsentation (ca. 8 min. pro Person).• Abgabe der schriftlichen Dokumentation von max<strong>im</strong>al 4 DIN-A4 Seiten in Papierform.• Abgabe der schriftlichen Dokumentation und des Projekts auf elektronischemDatenträger oder <strong>im</strong> StudIP.• Funktion des programmierten Baustein auf einem Exper<strong>im</strong>entierboard.Voraussetzungen für die Anerkennung des Entwurfs :• Teilnahme an der Wahlvorlesung "<strong>Programmierbare</strong> <strong>Logik</strong>",• Erfolgreiche Lösung der gestellten Aufgabe (eine für ein bis zwei Teilnehmer),• Saubere und prägnante Dokumentation und Präsentation des Testaufbaus.• Kenntlich machen, welcher Teilnehmer welchen Aufgabenteil gelöst hat.