- Page 1 and 2: Zynq-7000 EPP Technical Reference M

- Page 3 and 4: Date Version Revision 06/25/12 1.1

- Page 5 and 6: Chapter 3: Application Processing U

- Page 7 and 8: 6.2.4 Reset Requirements . . . . .

- Page 9 and 10: 10.2.2 Block Diagram . . . . . . .

- Page 11 and 12: 13.2.9 FIFO Overrun and Underrun Co

- Page 13 and 14: 16.1.2 Features . . . . . . . . . .

- Page 15 and 16: Chapter 20: I2C Controller 20.1 Int

- Page 17 and 18: 25.8 GPIO and I2C Clocks . . . . .

- Page 19 and 20: Chapter 31: PCI Express 31.1 Introd

- Page 21 and 22: Introduction 1.1 Overview Chapter 1

- Page 23 and 24: The Zynq-7000 system is composed of

- Page 25 and 26: TrustZone Capabilities Chapter 1: I

- Page 27 and 28: DDR Controller Core and Transaction

- Page 29 and 30: • IEEE 802.3-2008 and IEEE 1588 r

- Page 31 and 32: UART Controllers (Two) Chapter 1: I

- Page 33 and 34: ° ° Chapter 1: Introduction High-

- Page 35 and 36: ° ° Two, 32-bit slave interfaces

- Page 37 and 38: XADC VCCADC, GNDADC N/A Analog powe

- Page 39 and 40: X-Ref Target - Figure 2-2 AHB Maste

- Page 41 and 42: X-Ref Target - Figure 2-3 PS Centra

- Page 43 and 44: • Width of NAND Flash limited to

- Page 45 and 46: Chapter 2: Signals, Interfaces, and

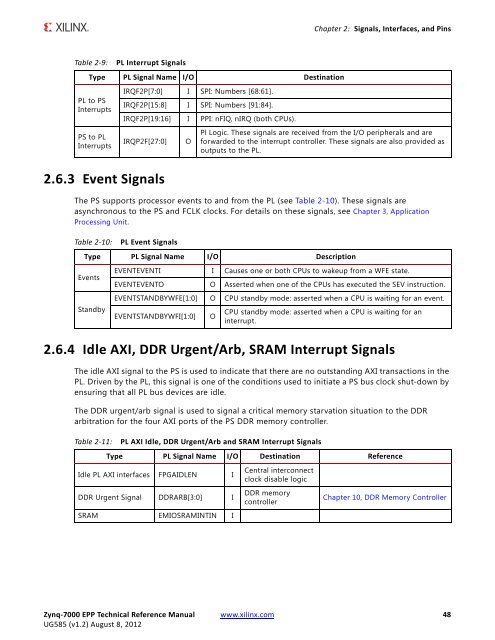

- Page 47: Table 2‐7: PL‐PS Signal Groups

- Page 51 and 52: Application Processing Unit 3.1 Int

- Page 53 and 54: 3.1.2 System‐level View Chapter 3

- Page 55 and 56: 3.2 Cortex A9 Processors 3.2.1 Summ

- Page 57 and 58: Chapter 3: Application Processing U

- Page 59 and 60: Chapter 3: Application Processing U

- Page 61 and 62: Memory Access Sequence When the pro

- Page 63 and 64: A TLB entry matches when these cond

- Page 65 and 66: • Large, shared register file, ad

- Page 67 and 68: Chapter 3: Application Processing U

- Page 69 and 70: Table 3‐1: Cache Controller Behav

- Page 71 and 72: Chapter 3: Application Processing U

- Page 73 and 74: Chapter 3: Application Processing U

- Page 75 and 76: Full Line of Zero Write Chapter 3:

- Page 77 and 78: Chapter 3: Application Processing U

- Page 79 and 80: Table 3‐3: ACP Read and Write Beh

- Page 81 and 82: 3.6 Support for TrustZone Within th

- Page 83 and 84: Chapter 3: Application Processing U

- Page 85 and 86: These are a few notes about the Tru

- Page 87 and 88: Chapter 3: Application Processing U

- Page 89 and 90: Notes: PL AXI Interface Note Chapte

- Page 91 and 92: Table 4‐3: SLCR Register Map (Con

- Page 93 and 94: 4.7 Miscellaneous PS Registers The

- Page 95 and 96: Interconnect Masters The interconne

- Page 97 and 98: L2 Cache Controller Chapter 5: Inte

- Page 99 and 100:

X-Ref Target - Figure 5-2 Chapter 5

- Page 101 and 102:

Table 5‐3: Slave Visible AXI ID V

- Page 103 and 104:

Chapter 5: Interconnect (through L2

- Page 105 and 106:

5.3.3 Functional Description Chapte

- Page 107 and 108:

Table 5‐6: Additional per-port HP

- Page 109 and 110:

Chapter 5: Interconnect For the 32-

- Page 111 and 112:

5.3.9 Performance Optimization Summ

- Page 113 and 114:

5.5 AXI_GP Interfaces 5.5.1 Feature

- Page 115 and 116:

Table 5‐8: AXI Signals Summary (C

- Page 117 and 118:

Table 5‐8: AXI Signals Summary (C

- Page 119 and 120:

Chapter 6: Boot and Configuration

- Page 121 and 122:

Table 6‐2: Boot_Mode Strapping MI

- Page 123 and 124:

Chapter 6: Boot and Configuration J

- Page 125 and 126:

6.3.2 BootROM Header Chapter 6: Boo

- Page 127 and 128:

Start of Execution — Byte Offset

- Page 129 and 130:

Chapter 6: Boot and Configuration G

- Page 131 and 132:

Table 6‐6: NAND MIO Pins Signal N

- Page 133 and 134:

Chapter 6: Boot and Configuration 1

- Page 135 and 136:

Chapter 6: Boot and Configuration T

- Page 137 and 138:

6.3.6 Debug Status Chapter 6: Boot

- Page 139 and 140:

Table 6‐10: BootROM Modified Regi

- Page 141 and 142:

Chapter 6: Boot and Configuration T

- Page 143 and 144:

X-Ref Target - Figure 6-6 pcap_2xcl

- Page 145 and 146:

6.4.4 Device Configuration Flow PS

- Page 147 and 148:

Chapter 6: Boot and Configuration b

- Page 149 and 150:

The configuration flow is: 1. Devic

- Page 151 and 152:

Chapter 6: Boot and Configuration T

- Page 153 and 154:

7.1.1 Private, Shared and Software

- Page 155 and 156:

7.2 Functional Description 7.2.1 So

- Page 157 and 158:

Table 7‐3: PS and PL Shared Perip

- Page 159 and 160:

7.3.1 Write Protection Lock Down Ch

- Page 161 and 162:

Timers 8.1 Introduction Chapter 8 E

- Page 163 and 164:

Chapter 8: Timers Although peripher

- Page 165 and 166:

8.4.2 Block Diagram A block diagram

- Page 167 and 168:

8.5 Triple Timer Counters (TTC) Cha

- Page 169 and 170:

Chapter 8: Timers Overflow mode: Th

- Page 171 and 172:

Chapter 8: Timers 2. Set overflow h

- Page 173 and 174:

DMA Controller 9.1 Introduction Cha

- Page 175 and 176:

Chapter 9: DMA Controller ° Signal

- Page 177 and 178:

9.1.3 Block Diagram X-Ref Target -

- Page 179 and 180:

Reset Initialization Interface Chap

- Page 181 and 182:

X-Ref Target - Figure 9-4 CPU_3x2x

- Page 183 and 184:

9.2.3 Memory to/from PL Peripheral

- Page 185 and 186:

Chapter 9: DMA Controller specifies

- Page 187 and 188:

Chapter 9: DMA Controller The DMALD

- Page 189 and 190:

Table 9‐2: Event/Interrupt Resour

- Page 191 and 192:

Table 9‐4: Abort Handling Thread

- Page 193 and 194:

Table 9‐8: Security Usage Summary

- Page 195 and 196:

9.3.3 Reset Initialization Interfac

- Page 197 and 198:

Chapter 9: DMA Controller 9.5 Instr

- Page 199 and 200:

9.6.2 Memory to Memory Chapter 9: D

- Page 201 and 202:

Table 9‐15: Unaligned Transfers (

- Page 203 and 204:

# Only loopback if servicing a burs

- Page 205 and 206:

Chapter 9: DMA Controller For examp

- Page 207 and 208:

When a discontinuity in the source

- Page 209 and 210:

DDR Memory Controller 10.1 Introduc

- Page 211 and 212:

X-Ref Target - Figure 10-1 Chapter

- Page 213 and 214:

Table 10‐1: Connectivity Limitati

- Page 215 and 216:

• Deep read and write command acc

- Page 217 and 218:

X-Ref Target - Figure 10-4 DDR Inte

- Page 219 and 220:

X-Ref Target - Figure 10-5 10.4.1 P

- Page 221 and 222:

X-Ref Target - Figure 10-6 Aging Co

- Page 223 and 224:

X-Ref Target - Figure 10-8 DDR Inte

- Page 225 and 226:

Chapter 10: DDR Memory Controller I

- Page 227 and 228:

10.5.1 Loopback Chapter 10: DDR Mem

- Page 229 and 230:

Table 10‐7: Calibration Field Nam

- Page 231 and 232:

10.6.4 DDR Controller Register Prog

- Page 233 and 234:

Chapter 10: DDR Memory Controller a

- Page 235 and 236:

Automatic Training The standard tra

- Page 237 and 238:

10.7 Register Overviews Chapter 10:

- Page 239 and 240:

Table 10‐11: DDRI Registers Overv

- Page 241 and 242:

Operating Modes Chapter 10: DDR Mem

- Page 243 and 244:

10.9.4 Self Refresh Chapter 10: DDR

- Page 245 and 246:

11.1.1 Features Chapter 11: Static

- Page 247 and 248:

11.1.3 Notices 7z010 CLG225 Device

- Page 249 and 250:

11.3 I/O Signals Chapter 11: Static

- Page 251 and 252:

X-Ref Target - Figure 11-5 SMC Cont

- Page 253 and 254:

Quad‐SPI Flash Controller 12.1 In

- Page 255 and 256:

Chapter 12: Quad‐SPI Flash Contro

- Page 257 and 258:

Chapter 12: Quad‐SPI Flash Contro

- Page 259 and 260:

Table 12‐2: Ignored AXI Read Addr

- Page 261 and 262:

12.3 Programming Guide Example: Sta

- Page 263 and 264:

Chapter 12: Quad‐SPI Flash Contro

- Page 265 and 266:

Chapter 12: Quad‐SPI Flash Contro

- Page 267 and 268:

Example: Read Data Sequence In this

- Page 269 and 270:

CPU_1x Clock Chapter 12: Quad‐SPI

- Page 271 and 272:

X-Ref Target - Figure 12-5 Dual SS,

- Page 273 and 274:

12.5.2 MIO Programming Chapter 12:

- Page 275 and 276:

a. Route Quad-SPI feedback clock ou

- Page 277 and 278:

X-Ref Target - Figure 13-1 AHB Inte

- Page 279 and 280:

• CRC generator and checker (CRC7

- Page 281 and 282:

Read Chapter 13: SD/SDIO Peripheral

- Page 283 and 284:

The sequence for data transfers wit

- Page 285 and 286:

Chapter 13: SD/SDIO Peripheral Cont

- Page 287 and 288:

13.3.4 Using ADMA X-Ref Target - Fi

- Page 289 and 290:

X-Ref Target - Figure 13-6 Synchron

- Page 291 and 292:

13.3.8 Bus Voltage Translation Chap

- Page 293 and 294:

Chapter 13: SD/SDIO Peripheral Cont

- Page 295 and 296:

14.2 Block Diagram X-Ref Target - F

- Page 297 and 298:

MIO bank control (for Bank0 and Ban

- Page 299 and 300:

Chapter 14: General Purpose I/O (GP

- Page 301 and 302:

Chapter 15: USB Host, Device, and O

- Page 303 and 304:

Chapter 15: USB Host, Device, and O

- Page 305 and 306:

15.3.1 Block Diagram Chapter 15: US

- Page 307 and 308:

15.5 Host Data Structure X-Ref Targ

- Page 309 and 310:

15.6.2 DMA Engine X-Ref Target - Fi

- Page 311 and 312:

15.6.5 Port Controller X-Ref Target

- Page 313 and 314:

Chapter 15: USB Host, Device, and O

- Page 315 and 316:

The change is a fundamental one in

- Page 317 and 318:

Asynchronous Transaction Scheduling

- Page 319 and 320:

Discovery Port Reset Chapter 15: US

- Page 321 and 322:

15.8.2 Port State and Control Chapt

- Page 323 and 324:

Chapter 15: USB Host, Device, and O

- Page 325 and 326:

Data Toggle Chapter 15: USB Host, D

- Page 327 and 328:

Table 15‐6: Variable Length Trans

- Page 329 and 330:

Control Endpoint Operation Model Se

- Page 331 and 332:

Table 15‐9: Control Endpoint Bus

- Page 333 and 334:

Chapter 15: USB Host, Device, and O

- Page 335 and 336:

Chapter 15: USB Host, Device, and O

- Page 337 and 338:

Active = 0 Halted = 0 Transaction E

- Page 339 and 340:

Low‐Frequency Interrupts Chapter

- Page 341 and 342:

Chapter 15: USB Host, Device, and O

- Page 343 and 344:

X-Ref Target - Figure 15-16 Operati

- Page 345 and 346:

Chapter 15: USB Host, Device, and O

- Page 347 and 348:

Table 15‐19: iTD Transaction Stat

- Page 349 and 350:

Table 15‐22: iTD Buffer Pointer P

- Page 351 and 352:

15.10.9 siTD Endpoint Capabilities/

- Page 353 and 354:

Chapter 15: USB Host, Device, and O

- Page 355 and 356:

15.10.12 siTD Back Link Pointer Cha

- Page 357 and 358:

15.10.15 Alternate Next qTD Pointer

- Page 359 and 360:

Chapter 15: USB Host, Device, and O

- Page 361 and 362:

7:0 (cont’d) 15.10.17 qTD Buffer

- Page 363 and 364:

15.10.19 Queue Head Horizontal Link

- Page 365 and 366:

Table 15‐36: Endpoint Capabilitie

- Page 367 and 368:

Table 15‐38: Host‐Controller Ru

- Page 369 and 370:

15.10.24 FSTN Back Path Link Pointe

- Page 371 and 372:

X-Ref Target - Figure 15-24 Endpoin

- Page 373 and 374:

Chapter 15: USB Host, Device, and O

- Page 375 and 376:

Chapter 15: USB Host, Device, and O

- Page 377 and 378:

Gigabit Ethernet Controller 16.1 In

- Page 379 and 380:

Chapter 16: Gigabit Ethernet Contro

- Page 381 and 382:

Chapter 16: Gigabit Ethernet Contro

- Page 383 and 384:

Chapter 16: Gigabit Ethernet Contro

- Page 385 and 386:

Chapter 16: Gigabit Ethernet Contro

- Page 387 and 388:

Chapter 16: Gigabit Ethernet Contro

- Page 389 and 390:

Table 16‐2: Rx Buffer Descriptor

- Page 391 and 392:

Chapter 16: Gigabit Ethernet Contro

- Page 393 and 394:

Table 16‐3: Tx Buffer Descriptor

- Page 395 and 396:

X-Ref Target - Figure 16-3 Gigabit

- Page 397 and 398:

Chapter 16: Gigabit Ethernet Contro

- Page 399 and 400:

Chapter 16: Gigabit Ethernet Contro

- Page 401 and 402:

Counter Value to the PL Chapter 16:

- Page 403 and 404:

Chapter 16: Gigabit Ethernet Contro

- Page 405 and 406:

Chapter 16: Gigabit Ethernet Contro

- Page 407 and 408:

X-Ref Target - Figure 16-4 To creat

- Page 409 and 410:

Chapter 16: Gigabit Ethernet Contro

- Page 411 and 412:

Table 16‐6: Ethernet Control Regi

- Page 413 and 414:

16.5 Signals and I/O Connections 16

- Page 415 and 416:

Table 16‐8: Ethernet RGMII Interf

- Page 417 and 418:

SPI Controller 17.1 Introduction Ch

- Page 419 and 420:

17.2 Functional Description 17.2.1

- Page 421 and 422:

17.2.4 Slave Mode Chapter 17: SPI C

- Page 423 and 424:

Table 17‐1: SPI MIO Pins and EMIO

- Page 425 and 426:

18.1.2 System Viewpoint The system

- Page 427 and 428:

18.2 Functional Description Chapter

- Page 429 and 430:

Normal Mode Chapter 18: CAN Control

- Page 431 and 432:

Table 18‐3: CAN Message Word Regi

- Page 433 and 434:

Chapter 18: CAN Controller When arb

- Page 435 and 436:

X-Ref Target - Figure 18-4 Table 18

- Page 437 and 438:

Chapter 18: CAN Controller If any o

- Page 439 and 440:

d. Zero-out extended frame bits, [A

- Page 441 and 442:

tBIT_RATE = tSYNC_SEGMENT + tTIME_S

- Page 443 and 444:

Chapter 18: CAN Controller 3. Wait

- Page 445 and 446:

5. Determine if more messages are i

- Page 447 and 448:

Chapter 18: CAN Controller 1. Confi

- Page 449 and 450:

18.5.2 MIO‐EMIO Signals Chapter 1

- Page 451 and 452:

° 1, 1.5, or 2 stop bits Chapter 1

- Page 453 and 454:

19.2 Functional Description 19.2.1

- Page 455 and 456:

19.2.3 Transmitter Data Stream Chap

- Page 457 and 458:

19.2.6 Mode Switch X-Ref Target - F

- Page 459 and 460:

4. Configure Baud Rate Generator (s

- Page 461 and 462:

Chapter 19: UART Controller 4. Repe

- Page 463 and 464:

Non‐FIFO Interrupts Chapter 19: U

- Page 465 and 466:

19.4 System Functions 19.4.1 Clocks

- Page 467 and 468:

Table 19‐4: UART MIO Pins and EMI

- Page 469 and 470:

° Supports TO interrupt flag to av

- Page 471 and 472:

Chapter 20: I2C Controller data is

- Page 473 and 474:

Chapter 20: I2C Controller At the s

- Page 475 and 476:

20.3 Register Overview An overview

- Page 477 and 478:

Chapter 21: Programmable Logic Desc

- Page 479 and 480:

Chapter 21: Programmable Logic Desc

- Page 481 and 482:

Error Detection and Correction Chap

- Page 483 and 484:

Chapter 21: Programmable Logic Desc

- Page 485 and 486:

Chapter 21: Programmable Logic Desc

- Page 487 and 488:

21.3 PS‐PL Interfaces Chapter 21:

- Page 489 and 490:

Power Chapter 22: Programmable Logi

- Page 491 and 492:

Chapter 22: Programmable Logic Desi

- Page 493 and 494:

Chapter 22: Programmable Logic Desi

- Page 495 and 496:

Chapter 22: Programmable Logic Desi

- Page 497 and 498:

X-Ref Target - Figure 22-1 MIO Pins

- Page 499 and 500:

X-Ref Target - Figure 22-3 MIO Pins

- Page 501 and 502:

Chapter 22: Programmable Logic Desi

- Page 503 and 504:

Chapter 22: Programmable Logic Desi

- Page 505 and 506:

23.1.2 Block Diagram A block diagra

- Page 507 and 508:

Chapter 23: Programmable Logic (PL)

- Page 509 and 510:

X-Ref Target - Figure 23-5 PL Activ

- Page 511 and 512:

Table 23‐5: Cycle Count Packet Fo

- Page 513 and 514:

23.4 Register Overview Table 23‐1

- Page 515 and 516:

24.2 Voltage Domains Figure 24-1 sh

- Page 517 and 518:

Clocks 25.1 Introduction Chapter 25

- Page 519 and 520:

25.1.4 System Viewpoint X-Ref Targe

- Page 521 and 522:

25.3 CPU Clock Domains X-Ref Target

- Page 523 and 524:

Table 25‐2: PS Peripheral Clock C

- Page 525 and 526:

X-Ref Target - Figure 25-4 These fe

- Page 527 and 528:

25.7 I/O Peripheral (IOP) Clocks I/

- Page 529 and 530:

Chapter 25: Clocks the RGMII interf

- Page 531 and 532:

X-Ref Target - Figure 25-10 IO PLL

- Page 533 and 534:

25.12 Programming Model 25.12.1 Bra

- Page 535 and 536:

Table 25‐5: PLL Frequency Control

- Page 537 and 538:

Chapter 25: Clocks Zynq‐7000 EPP

- Page 539 and 540:

X-Ref Target - Figure 26-1 PS_POR_B

- Page 541 and 542:

X-Ref Target - Figure 26-3 System R

- Page 543 and 544:

Chapter 26: Reset System The PS doe

- Page 545 and 546:

Chapter 26: Reset System The first

- Page 547 and 548:

X-Ref Target - Figure 27-1 Chapter

- Page 549 and 550:

27.2 Functional Description Chapter

- Page 551 and 552:

Chapter 27: JTAG and DAP Subsystem

- Page 553 and 554:

Chapter 27: JTAG and DAP Subsystem

- Page 555 and 556:

27.6 Trace Port Interface Unit (TPI

- Page 557 and 558:

System Test and Debug 28.1 Introduc

- Page 559 and 560:

• Trace source: PTM, FTM, ITM •

- Page 561 and 562:

Table 28‐1: CTI Trigger Inputs an

- Page 563 and 564:

28.2.6 Embedded Trace Buffer (ETB)

- Page 565 and 566:

28.4 Register Overview 28.4.1 Memor

- Page 567 and 568:

Table 28‐6: CoreSight Component R

- Page 569 and 570:

28.5 Programming Model 28.5.1 Authe

- Page 571 and 572:

On‐Chip Memory (OCM) 29.1 Introdu

- Page 573 and 574:

• TrustZone support for on-chip R

- Page 575 and 576:

X-Ref Target - Figure 29-3 Arbitrat

- Page 577 and 578:

OCM Relocation Chapter 29: On‐Chi

- Page 579 and 580:

29.2.5 Interrupts Chapter 29: On‐

- Page 581 and 582:

Chapter 29: On‐Chip Memory (OCM)

- Page 583 and 584:

30.1.1 Block Diagram Figure 30-1 sh

- Page 585 and 586:

Chapter 30: Analog‐to‐Digital C

- Page 587 and 588:

30.5 Programming Model Chapter 30:

- Page 589 and 590:

31.2 Block Diagram X-Ref Target - F

- Page 591 and 592:

Device Secure Boot 32.1 Introductio

- Page 593 and 594:

32.2 Functional Description 32.2.1

- Page 595 and 596:

X-Ref Target - Figure 32-3 BootROM

- Page 597 and 598:

32.2.8 Key Management Chapter 32: D

- Page 599 and 600:

Chapter 32: Device Secure Boot resu

- Page 601 and 602:

A.2 Solution Centers Appendix A: Ad

- Page 603 and 604:

ChipScope Pro Software and Cores Us

- Page 605 and 606:

Register Details B.1 Overview Appen

- Page 607 and 608:

B.3 Module Summary Module Name Modu

- Page 609 and 610:

Module Name Module Type Base Addres

- Page 611 and 612:

Register Name Address Width Type Re

- Page 613 and 614:

Register (AFI) AFI_RDCHAN_ISSUINGCA

- Page 615 and 616:

Absolute Address afi0: 0xF8008010 a

- Page 617 and 618:

Field Name Bits Type Reset Value De

- Page 619 and 620:

Register (AFI) AFI_WRDATAFIFO_LEVEL

- Page 621 and 622:

B.5 CAN Controller (can) Module Nam

- Page 623 and 624:

Register SRR Details Appendix B: Re

- Page 625 and 626:

Please refer to the CAN chapter for

- Page 627 and 628:

Field Name Bits Type Reset Value De

- Page 629 and 630:

Field Name Bits Type Reset Value De

- Page 631 and 632:

Field Name Bits Type Reset Value De

- Page 633 and 634:

Field Name Bits Type Reset Value De

- Page 635 and 636:

ETXFWMEMP (IXR_TXFWMEMP) ERXFWMFLL

- Page 637 and 638:

Field Name Bits Type Reset Value De

- Page 639 and 640:

CTXFWMEMP (IXR_TXFWMEMP) CRXFWMFLL

- Page 641 and 642:

Description Watermark Interrupt Reg

- Page 643 and 644:

Register (can) TXFIFO_DLC Name TXFI

- Page 645 and 646:

Field Name Bits Type Reset Value De

- Page 647 and 648:

Register TXHPB_DLC Details Field Na

- Page 649 and 650:

IDH (IDR_ID1) SRRRTR (IDR_SRR) IDE

- Page 651 and 652:

Register RXFIFO_DATA1 Details Field

- Page 653 and 654:

Field Name Bits Type Reset Value De

- Page 655 and 656:

Field Name Bits Type Reset Value De

- Page 657 and 658:

Register AFMR2 Details Field Name B

- Page 659 and 660:

Field Name Bits Type Reset Value De

- Page 661 and 662:

Field Name Bits Type Reset Value De

- Page 663 and 664:

Register AFMR4 Details Field Name B

- Page 665 and 666:

Field Name Bits Type Reset Value De

- Page 667 and 668:

Register Name Address Width Type Re

- Page 669 and 670:

Register Name Address Width Type Re

- Page 671 and 672:

Register Name Address Width Type Re

- Page 673 and 674:

Field Name Bits Type Reset Value De

- Page 675 and 676:

Register (ddrc) DRAM_param_reg0 Nam

- Page 677 and 678:

Reset Value 0x83015904 Description

- Page 679 and 680:

Field Name Bits Type Reset Value De

- Page 681 and 682:

Field Name Bits Type Reset Value De

- Page 683 and 684:

Description DRAM EMR, MR access Reg

- Page 685 and 686:

Field Name Bits Type Reset Value De

- Page 687 and 688:

Field Name Bits Type Reset Value De

- Page 689 and 690:

Field Name Bits Type Reset Value De

- Page 691 and 692:

Field Name Bits Type Reset Value De

- Page 693 and 694:

Register phy_cmd_timeout_rddata_cpt

- Page 695 and 696:

Register (ddrc) DLL_calib Name DLL_

- Page 697 and 698:

Field Name Bits Type Reset Value De

- Page 699 and 700:

Name ctrl_reg4 Register (ddrc) ctrl

- Page 701 and 702:

Name ctrl_reg6 Register (ddrc) ctrl

- Page 703 and 704:

Register (ddrc) CHE_T_ZQ_Short_Inte

- Page 705 and 706:

Field Name Bits Type Reset Value De

- Page 707 and 708:

Width 2 bits Access Type rw Reset V

- Page 709 and 710:

Field Name Bits Type Reset Value De

- Page 711 and 712:

Register CHE_UNCORR_ECC_LOG_REG_OFF

- Page 713 and 714:

Register CHE_UNCORR_ECC_DATA_71_64_

- Page 715 and 716:

Register CHE_ECC_CORR_BIT_MASK_31_0

- Page 717 and 718:

Name Address PHY_Config0 0xf8006118

- Page 719 and 720:

Name Address phy_rd_dqs_cfg0 0xf800

- Page 721 and 722:

Register phy_we_cfg0 to phy_we_cfg3

- Page 723 and 724:

Field Name Bits Type Reset Value De

- Page 725 and 726:

Field Name Bits Type Reset Value De

- Page 727 and 728:

Register reg6c_6d2 to reg6c_6d3 Det

- Page 729 and 730:

Register dll_lock_sts Details Field

- Page 731 and 732:

Name axi_id Register (ddrc) axi_id

- Page 733 and 734:

Register (ddrc) axi_priority_rd_por

- Page 735 and 736:

Register excl_access_cfg0 to excl_a

- Page 737 and 738:

Register lpddr_ctrl2 Details Field

- Page 739 and 740:

Register (ddrc) phy_gate_lvl_fsm Na

- Page 741 and 742:

Register Name Address Width Type Re

- Page 743 and 744:

Register (cti) CTIINTACK Name CTIIN

- Page 745 and 746:

Absolute Address debug_cpu_cti0: 0x

- Page 747 and 748:

Register (cti) CTIINEN2 Name CTIINE

- Page 749 and 750:

Register (cti) CTIINEN5 Name CTIINE

- Page 751 and 752:

Register (cti) CTIOUTEN0 Name CTIOU

- Page 753 and 754:

Register (cti) CTIOUTEN3 Name CTIOU

- Page 755 and 756:

Register (cti) CTIOUTEN6 Name CTIOU

- Page 757 and 758:

Absolute Address debug_cpu_cti0: 0x

- Page 759 and 760:

Field Name Bits Type Reset Value De

- Page 761 and 762:

Absolute Address debug_cpu_cti0: 0x

- Page 763 and 764:

Description ITTRIGIN Register Regis

- Page 765 and 766:

Width 32 bits Access Type wo Reset

- Page 767 and 768:

Register (cti) DEVID Name DEVID Rel

- Page 769 and 770:

Relative Address 0x00000FD8 Absolut

- Page 771 and 772:

Absolute Address debug_cpu_cti0: 0x

- Page 773 and 774:

Width 8 bits Access Type ro Reset V

- Page 775 and 776:

Register (cortexa9_pmu) PMXEVCNTR0

- Page 777 and 778:

Register (cortexa9_pmu) PMXEVCNTR5

- Page 779 and 780:

Register (cortexa9_pmu) PMXEVTYPER3

- Page 781 and 782:

Register (cortexa9_pmu) PMINTENSET

- Page 783 and 784:

Register (cortexa9_pmu) PMUSERENR N

- Page 785 and 786:

Register Name Address Width Type Re

- Page 787 and 788:

Register Name Address Width Type Re

- Page 789 and 790:

Field Name Bits Type Reset Value De

- Page 791 and 792:

Register (ptm) ETMTSSCR Name ETMTSS

- Page 793 and 794:

Register (ptm) ETMACVR2 Name ETMACV

- Page 795 and 796:

Register (ptm) ETMACVR7 Name ETMACV

- Page 797 and 798:

Register ETMACTR2 Details Field Nam

- Page 799 and 800:

Register ETMACTR4 Details Field Nam

- Page 801 and 802:

Register ETMACTR6 Details Field Nam

- Page 803 and 804:

Register ETMACTR8 Details Field Nam

- Page 805 and 806:

Width 18 bits Access Type mixed Res

- Page 807 and 808:

Register (ptm) ETMCNTVR2 Name ETMCN

- Page 809 and 810:

Register ETMSQ23EVR Details Field N

- Page 811 and 812:

Register ETMSQ13EVR Details Field N

- Page 813 and 814:

Access Type rw Reset Value 0x000000

- Page 815 and 816:

Access Type ro Reset Value 0x00C019

- Page 817 and 818:

Field Name Bits Type Reset Value De

- Page 819 and 820:

Register ITMISCOUT Details Field Na

- Page 821 and 822:

Register ITATBCTR2 Details Field Na

- Page 823 and 824:

Register CTSR Details Field Name Bi

- Page 825 and 826:

Register LSR Details Field Name Bit

- Page 827 and 828:

Register DTIR Details Field Name Bi

- Page 829 and 830:

Access Type ro Reset Value 0x000000

- Page 831 and 832:

Register (ptm) COMPID1 Name COMPID1

- Page 833 and 834:

B.10 Debug Access Port (dap) Module

- Page 835 and 836:

Width 32 bits Access Type ro Reset

- Page 837 and 838:

Reset Value 0x00005003 Description

- Page 839 and 840:

Reset Value 0x0000B003 Description

- Page 841 and 842:

Reset Value 0x00000000 Description

- Page 843 and 844:

Register ROMENTRY15 Details Field N

- Page 845 and 846:

Register PERIPHID0 Details Field Na

- Page 847 and 848:

Description Component ID1 Register

- Page 849 and 850:

Register Name Address Width Type Re

- Page 851 and 852:

Register RRD Details Field Name Bit

- Page 853 and 854:

Register CTL Details Field Name Bit

- Page 855 and 856:

Field Name Bits Type Reset Value De

- Page 857 and 858:

Reset Value 0x00000000 Description

- Page 859 and 860:

Name CTSR Register (etb) CTSR Relat

- Page 861 and 862:

Register LSR Details Field Name Bit

- Page 863 and 864:

Register PERIPHID4 Details Field Na

- Page 865 and 866:

Register PERIPHID1 Details Field Na

- Page 867 and 868:

Register COMPID2 Details Field Name

- Page 869 and 870:

Register Name Address Width Type Re

- Page 871 and 872:

Access Type rw Reset Value 0x000000

- Page 873 and 874:

Register FTMP2FDBG3 Details Field N

- Page 875 and 876:

Description AXI Cycle Count clock p

- Page 877 and 878:

Register FTMITTRIGOUTACK Details Fi

- Page 879 and 880:

Absolute Address 0xF880BEF0 Width 2

- Page 881 and 882:

Register CLAIMTAGSET Details Field

- Page 883 and 884:

Absolute Address 0xF880BFC8 Width 1

- Page 885 and 886:

Relative Address 0x00000FDC Absolut

- Page 887 and 888:

Register (ftm) FTMCOMPONID0 Name FT

- Page 889 and 890:

B.13 CoreSight Trace Funnel (funnel

- Page 891 and 892:

Field Name Bits Type Reset Value De

- Page 893 and 894:

Register ITATBCTR2 Details Field Na

- Page 895 and 896:

Register CTSR Details Field Name Bi

- Page 897 and 898:

Register LSR Details Field Name Bit

- Page 899 and 900:

Register PERIPHID4 Details Field Na

- Page 901 and 902:

Register PERIPHID1 Details Field Na

- Page 903 and 904:

Register COMPID2 Details Field Name

- Page 905 and 906:

Register Name Address Width Type Re

- Page 907 and 908:

Register StimPort00 Details Field N

- Page 909 and 910:

Register StimPort02 Details Field N

- Page 911 and 912:

Register StimPort04 Details Field N

- Page 913 and 914:

Register StimPort06 Details Field N

- Page 915 and 916:

Register StimPort08 Details Field N

- Page 917 and 918:

Register StimPort10 Details Field N

- Page 919 and 920:

Register StimPort12 Details Field N

- Page 921 and 922:

Register StimPort14 Details Field N

- Page 923 and 924:

Register StimPort16 Details Field N

- Page 925 and 926:

Register StimPort18 Details Field N

- Page 927 and 928:

Register StimPort20 Details Field N

- Page 929 and 930:

Register StimPort22 Details Field N

- Page 931 and 932:

Register StimPort24 Details Field N

- Page 933 and 934:

Register StimPort26 Details Field N

- Page 935 and 936:

Register StimPort28 Details Field N

- Page 937 and 938:

Register StimPort30 Details Field N

- Page 939 and 940:

Absolute Address 0xF8805E20 Width 3

- Page 941 and 942:

Description Integration Test Trigge

- Page 943 and 944:

Description Integration Mode Contro

- Page 945 and 946:

Relative Address 0x00000FB4 Absolut

- Page 947 and 948:

Relative Address 0x00000FD0 Absolut

- Page 949 and 950:

Absolute Address 0xF8805FE4 Width 8

- Page 951 and 952:

Relative Address 0x00000FF8 Absolut

- Page 953 and 954:

Register Name Address Width Type Re

- Page 955 and 956:

Reset Value 0x0000011F Description

- Page 957 and 958:

Register (tpiu) CurrentTest Name Cu

- Page 959 and 960:

Field Name Bits Type Reset Value De

- Page 961 and 962:

Register ITTRFLINACK Details Field

- Page 963 and 964:

Relative Address 0x00000EF8 Absolut

- Page 965 and 966:

Description Lock Access Register Re

- Page 967 and 968:

Access Type ro Reset Value 0x000000

- Page 969 and 970:

Relative Address 0x00000FDC Absolut

- Page 971 and 972:

Register (tpiu) COMPID0 Name COMPID

- Page 973 and 974:

B.16 Device Configuration Interface

- Page 975 and 976:

Register Name Address Width Type Re

- Page 977 and 978:

Register Name Address Width Type Re

- Page 979 and 980:

Field Name Bits Type Reset Value De

- Page 981 and 982:

Register LOCK Details Appendix B: R

- Page 983 and 984:

Field Name Bits Type Reset Value De

- Page 985 and 986:

Field Name Bits Type Reset Value De

- Page 987 and 988:

Field Name Bits Type Reset Value De

- Page 989 and 990:

Access Type rw Reset Value 0x000000

- Page 991 and 992:

Register (devcfg) ROM_SHADOW Name R

- Page 993 and 994:

Register MCTRL Details Field Name B

- Page 995 and 996:

Register XADCIF_INT_STS Details Fie

- Page 997 and 998:

Register XADCIF_CMDFIFO Details Fie

- Page 999 and 1000:

B.17 DMA Controller (dmac) Module N

- Page 1001 and 1002:

Register Name Address Width Type Re

- Page 1003 and 1004:

Register Name Address Width Type Re

- Page 1005 and 1006:

Register DSR Details Field Name Bit

- Page 1007 and 1008:

Width 32 bits Access Type mixed Res

- Page 1009 and 1010:

Absolute Address dmac0_ns: 0xF80040

- Page 1011 and 1012:

Field Name Bits Type Reset Value De

- Page 1013 and 1014:

Field Name Bits Type Reset Value De

- Page 1015 and 1016:

Register FTR1 Details Field Name Bi

- Page 1017 and 1018:

Field Name Bits Type Reset Value De

- Page 1019 and 1020:

Field Name Bits Type Reset Value De

- Page 1021 and 1022:

Register FTR3 Details Field Name Bi

- Page 1023 and 1024:

Field Name Bits Type Reset Value De

- Page 1025 and 1026:

Field Name Bits Type Reset Value De

- Page 1027 and 1028:

Register FTR5 Details Field Name Bi

- Page 1029 and 1030:

Field Name Bits Type Reset Value De

- Page 1031 and 1032:

Field Name Bits Type Reset Value De

- Page 1033 and 1034:

Register FTR7 Details Field Name Bi

- Page 1035 and 1036:

Field Name Bits Type Reset Value De

- Page 1037 and 1038:

Field Name Bits Type Reset Value De

- Page 1039 and 1040:

Field Name Bits Type Reset Value De

- Page 1041 and 1042:

Field Name Bits Type Reset Value De

- Page 1043 and 1044:

Field Name Bits Type Reset Value De

- Page 1045 and 1046:

Description Channel PC for DMA chan

- Page 1047 and 1048:

Relative Address 0x00000124 Absolut

- Page 1049 and 1050:

Field Name Bits Type Reset Value De

- Page 1051 and 1052:

Field Name Bits Type Reset Value De

- Page 1053 and 1054:

Field Name Bits Type Reset Value De

- Page 1055 and 1056:

Description Channel PC for DMA chan

- Page 1057 and 1058:

Field Name Bits Type Reset Value De

- Page 1059 and 1060:

Field Name Bits Type Reset Value De

- Page 1061 and 1062:

Register LC0_0 Details Field Name B

- Page 1063 and 1064:

Reset Value dmac0_ns: 0x00000000 dm

- Page 1065 and 1066:

Field Name Bits Type Reset Value De

- Page 1067 and 1068:

Field Name Bits Type Reset Value De

- Page 1069 and 1070:

Width 32 bits Access Type mixed Res

- Page 1071 and 1072:

Field Name Bits Type Reset Value De

- Page 1073 and 1074:

Field Name Bits Type Reset Value De

- Page 1075 and 1076:

Register LC0_2 Details Field Name B

- Page 1077 and 1078:

Reset Value dmac0_ns: 0x00000000 dm

- Page 1079 and 1080:

Field Name Bits Type Reset Value De

- Page 1081 and 1082:

Field Name Bits Type Reset Value De

- Page 1083 and 1084:

Width 32 bits Access Type mixed Res

- Page 1085 and 1086:

Field Name Bits Type Reset Value De

- Page 1087 and 1088:

Field Name Bits Type Reset Value De

- Page 1089 and 1090:

Register LC0_4 Details Field Name B

- Page 1091 and 1092:

Reset Value dmac0_ns: 0x00000000 dm

- Page 1093 and 1094:

Field Name Bits Type Reset Value De

- Page 1095 and 1096:

Field Name Bits Type Reset Value De

- Page 1097 and 1098:

Width 32 bits Access Type mixed Res

- Page 1099 and 1100:

Field Name Bits Type Reset Value De

- Page 1101 and 1102:

Field Name Bits Type Reset Value De

- Page 1103 and 1104:

Register LC0_6 Details Field Name B

- Page 1105 and 1106:

Reset Value dmac0_ns: 0x00000000 dm

- Page 1107 and 1108:

Field Name Bits Type Reset Value De

- Page 1109 and 1110:

Field Name Bits Type Reset Value De

- Page 1111 and 1112:

Access Type mixed Reset Value 0x000

- Page 1113 and 1114:

Access Type mixed Reset Value 0x000

- Page 1115 and 1116:

Field Name Bits Type Reset Value De

- Page 1117 and 1118:

Register CR3 Details Register (dmac

- Page 1119 and 1120:

Field Name Bits Type Reset Value De

- Page 1121 and 1122:

Reset Value dmac0_ns: 0x00000000 dm

- Page 1123 and 1124:

Register pcell_id_0 Details Field N

- Page 1125 and 1126:

B.18 Gigabit Ethernet Controller (G

- Page 1127 and 1128:

Register Name Address Width Type Re

- Page 1129 and 1130:

Relative Address 0x00000000 Absolut

- Page 1131 and 1132:

Name net_cfg Register (GEM) net_cfg

- Page 1133 and 1134:

len_err_frame_disc (LENGTHERRDSCRD)

- Page 1135 and 1136:

Field Name Bits Type Reset Value De

- Page 1137 and 1138:

Field Name Bits Type Reset Value De

- Page 1139 and 1140:

Name tx_status Register (GEM) tx_st

- Page 1141 and 1142:

Register rx_qbar Details Appendix B

- Page 1143 and 1144:

Register (GEM) intr_status Name int

- Page 1145 and 1146:

Field Name Bits Type Reset Value De

- Page 1147 and 1148:

Field Name Bits Type Reset Value De

- Page 1149 and 1150:

Field Name Bits Type Reset Value De

- Page 1151 and 1152:

Field Name Bits Type Reset Value De

- Page 1153 and 1154:

Appendix B: Register Details operat

- Page 1155 and 1156:

Name hash_top Register (GEM) hash_t

- Page 1157 and 1158:

Register (GEM) spec_addr2_top Name

- Page 1159 and 1160:

Register (GEM) spec_addr4_top Name

- Page 1161 and 1162:

Field Name Bits Type Reset Value De

- Page 1163 and 1164:

Register ipg_stretch Details Field

- Page 1165 and 1166:

Register (GEM) spec_addr1_mask_top

- Page 1167 and 1168:

Register octets_tx_top Details Appe

- Page 1169 and 1170:

Register multi_frames_tx Details Ap

- Page 1171 and 1172:

Register (GEM) frames_128to255b_tx

- Page 1173 and 1174:

Description Frame Tx, 1024 to 1518-

- Page 1175 and 1176:

Register multi_collisn_frames Detai

- Page 1177 and 1178:

Description Deferred Transmission F

- Page 1179 and 1180:

Register (GEM) octets_rx_top Name o

- Page 1181 and 1182:

Register (GEM) multi_frames_rx Name

- Page 1183 and 1184:

Reset Value 0x00000000 Description

- Page 1185 and 1186:

Field Name Bits Type Reset Value De

- Page 1187 and 1188:

Name jab_rx Register (GEM) jab_rx S

- Page 1189 and 1190:

Software Name XEMACPS_RXSYMBCNT Rel

- Page 1191 and 1192:

Absolute Address gem0: 0xE000B1A4 g

- Page 1193 and 1194:

Register udp_csum_errors Details Fi

- Page 1195 and 1196:

Register timer_ns Details Field Nam

- Page 1197 and 1198:

Name ptp_tx_ns Register (GEM) ptp_t

- Page 1199 and 1200:

Access Type ro Reset Value 0x000000

- Page 1201 and 1202:

Register ptp_peer_rx_ns Details Fie

- Page 1203 and 1204:

Access Type ro Reset Value 0x000000

- Page 1205 and 1206:

B.19 General Purpose I/O (gpio) Mod

- Page 1207 and 1208:

Register Name Address Width Type Re

- Page 1209 and 1210:

Field Name Bits Type Reset Value De

- Page 1211 and 1212:

Field Name Bits Type Reset Value De

- Page 1213 and 1214:

Field Name Bits Type Reset Value De

- Page 1215 and 1216:

Register (gpio) DATA_2_RO Name DATA

- Page 1217 and 1218:

Field Name Bits Type Reset Value De

- Page 1219 and 1220:

Software Name INTSTS Relative Addre

- Page 1221 and 1222:

Description Interrupt Any Edge Sens

- Page 1223 and 1224:

Field Name Bits Type Reset Value De

- Page 1225 and 1226:

Absolute Address 0xE000A264 Width 2

- Page 1227 and 1228:

Field Name Bits Type Reset Value De

- Page 1229 and 1230:

Absolute Address 0xE000A2A4 Width 3

- Page 1231 and 1232:

Field Name Bits Type Reset Value De

- Page 1233 and 1234:

Absolute Address 0xE000A2E4 Width 3

- Page 1235 and 1236:

Absolute Address gpv_qos301_cpu: 0x

- Page 1237 and 1238:

Name aw_p Register (qos301) aw_p Re

- Page 1239 and 1240:

Relative Address 0x00000128 Absolut

- Page 1241 and 1242:

Register (nic301_addr_region_ctrl_r

- Page 1243 and 1244:

Access Type mixed Reset Value 0x000

- Page 1245 and 1246:

Relative Address 0x00000008 Absolut

- Page 1247 and 1248:

Field Name Bits Type Reset Value De

- Page 1249 and 1250:

Width 16 bits Access Type ro Reset

- Page 1251 and 1252:

TO (IXR_TO) Field Name Bits Type Re

- Page 1253 and 1254:

B.23 L2 Cache (L2Cpl310) Module Nam

- Page 1255 and 1256:

Register Name Address Width Type Re

- Page 1257 and 1258:

Register Name Address Width Type Re

- Page 1259 and 1260:

Register Name Address Width Type Re

- Page 1261 and 1262:

Field Name Bits Type Reset Value De

- Page 1263 and 1264:

Field Name Bits Type Reset Value De

- Page 1265 and 1266:

Register reg1_tag_ram_control Detai

- Page 1267 and 1268:

Field Name Bits Type Reset Value De

- Page 1269 and 1270:

Width 32 bits Access Type mixed Res

- Page 1271 and 1272:

Register reg2_int_mask Details Regi

- Page 1273 and 1274:

Register reg2_int_raw_status Detail

- Page 1275 and 1276:

Field Name Bits Type Reset Value De

- Page 1277 and 1278:

Access Type mixed Reset Value 0x000

- Page 1279 and 1280:

Register (L2Cpl310) reg9_d_lockdown

- Page 1281 and 1282:

Register (L2Cpl310) reg9_d_lockdown

- Page 1283 and 1284:

Register reg9_d_lockdown4 Details F

- Page 1285 and 1286:

Access Type mixed Reset Value 0x000

- Page 1287 and 1288:

Register reg9_unlock_way Details Fi

- Page 1289 and 1290:

Field Name Bits Type Reset Value De

- Page 1291 and 1292:

Register (L2Cpl310) reg15_power_ctr

- Page 1293 and 1294:

Register Name Address Width Type Re

- Page 1295 and 1296:

Register Name Address Width Type Re

- Page 1297 and 1298:

Register Name Address Width Type Re

- Page 1299 and 1300:

Relative Address 0x00000004 Absolut

- Page 1301 and 1302:

Description SCU Invalidate All Regi

- Page 1303 and 1304:

Field Name Bits Type Reset Value De

- Page 1305 and 1306:

Register ICCICR Details Field Name

- Page 1307 and 1308:

Register ICCIAR Details Field Name

- Page 1309 and 1310:

Absolute Address 0xF8F0011C Width 3

- Page 1311 and 1312:

Register (mpcore) Global_Timer_Cont

- Page 1313 and 1314:

Absolute Address 0xF8F00210 Width 3

- Page 1315 and 1316:

Register (mpcore) Private_Timer_Cou

- Page 1317 and 1318:

Reset Value 0x00000000 Description

- Page 1319 and 1320:

Register Watchdog_Counter_Register

- Page 1321 and 1322:

Register (mpcore) Watchdog_Interrup

- Page 1323 and 1324:

Register Watchdog_Disable_Register

- Page 1325 and 1326:

Register ICDICTR Details Field Name

- Page 1327 and 1328:

Register ICDISR0 to ICDISR2 Details

- Page 1329 and 1330:

Reset Value 0x0000FFFF Description

- Page 1331 and 1332:

Register ICDISPR0 to ICDISPR2 Detai

- Page 1333 and 1334:

Appendix B: Register Details Note:

- Page 1335 and 1336:

Name Address ICDIPTR22 0xf8f01858 I

- Page 1337 and 1338:

Description Interrupt Configuration

- Page 1339 and 1340:

Register ppi_status Details Field N

- Page 1341 and 1342:

Register ICDSGIR Details Field Name

- Page 1343 and 1344:

Relative Address 0x00001FDC Absolut

- Page 1345 and 1346:

Register ICPIDR3 Details Field Name

- Page 1347 and 1348:

B.25 On‐Chip Memory (ocm) Module

- Page 1349 and 1350:

Access Type rw Reset Value 0x000000

- Page 1351 and 1352:

B.26 Quad‐SPI Flash Controller (q

- Page 1353 and 1354:

leg_flsh (IFMODE) Register Config_r

- Page 1355 and 1356:

Register Intr_status_REG Details Fi

- Page 1357 and 1358:

Register Intrpt_dis_REG Details Fie

- Page 1359 and 1360:

Register En_REG Details Field Name

- Page 1361 and 1362:

Width 32 bits Access Type mixed Res

- Page 1363 and 1364:

Register LPBK_DLY_ADJ Details Appen

- Page 1365 and 1366:

Absolute Address 0xE000D0A0 Width 3

- Page 1367 and 1368:

Field Name Bits Type Reset Value De

- Page 1369 and 1370:

B.27 SD Controller (sdio) Module Na

- Page 1371 and 1372:

Register Name Address Width Type Re

- Page 1373 and 1374:

Register Block_Size_Block_Count Det

- Page 1375 and 1376:

Register (sdio) Transfer_Mode_Comma

- Page 1377 and 1378:

Field Name Bits Type Reset Value De

- Page 1379 and 1380:

Register Present_State Details Fiel

- Page 1381 and 1382:

Field Name Bits Type Reset Value De

- Page 1383 and 1384:

Description Host control register P

- Page 1385 and 1386:

Field Name Bits Type Reset Value De

- Page 1387 and 1388:

Absolute Address sd0: 0xE010002C sd

- Page 1389 and 1390:

Field Name Bits Type Reset Value De

- Page 1391 and 1392:

Field Name Bits Type Reset Value De

- Page 1393 and 1394:

Field Name Bits Type Reset Value De

- Page 1395 and 1396:

Field Name Bits Type Reset Value De

- Page 1397 and 1398:

Field Name Bits Type Reset Value De

- Page 1399 and 1400:

Field Name Bits Type Reset Value De

- Page 1401 and 1402:

Register Capabilities Details Field

- Page 1403 and 1404:

Field Name Bits Type Reset Value De

- Page 1405 and 1406:

Field Name Bits Type Reset Value De

- Page 1407 and 1408:

Register ADMA_system_address Detail

- Page 1409 and 1410:

Register SPI_interrupt_support Deta

- Page 1411 and 1412:

B.28 System Level Control Registers

- Page 1413 and 1414:

Register Name Address Width Type Re

- Page 1415 and 1416:

Register Name Address Width Type Re

- Page 1417 and 1418:

Register SLCR_LOCK Details Field Na

- Page 1419 and 1420:

Field Name Bits Type Reset Value De

- Page 1421 and 1422:

Field Name Bits Type Reset Value De

- Page 1423 and 1424:

Register (slcr) DDR_PLL_CFG Name DD

- Page 1425 and 1426:

Field Name Bits Type Reset Value De

- Page 1427 and 1428:

Field Name Bits Type Reset Value De

- Page 1429 and 1430:

Description USB 1 ULPI Clock Contro

- Page 1431 and 1432:

Field Name Bits Type Reset Value De

- Page 1433 and 1434:

Field Name Bits Type Reset Value De

- Page 1435 and 1436:

Register SPI_CLK_CTRL Details Field

- Page 1437 and 1438:

Field Name Bits Type Reset Value De

- Page 1439 and 1440:

Register TOPSW_CLK_CTRL Details Fie

- Page 1441 and 1442:

Register FPGA2_CLK_CTRL Details Fie

- Page 1443 and 1444:

Register PSS_RST_CTRL Details Field

- Page 1445 and 1446:

Register USB_RST_CTRL Details Field

- Page 1447 and 1448:

Register SDIO_RST_CTRL Details Fiel

- Page 1449 and 1450:

Register CAN_RST_CTRL Details Field

- Page 1451 and 1452:

Field Name Bits Type Reset Value De

- Page 1453 and 1454:

Field Name Bits Type Reset Value De

- Page 1455 and 1456:

Field Name Bits Type Reset Value De

- Page 1457 and 1458:

Width 32 bits Access Type rw Reset

- Page 1459 and 1460:

Field Name Bits Type Reset Value De

- Page 1461 and 1462:

Relative Address 0x00000304 Absolut

- Page 1463 and 1464:

Register DDR_CAL_START Details Fiel

- Page 1465 and 1466:

Register (slcr) DDR_URGENT_SEL Name

- Page 1467 and 1468:

Field Name Bits Type Reset Value De

- Page 1469 and 1470:

Field Name Bits Type Reset Value De

- Page 1471 and 1472:

Field Name Bits Type Reset Value De

- Page 1473 and 1474:

Field Name Bits Type Reset Value De

- Page 1475 and 1476:

Field Name Bits Type Reset Value De

- Page 1477 and 1478:

Field Name Bits Type Reset Value De

- Page 1479 and 1480:

Field Name Bits Type Reset Value De

- Page 1481 and 1482:

Field Name Bits Type Reset Value De

- Page 1483 and 1484:

Register MIO_PIN_14 Details Field N

- Page 1485 and 1486:

Register MIO_PIN_16 Details Field N

- Page 1487 and 1488:

Register MIO_PIN_18 Details Field N

- Page 1489 and 1490:

Register MIO_PIN_20 Details Field N

- Page 1491 and 1492:

Register MIO_PIN_22 Details Field N

- Page 1493 and 1494:

Register MIO_PIN_24 Details Field N

- Page 1495 and 1496:

Register MIO_PIN_26 Details Field N

- Page 1497 and 1498:

Register MIO_PIN_28 Details Field N

- Page 1499 and 1500:

Register MIO_PIN_30 Details Field N

- Page 1501 and 1502:

Register MIO_PIN_32 Details Field N

- Page 1503 and 1504:

Register MIO_PIN_34 Details Field N

- Page 1505 and 1506:

Register MIO_PIN_36 Details Field N

- Page 1507 and 1508:

Reset Value 0x00001601 Description

- Page 1509 and 1510:

Width 32 bits Access Type rw Reset

- Page 1511 and 1512:

Relative Address 0x000007A8 Absolut

- Page 1513 and 1514:

Register (slcr) MIO_PIN_44 Name MIO

- Page 1515 and 1516:

Register (slcr) MIO_PIN_46 Name MIO

- Page 1517 and 1518:

Register (slcr) MIO_PIN_48 Name MIO

- Page 1519 and 1520:

Register (slcr) MIO_PIN_50 Name MIO

- Page 1521 and 1522:

Register (slcr) MIO_PIN_52 Name MIO

- Page 1523 and 1524:

Register (slcr) MIO_FMIO_GEM_SEL Na

- Page 1525 and 1526:

Field Name Bits Type Reset Value De

- Page 1527 and 1528:

Register (slcr) SD0_WP_CD_SEL Name

- Page 1529 and 1530:

Absolute Address 0xF8000910 Width 3

- Page 1531 and 1532:

Register (slcr) GPIOB_CFG_CMOS25 Na

- Page 1533 and 1534:

Width 32 bits Access Type rw Reset

- Page 1535 and 1536:

Field Name Bits Type Reset Value De

- Page 1537 and 1538:

Field Name Bits Type Reset Value De

- Page 1539 and 1540:

Width 32 bits Access Type rw Reset

- Page 1541 and 1542:

Field Name Bits Type Reset Value De

- Page 1543 and 1544:

Register (slcr) DDRIOB_DRIVE_SLEW_D

- Page 1545 and 1546:

Register DDRIOB_DDR_CTRL Details Fi

- Page 1547 and 1548:

Register DDRIOB_DCI_STATUS Details

- Page 1549 and 1550:

Register Name Address Width Type Re

- Page 1551 and 1552:

int_en0 (INT_EN0) state (STATE) Fie

- Page 1553 and 1554:

Register (pl353) memc_cfg_clr Name

- Page 1555 and 1556:

Set_t6 (SET_T6) Set_t5 (SET_T5) Set

- Page 1557 and 1558:

Field Name Bits Type Reset Value De

- Page 1559 and 1560:

Field Name Bits Type Reset Value De

- Page 1561 and 1562:

eserved 2 ro 0x0 Reserved. Do not m

- Page 1563 and 1564:

Reset Value 0x0024ABCC Description

- Page 1565 and 1566:

Register user_config Details Regist

- Page 1567 and 1568:

Field Name Bits Type Reset Value De

- Page 1569 and 1570:

Field Name Bits Type Reset Value De

- Page 1571 and 1572:

Register (pl353) ecc_addr0_1 Name e

- Page 1573 and 1574:

Register ecc_value1_1 Details Field

- Page 1575 and 1576:

Register ecc_value3_1 Details Field

- Page 1577 and 1578:

Absolute Address spi0: 0xE0006000 s

- Page 1579 and 1580:

Register Intr_status_reg0 Details F

- Page 1581 and 1582:

Width 32 bits Access Type mixed Res

- Page 1583 and 1584:

Register (SPI) En_reg0 Name En_reg0

- Page 1585 and 1586:

Relative Address 0x00000020 Absolut

- Page 1587 and 1588:

Access Type ro Reset Value 0x000901

- Page 1589 and 1590:

Field Name Bits Type Reset Value De

- Page 1591 and 1592:

Access Type ro Reset Value 0x000000

- Page 1593 and 1594:

Register Name Address Width Type Re

- Page 1595 and 1596:

Register (ttc) Clock_Control_3 Name

- Page 1597 and 1598:

Register Counter_Control_2 Details

- Page 1599 and 1600:

Value (MASK) Register Counter_Value

- Page 1601 and 1602:

Absolute Address ttc0: 0xF800102C t

- Page 1603 and 1604:

Description Match value Match (MATC

- Page 1605 and 1606:

Match (MATCH) Register Match_3_Coun

- Page 1607 and 1608:

Register (ttc) Interrupt_Register_3

- Page 1609 and 1610:

Register Interrupt_Enable_3 Details

- Page 1611 and 1612:

Absolute Address ttc0: 0xF8001078 t

- Page 1613 and 1614:

B.33 UART Controller (UART) Module

- Page 1615 and 1616:

TXRES (TXRST) RXRES (RXRST) Field N

- Page 1617 and 1618:

Field Name Bits Type Reset Value De

- Page 1619 and 1620:

Register Intrpt_mask_reg0 Details F

- Page 1621 and 1622:

Field Name Bits Type Reset Value De

- Page 1623 and 1624:

Access Type mixed Reset Value 0x000

- Page 1625 and 1626:

Field Name Bits Type Reset Value De

- Page 1627 and 1628:

Relative Address 0x00000030 Absolut

- Page 1629 and 1630:

B.34 USB Controller (usb) Module Na

- Page 1631 and 1632:

Register Name Address Width Type Re

- Page 1633 and 1634:

Register Name Address Width Type Re

- Page 1635 and 1636:

Field Name Bits Type Reset Value De

- Page 1637 and 1638:

Register (usb) HWTXBUF Name HWTXBUF

- Page 1639 and 1640:

Width 32 bits Access Type mixed Res

- Page 1641 and 1642:

Field Name Bits Type Reset Value De

- Page 1643 and 1644:

Register HCSPARAMS Details Field Na

- Page 1645 and 1646:

Field Name Bits Type Reset Value De

- Page 1647 and 1648:

Register USBCMD Details Field Name

- Page 1649 and 1650:

Field Name Bits Type Reset Value De

- Page 1651 and 1652:

HCH (IXR_HCH) Appendix B: Register

- Page 1653 and 1654:

Absolute Address usb0: 0xE0002148 u

- Page 1655 and 1656:

UEE (IXR_UE) UE (IXR_UI) Field Name

- Page 1657 and 1658:

Register PERIODICLISTBASE_DEVICEADD

- Page 1659 and 1660:

Register TTCTRL Details Field Name

- Page 1661 and 1662:

Register TXFILLTUNING Details Field

- Page 1663 and 1664:

Register IC_USB Details Field Name

- Page 1665 and 1666:

Field Name Bits Type Reset Value De

- Page 1667 and 1668:

Absolute Address usb0: 0xE0002178 u

- Page 1669 and 1670:

Register (usb) PORTSC1 Name PORTSC1

- Page 1671 and 1672:

Field Name Bits Type Reset Value De

- Page 1673 and 1674:

Field Name Bits Type Reset Value De

- Page 1675 and 1676:

Field Name Bits Type Reset Value De

- Page 1677 and 1678:

Field Name Bits Type Reset Value De

- Page 1679 and 1680:

Register USBMODE Details Field Name

- Page 1681 and 1682:

Register ENDPTSETUPSTAT Details Fie

- Page 1683 and 1684:

Register (usb) ENDPTFLUSH Name ENDP

- Page 1685 and 1686:

Register ENDPTSTAT Details Field Na

- Page 1687 and 1688:

Register (usb) ENDPTCTRL0 Name ENDP

- Page 1689 and 1690:

Register ENDPTCTRL1 to ENDPTCTRL12

- Page 1691:

Access Type Description w1crs w: 1/