impact of microvia-in-pad design on void formation - Sanmina-SCI

impact of microvia-in-pad design on void formation - Sanmina-SCI

impact of microvia-in-pad design on void formation - Sanmina-SCI

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

ABSTRACT<br />

IMPACT OF MICROVIA-IN-PAD DESIGN ON VOID FORMATION<br />

Frank Grano, Felix Bruno<br />

Huntsville, AL<br />

Dana Korf, Eam<strong>on</strong> O’Keeffe<br />

San Jose, CA<br />

Cheryl Kelley<br />

Salem, NH<br />

Jo<str<strong>on</strong>g>in</str<strong>on</strong>g>t Paper by Sanm<str<strong>on</strong>g>in</str<strong>on</strong>g>a-<strong>SCI</strong> Corporati<strong>on</strong> EMS, GTS and PCB Divisi<strong>on</strong>s<br />

Micro-vias are m<str<strong>on</strong>g>in</str<strong>on</strong>g>ute holes <str<strong>on</strong>g>in</str<strong>on</strong>g> circuit boards with a<br />

diameter <str<strong>on</strong>g>of</str<strong>on</strong>g> 6 mils or less that are placed with<str<strong>on</strong>g>in</str<strong>on</strong>g> or<br />

underneath comp<strong>on</strong>ent <str<strong>on</strong>g>pad</str<strong>on</strong>g>s. These structures allow the<br />

<str<strong>on</strong>g>in</str<strong>on</strong>g>terc<strong>on</strong>necti<strong>on</strong> <str<strong>on</strong>g>of</str<strong>on</strong>g> outer and <str<strong>on</strong>g>in</str<strong>on</strong>g>ner layers, which results <str<strong>on</strong>g>in</str<strong>on</strong>g><br />

an <str<strong>on</strong>g>in</str<strong>on</strong>g>creased rout<str<strong>on</strong>g>in</str<strong>on</strong>g>g area or available space for the<br />

placement <str<strong>on</strong>g>of</str<strong>on</strong>g> denser comp<strong>on</strong>ents. A via-<str<strong>on</strong>g>in</str<strong>on</strong>g>-<str<strong>on</strong>g>pad</str<strong>on</strong>g> is a platedthrough<br />

hole that is used as an <str<strong>on</strong>g>in</str<strong>on</strong>g>terlayer c<strong>on</strong>necti<strong>on</strong> from<br />

a comp<strong>on</strong>ent land, but <str<strong>on</strong>g>in</str<strong>on</strong>g> which there is no <str<strong>on</strong>g>in</str<strong>on</strong>g>tenti<strong>on</strong> to<br />

<str<strong>on</strong>g>in</str<strong>on</strong>g>sert a comp<strong>on</strong>ent lead or other re<str<strong>on</strong>g>in</str<strong>on</strong>g>forc<str<strong>on</strong>g>in</str<strong>on</strong>g>g material.<br />

However, the ability to either place vias <strong>on</strong> or <str<strong>on</strong>g>of</str<strong>on</strong>g>f the <str<strong>on</strong>g>pad</str<strong>on</strong>g>s<br />

gives <str<strong>on</strong>g>design</str<strong>on</strong>g>ers greater flexibility to selectively create<br />

rout<str<strong>on</strong>g>in</str<strong>on</strong>g>g room <str<strong>on</strong>g>in</str<strong>on</strong>g> denser parts <str<strong>on</strong>g>of</str<strong>on</strong>g> the substrate.<br />

This is phase 1 <str<strong>on</strong>g>of</str<strong>on</strong>g> an R&D project and this paper presents<br />

the solderability results for different via-<str<strong>on</strong>g>in</str<strong>on</strong>g>-<str<strong>on</strong>g>pad</str<strong>on</strong>g> locati<strong>on</strong>s<br />

and sizes based <strong>on</strong> assembly criteria. Although the <str<strong>on</strong>g>design</str<strong>on</strong>g><br />

<str<strong>on</strong>g>in</str<strong>on</strong>g>cludes Ball Grid Arrays (BGAs), Quad Flat Packs<br />

(QFPs) and passive comp<strong>on</strong>ents, <strong>on</strong>ly BGAs were<br />

exam<str<strong>on</strong>g>in</str<strong>on</strong>g>ed at this stage. S<str<strong>on</strong>g>in</str<strong>on</strong>g>ce the primary analysis will be<br />

<strong>void</strong> formati<strong>on</strong> the samples were analyzed us<str<strong>on</strong>g>in</str<strong>on</strong>g>g X-Ray<br />

Lam<str<strong>on</strong>g>in</str<strong>on</strong>g>ography and c<strong>on</strong>clusi<strong>on</strong>s drawn. The results <str<strong>on</strong>g>of</str<strong>on</strong>g> this<br />

experiment may not reflect the <str<strong>on</strong>g>impact</str<strong>on</strong>g> <strong>on</strong> high volume<br />

manufactur<str<strong>on</strong>g>in</str<strong>on</strong>g>g.<br />

BACKGROUND<br />

The tendency <str<strong>on</strong>g>in</str<strong>on</strong>g> electr<strong>on</strong>ic devices is toward smaller and<br />

lighter devices with an <str<strong>on</strong>g>in</str<strong>on</strong>g>crease <str<strong>on</strong>g>in</str<strong>on</strong>g> functi<strong>on</strong>ality. The size<br />

<str<strong>on</strong>g>of</str<strong>on</strong>g> products, such as cellular ph<strong>on</strong>es and camcorders, is a<br />

fracti<strong>on</strong> <str<strong>on</strong>g>of</str<strong>on</strong>g> the size they were before. The improved<br />

product functi<strong>on</strong>ality comes next to the dramatic<br />

reducti<strong>on</strong> <str<strong>on</strong>g>in</str<strong>on</strong>g> the size <str<strong>on</strong>g>of</str<strong>on</strong>g> the silic<strong>on</strong> packages and the<br />

Pr<str<strong>on</strong>g>in</str<strong>on</strong>g>ted Circuit Boards (PCBs) [1].<br />

Newer comp<strong>on</strong>ents such as Ball Grid Arrays (BGAs),<br />

Chip Scales Packages (CSPs) and Direct Chip Attach<br />

(DCA) devices have challenged the ability <str<strong>on</strong>g>of</str<strong>on</strong>g> technology<br />

associated with PCBs to manufacture cost effective<br />

boards. This is predom<str<strong>on</strong>g>in</str<strong>on</strong>g>antly due to the higher number<br />

<str<strong>on</strong>g>of</str<strong>on</strong>g> I/Os (as high as 2500 I/Os) and the tighter pitches (as<br />

low as 0.5 mm) associated with these comp<strong>on</strong>ents<br />

compared to peripheral leaded devices. The <str<strong>on</strong>g>in</str<strong>on</strong>g>creases <str<strong>on</strong>g>in</str<strong>on</strong>g><br />

the number <str<strong>on</strong>g>of</str<strong>on</strong>g> I/Os require PCBs to allow signal<br />

distributi<strong>on</strong> from these packages to the rest <str<strong>on</strong>g>of</str<strong>on</strong>g> the board.<br />

Different soluti<strong>on</strong>s have been proposed, such as<br />

fabricati<strong>on</strong> <str<strong>on</strong>g>of</str<strong>on</strong>g> f<str<strong>on</strong>g>in</str<strong>on</strong>g>e l<str<strong>on</strong>g>in</str<strong>on</strong>g>e circuitries and a reducti<strong>on</strong> <str<strong>on</strong>g>in</str<strong>on</strong>g> the<br />

spaces between the l<str<strong>on</strong>g>in</str<strong>on</strong>g>es. However, micro-via technology<br />

is <strong>on</strong>e soluti<strong>on</strong> to the challenges imposed by the<br />

m<str<strong>on</strong>g>in</str<strong>on</strong>g>iaturizati<strong>on</strong> <str<strong>on</strong>g>of</str<strong>on</strong>g> comp<strong>on</strong>ents utilized <str<strong>on</strong>g>in</str<strong>on</strong>g> current<br />

electr<strong>on</strong>ic assemblies. Micro-vias are the structures that<br />

allow the <str<strong>on</strong>g>in</str<strong>on</strong>g>terc<strong>on</strong>necti<strong>on</strong> between different layers <str<strong>on</strong>g>of</str<strong>on</strong>g> the<br />

circuit board and thereby enhance the rout<str<strong>on</strong>g>in</str<strong>on</strong>g>g area for the<br />

c<strong>on</strong>necti<strong>on</strong> <str<strong>on</strong>g>of</str<strong>on</strong>g> denser comp<strong>on</strong>ents [2].<br />

Micro-vias are def<str<strong>on</strong>g>in</str<strong>on</strong>g>ed by IPC-2315 and IPC-6012A<br />

standards, as bl<str<strong>on</strong>g>in</str<strong>on</strong>g>d and buried vias that are equal to or less<br />

than 6 mils (152 micr<strong>on</strong>s) <str<strong>on</strong>g>in</str<strong>on</strong>g> diameter and have a target<br />

<str<strong>on</strong>g>pad</str<strong>on</strong>g> equal to or less than 14 mils (356 micr<strong>on</strong>s). The<br />

target <str<strong>on</strong>g>pad</str<strong>on</strong>g> is def<str<strong>on</strong>g>in</str<strong>on</strong>g>ed as the land <strong>on</strong> which a micro-via<br />

ends and makes a c<strong>on</strong>necti<strong>on</strong> [3]. The micro-vias are<br />

placed <strong>on</strong> the substrate <str<strong>on</strong>g>pad</str<strong>on</strong>g>s, namely via-<str<strong>on</strong>g>in</str<strong>on</strong>g>-<str<strong>on</strong>g>pad</str<strong>on</strong>g>, and are<br />

used to <str<strong>on</strong>g>in</str<strong>on</strong>g>terc<strong>on</strong>nect the different outer and <str<strong>on</strong>g>in</str<strong>on</strong>g>ner layers <str<strong>on</strong>g>of</str<strong>on</strong>g><br />

a PCB. The use <str<strong>on</strong>g>of</str<strong>on</strong>g> micro-via technology, coupled with<br />

the reducti<strong>on</strong> <str<strong>on</strong>g>of</str<strong>on</strong>g> geometries <str<strong>on</strong>g>of</str<strong>on</strong>g> a c<strong>on</strong>venti<strong>on</strong>al<br />

multilayered PCB, is termed as a High Density<br />

Interc<strong>on</strong>necti<strong>on</strong> (HDI) structure [4]. Typically, these<br />

structures use a traditi<strong>on</strong>al FR-4 core with build-up<br />

dielectric layers such as Res<str<strong>on</strong>g>in</str<strong>on</strong>g> Coated Copper (RCC).<br />

Some <str<strong>on</strong>g>of</str<strong>on</strong>g> the reported advantages <str<strong>on</strong>g>of</str<strong>on</strong>g> the use <str<strong>on</strong>g>of</str<strong>on</strong>g> micro-vias<br />

are listed below [4]:<br />

They require smaller <str<strong>on</strong>g>pad</str<strong>on</strong>g> sizes, which save space <str<strong>on</strong>g>in</str<strong>on</strong>g><br />

the PCB;<br />

Increase the wir<str<strong>on</strong>g>in</str<strong>on</strong>g>g density <str<strong>on</strong>g>in</str<strong>on</strong>g> c<strong>on</strong>venti<strong>on</strong>al FR-4 by a<br />

factor <str<strong>on</strong>g>of</str<strong>on</strong>g> 4;<br />

Reduce layer counts (33% <str<strong>on</strong>g>of</str<strong>on</strong>g> c<strong>on</strong>venti<strong>on</strong>al boards);<br />

More chips can be placed <strong>on</strong> the PCB or a smaller<br />

PCB can be fabricated;<br />

•<br />

In some cases, micro-vias improve the electrical<br />

performance due to the smaller via lengths and<br />

diameters and shorter pathways <str<strong>on</strong>g>in</str<strong>on</strong>g> comparis<strong>on</strong> to the<br />

through hole; they reduce the cross talk and<br />

switch<str<strong>on</strong>g>in</str<strong>on</strong>g>g noises;

•<br />

•<br />

•<br />

Support surface mount comp<strong>on</strong>ents and DCA<br />

devices;<br />

Provide for better reliability <str<strong>on</strong>g>in</str<strong>on</strong>g> comparis<strong>on</strong> to through<br />

hole vias due to lowest aspect ratio. A typical aspect<br />

ratio for through holes is 4 - 8 and for micro-vias is<br />

between 0.5 – 0.7; and<br />

Can be fabricated <str<strong>on</strong>g>in</str<strong>on</strong>g> rigid, flex or rigid/flex<br />

substrates.<br />

EXPERIMENT<br />

The ma<str<strong>on</strong>g>in</str<strong>on</strong>g> focus <str<strong>on</strong>g>of</str<strong>on</strong>g> this project is to determ<str<strong>on</strong>g>in</str<strong>on</strong>g>e the<br />

optimum <str<strong>on</strong>g>design</str<strong>on</strong>g> criteria when <str<strong>on</strong>g>in</str<strong>on</strong>g>corporat<str<strong>on</strong>g>in</str<strong>on</strong>g>g via-<str<strong>on</strong>g>in</str<strong>on</strong>g>-<str<strong>on</strong>g>pad</str<strong>on</strong>g><br />

technology <str<strong>on</strong>g>in</str<strong>on</strong>g> a board <str<strong>on</strong>g>design</str<strong>on</strong>g>. The goal was to accomplish<br />

this by vary<str<strong>on</strong>g>in</str<strong>on</strong>g>g both the via-hole size and the locati<strong>on</strong> <str<strong>on</strong>g>of</str<strong>on</strong>g><br />

the via-hole <str<strong>on</strong>g>in</str<strong>on</strong>g> the <str<strong>on</strong>g>pad</str<strong>on</strong>g> al<strong>on</strong>g with assembl<str<strong>on</strong>g>in</str<strong>on</strong>g>g these <strong>on</strong> a<br />

standard Surface Mount Technology (SMT) l<str<strong>on</strong>g>in</str<strong>on</strong>g>e. The data<br />

generated from this would then be given to the Sanm<str<strong>on</strong>g>in</str<strong>on</strong>g>a-<br />

<strong>SCI</strong> PCB <str<strong>on</strong>g>design</str<strong>on</strong>g> group.<br />

With this <str<strong>on</strong>g>in</str<strong>on</strong>g> m<str<strong>on</strong>g>in</str<strong>on</strong>g>d a test-vehicle PCB was <str<strong>on</strong>g>design</str<strong>on</strong>g>ed for<br />

this evaluati<strong>on</strong> that was 8 layers with dimensi<strong>on</strong>s <str<strong>on</strong>g>of</str<strong>on</strong>g> 6.5”<br />

X 10”. The use <str<strong>on</strong>g>of</str<strong>on</strong>g> 8 layers allowed the <str<strong>on</strong>g>design</str<strong>on</strong>g>ers to best<br />

simulate the via-hole c<strong>on</strong>figurati<strong>on</strong>s currently be<str<strong>on</strong>g>in</str<strong>on</strong>g>g used.<br />

Dummy <str<strong>on</strong>g>in</str<strong>on</strong>g>ner layer planes were used for thermal load<str<strong>on</strong>g>in</str<strong>on</strong>g>g<br />

characteristics. PCBs <str<strong>on</strong>g>of</str<strong>on</strong>g> two different thicknesses (0.062”<br />

and 0.093”) were used and two surface f<str<strong>on</strong>g>in</str<strong>on</strong>g>ishes -<br />

Immersi<strong>on</strong> Ag and Ni-Au - are used <str<strong>on</strong>g>in</str<strong>on</strong>g> this <str<strong>on</strong>g>in</str<strong>on</strong>g>vestigati<strong>on</strong>.<br />

The PCB was split <str<strong>on</strong>g>in</str<strong>on</strong>g>to 4 secti<strong>on</strong>s, with each secti<strong>on</strong><br />

c<strong>on</strong>sist<str<strong>on</strong>g>in</str<strong>on</strong>g>g <str<strong>on</strong>g>of</str<strong>on</strong>g> a different via <str<strong>on</strong>g>design</str<strong>on</strong>g>.<br />

Figure 1: Via-In-Pad PCB<br />

• 56 ball, 0.5 mm pitch BGA<br />

• 208 lead, QFP 0.5 mm pitch QFP<br />

• 0805s, 0603s, and 0402s capacitors<br />

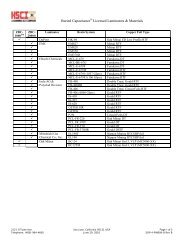

The different via <str<strong>on</strong>g>design</str<strong>on</strong>g>s for the BGAs are shown <str<strong>on</strong>g>in</str<strong>on</strong>g><br />

Figure 2 below. BGA 1 was used twice <str<strong>on</strong>g>in</str<strong>on</strong>g> the <str<strong>on</strong>g>design</str<strong>on</strong>g> –<br />

<strong>on</strong>ce for a micro-via and then aga<str<strong>on</strong>g>in</str<strong>on</strong>g> for a through hole<br />

c<strong>on</strong>figurati<strong>on</strong>. See Table 1 for a complete list <str<strong>on</strong>g>of</str<strong>on</strong>g> the<br />

<str<strong>on</strong>g>design</str<strong>on</strong>g>s used. The images below show the BGA <str<strong>on</strong>g>pad</str<strong>on</strong>g> styles<br />

used and via-holes.<br />

BGA 1<br />

BGA 2<br />

BGA3<br />

BGA Pad<br />

Via<br />

BGA Pad<br />

Via<br />

BGA Pad<br />

Via<br />

Figure 2: BGA Design Patterns Used<br />

The via-hole <str<strong>on</strong>g>design</str<strong>on</strong>g> for the QFP is shown <str<strong>on</strong>g>in</str<strong>on</strong>g> Figure 3. For<br />

the QFP <strong>on</strong>ly 1 via-hole locati<strong>on</strong> was used.<br />

Figure 3: QFP Design Patterns Used<br />

The via-hole <str<strong>on</strong>g>design</str<strong>on</strong>g> for the passive devices is shown <str<strong>on</strong>g>in</str<strong>on</strong>g><br />

Figure 4:<br />

For this evaluati<strong>on</strong>, the follow<str<strong>on</strong>g>in</str<strong>on</strong>g>g comp<strong>on</strong>ents were used:<br />

• 615 ball, 1.27 mm pitch BGA<br />

• 548 ball, 1.00 mm pitch BGA<br />

• 64 ball, 0.8 mm pitch BGA Figure 4: Passive Design Patterns Used

Via-Hole sizes be<str<strong>on</strong>g>in</str<strong>on</strong>g>g tested <str<strong>on</strong>g>in</str<strong>on</strong>g>clude 4, 6, and 8 mils and<br />

these go from layer 1 to layer 2 and from layer 1 to layer<br />

3 <str<strong>on</strong>g>of</str<strong>on</strong>g> the PCB. A through-hole c<strong>on</strong>figurati<strong>on</strong> is also<br />

<str<strong>on</strong>g>in</str<strong>on</strong>g>cluded for each device i.e. these vias went for layer 1 to<br />

layer 8 <str<strong>on</strong>g>of</str<strong>on</strong>g> the 8 layer PCB.<br />

Lyr 1<br />

to 2<br />

(mils)<br />

Lyr 1<br />

to 3<br />

(mils)<br />

Device<br />

Pitch <str<strong>on</strong>g>in</str<strong>on</strong>g><br />

mm<br />

BGA 548 1.0 4, 6 6, 8 8<br />

BGA 615 1.27 4, 6 6, 8 8<br />

BGA 64 0.8 4, 6 6, 8 8<br />

BGA 56 0.5 6 6 8<br />

QFP 208 0.5 4, 6 6, 8 8<br />

Passives n/a 4, 6 6, 8 8<br />

Table 1 – Overall Design Parameters<br />

PTH<br />

(mils)<br />

The boards were assembled <strong>on</strong> a standard producti<strong>on</strong><br />

SMT l<str<strong>on</strong>g>in</str<strong>on</strong>g>e and the primary goal <str<strong>on</strong>g>of</str<strong>on</strong>g> this build was to look at<br />

the <str<strong>on</strong>g>in</str<strong>on</strong>g>fluence that the via-hole locati<strong>on</strong> and size had <strong>on</strong><br />

solderability, if any. The ma<str<strong>on</strong>g>in</str<strong>on</strong>g> measurement criteria<br />

would be to look at solder jo<str<strong>on</strong>g>in</str<strong>on</strong>g>t <strong>void</strong><str<strong>on</strong>g>in</str<strong>on</strong>g>g issues that are<br />

typically associated with the use <str<strong>on</strong>g>of</str<strong>on</strong>g> this type <str<strong>on</strong>g>of</str<strong>on</strong>g> <str<strong>on</strong>g>design</str<strong>on</strong>g>.<br />

A standard no clean solder paste (63/37 SnPb) was chosen<br />

for the purposes <str<strong>on</strong>g>of</str<strong>on</strong>g> the <str<strong>on</strong>g>in</str<strong>on</strong>g>vestigati<strong>on</strong>. A stencil <str<strong>on</strong>g>design</str<strong>on</strong>g> that<br />

had been used successfully <str<strong>on</strong>g>in</str<strong>on</strong>g> the past was <str<strong>on</strong>g>in</str<strong>on</strong>g>corporated<br />

and used al<strong>on</strong>g with a reflow pr<str<strong>on</strong>g>of</str<strong>on</strong>g>ile that has been known<br />

to m<str<strong>on</strong>g>in</str<strong>on</strong>g>imize solder jo<str<strong>on</strong>g>in</str<strong>on</strong>g>t <strong>void</strong><str<strong>on</strong>g>in</str<strong>on</strong>g>g. This was d<strong>on</strong>e s<str<strong>on</strong>g>in</str<strong>on</strong>g>ce<br />

there would be no variati<strong>on</strong> <str<strong>on</strong>g>of</str<strong>on</strong>g> any <str<strong>on</strong>g>of</str<strong>on</strong>g> the assembly<br />

parameters dur<str<strong>on</strong>g>in</str<strong>on</strong>g>g the run. The goal was to look at<br />

optimiz<str<strong>on</strong>g>in</str<strong>on</strong>g>g the <str<strong>on</strong>g>design</str<strong>on</strong>g> criteria when us<str<strong>on</strong>g>in</str<strong>on</strong>g>g a via-<str<strong>on</strong>g>in</str<strong>on</strong>g>-<str<strong>on</strong>g>pad</str<strong>on</strong>g><br />

layout.<br />

Some <str<strong>on</strong>g>of</str<strong>on</strong>g> the producti<strong>on</strong> parameters:<br />

• One stencil <str<strong>on</strong>g>design</str<strong>on</strong>g> was used for all boards. The<br />

stencil was 5 mils thick and the apertures were<br />

<str<strong>on</strong>g>design</str<strong>on</strong>g>ed to be 1:1 with the SMT <str<strong>on</strong>g>pad</str<strong>on</strong>g>s.<br />

• Average paste height recorded was 5.8 mils,<br />

which is acceptable.<br />

• Oven set po<str<strong>on</strong>g>in</str<strong>on</strong>g>ts varied from the .062 board to the<br />

.093 board but a s<str<strong>on</strong>g>in</str<strong>on</strong>g>gle pr<str<strong>on</strong>g>of</str<strong>on</strong>g>ile, as measured by<br />

solder jo<str<strong>on</strong>g>in</str<strong>on</strong>g>t temperatures, was used.<br />

• Based <strong>on</strong> the chosen solder paste a straight l<str<strong>on</strong>g>in</str<strong>on</strong>g>e<br />

preheat / soak cycle and then a spike to 215<br />

degrees was used as our reflow pr<str<strong>on</strong>g>of</str<strong>on</strong>g>ile. (See<br />

Figure 5)<br />

• All reflow was d<strong>on</strong>e <str<strong>on</strong>g>in</str<strong>on</strong>g> an air envir<strong>on</strong>ment<br />

Figure 5: Reflow Pr<str<strong>on</strong>g>of</str<strong>on</strong>g>ile<br />

The assembled boards covered 2 surface f<str<strong>on</strong>g>in</str<strong>on</strong>g>ishes and 2<br />

board thickness. As stated earlier the evaluati<strong>on</strong> criteria<br />

will be the exam<str<strong>on</strong>g>in</str<strong>on</strong>g>ati<strong>on</strong> <str<strong>on</strong>g>of</str<strong>on</strong>g> solder jo<str<strong>on</strong>g>in</str<strong>on</strong>g>t <strong>void</strong><str<strong>on</strong>g>in</str<strong>on</strong>g>g, and as<br />

such X-Ray analysis will be used to observe the results.<br />

TESTING & RESULTS<br />

Our primary analysis tool was the use <str<strong>on</strong>g>of</str<strong>on</strong>g> X-Ray<br />

<str<strong>on</strong>g>in</str<strong>on</strong>g>specti<strong>on</strong>, both transmissi<strong>on</strong> and Lam<str<strong>on</strong>g>in</str<strong>on</strong>g>ography, to look<br />

at <strong>void</strong> size and locati<strong>on</strong> <str<strong>on</strong>g>in</str<strong>on</strong>g> the solder jo<str<strong>on</strong>g>in</str<strong>on</strong>g>t. Although the<br />

board c<strong>on</strong>ta<str<strong>on</strong>g>in</str<strong>on</strong>g>ed passives and QFP’s, the analysis<br />

c<strong>on</strong>centrated <strong>on</strong> the BGA’s used <strong>on</strong> the assembly. There<br />

is no specific IPC pass / fail criteria for BGA <strong>void</strong><str<strong>on</strong>g>in</str<strong>on</strong>g>g. The<br />

paragraph below is taken from IPC-610C and serves as a<br />

guidel<str<strong>on</strong>g>in</str<strong>on</strong>g>e or reference po<str<strong>on</strong>g>in</str<strong>on</strong>g>t:<br />

The follow<str<strong>on</strong>g>in</str<strong>on</strong>g>g guidel<str<strong>on</strong>g>in</str<strong>on</strong>g>es are provided as assessment<br />

criteria for the attachment technology process. Without<br />

substantial documented reliability data at the time <str<strong>on</strong>g>of</str<strong>on</strong>g><br />

publicati<strong>on</strong> <str<strong>on</strong>g>of</str<strong>on</strong>g> this revisi<strong>on</strong>, no acceptability criteria are<br />

provided.<br />

Acceptable - Class 1, 2, 3<br />

• Less than 10% <strong>void</strong><str<strong>on</strong>g>in</str<strong>on</strong>g>g <str<strong>on</strong>g>in</str<strong>on</strong>g> the ball to board <str<strong>on</strong>g>in</str<strong>on</strong>g>terface.<br />

Process Indicator - Class 2, 3<br />

• 10-25% <strong>void</strong><str<strong>on</strong>g>in</str<strong>on</strong>g>g <str<strong>on</strong>g>in</str<strong>on</strong>g> the ball to board <str<strong>on</strong>g>in</str<strong>on</strong>g>terface.<br />

Void<str<strong>on</strong>g>in</str<strong>on</strong>g>g <str<strong>on</strong>g>in</str<strong>on</strong>g> the BGA solder ball to board <str<strong>on</strong>g>in</str<strong>on</strong>g>terc<strong>on</strong>necti<strong>on</strong><br />

up to 25% may or may not be a reliability issue and<br />

should be determ<str<strong>on</strong>g>in</str<strong>on</strong>g>ed <str<strong>on</strong>g>in</str<strong>on</strong>g> your process development.<br />

BGA solder jo<str<strong>on</strong>g>in</str<strong>on</strong>g>t reliability studies performed at some<br />

<str<strong>on</strong>g>in</str<strong>on</strong>g>dustry locati<strong>on</strong>s show that limited <strong>void</strong><str<strong>on</strong>g>in</str<strong>on</strong>g>g <str<strong>on</strong>g>in</str<strong>on</strong>g> BGA balls<br />

does not <str<strong>on</strong>g>impact</str<strong>on</strong>g> l<strong>on</strong>g-term reliability.<br />

Defect - Class 1, 2, 3<br />

• More than 25% <strong>void</strong><str<strong>on</strong>g>in</str<strong>on</strong>g>g <str<strong>on</strong>g>in</str<strong>on</strong>g> the ball to board <str<strong>on</strong>g>in</str<strong>on</strong>g>terface.

With this specificati<strong>on</strong> open to some <str<strong>on</strong>g>in</str<strong>on</strong>g>terpretati<strong>on</strong> the<br />

po<str<strong>on</strong>g>in</str<strong>on</strong>g>t <str<strong>on</strong>g>of</str<strong>on</strong>g> this analysis will be to compare the various<br />

<str<strong>on</strong>g>design</str<strong>on</strong>g> c<strong>on</strong>figurati<strong>on</strong>s to each other and whether or not it<br />

is a reliability issue will not be looked at.<br />

Transmissi<strong>on</strong> X-Ray Images:<br />

Figure 6A shows a 0.5 mm BGA. All <str<strong>on</strong>g>pad</str<strong>on</strong>g>s were <str<strong>on</strong>g>design</str<strong>on</strong>g>ed<br />

with 6 mil vias <str<strong>on</strong>g>in</str<strong>on</strong>g> the center <str<strong>on</strong>g>of</str<strong>on</strong>g> the <str<strong>on</strong>g>pad</str<strong>on</strong>g>s. On the left side<br />

the vias go from layer 1 to layer 2 and <strong>on</strong> the right side<br />

the vias go from layer 1 to layer 3. Notice the <str<strong>on</strong>g>in</str<strong>on</strong>g>crease <str<strong>on</strong>g>in</str<strong>on</strong>g><br />

<strong>void</strong><str<strong>on</strong>g>in</str<strong>on</strong>g>g as the depth <str<strong>on</strong>g>of</str<strong>on</strong>g> the via hole <str<strong>on</strong>g>in</str<strong>on</strong>g>creases. Figure 6B<br />

shows the same package but the sample, <str<strong>on</strong>g>in</str<strong>on</strong>g> this case, has<br />

an 8 mil through hole via. (Layer 1 to the bottom <str<strong>on</strong>g>of</str<strong>on</strong>g> the<br />

PCB).<br />

Figure 6A: 0.5 mm BGA<br />

Figure 6B: 0.5 mm BGA<br />

Figure 7 shows a 0.8 mm BGA. All <str<strong>on</strong>g>pad</str<strong>on</strong>g>s were <str<strong>on</strong>g>design</str<strong>on</strong>g>ed<br />

with 8 mil plated through holes go<str<strong>on</strong>g>in</str<strong>on</strong>g>g from layer 1 to the<br />

bottom <str<strong>on</strong>g>of</str<strong>on</strong>g> the PCB (layer 8) <str<strong>on</strong>g>in</str<strong>on</strong>g> the center <str<strong>on</strong>g>of</str<strong>on</strong>g> the <str<strong>on</strong>g>pad</str<strong>on</strong>g>.<br />

Notice the large <strong>void</strong>s throughout the entire device very<br />

similar to the 0.5 mm pitch package.<br />

Figure 7: 0.8 mm BGA<br />

Figures 8A and 8B are images <str<strong>on</strong>g>of</str<strong>on</strong>g> a 1.0 mm BGA. Both<br />

use a 4 mil via–<str<strong>on</strong>g>in</str<strong>on</strong>g>-<str<strong>on</strong>g>pad</str<strong>on</strong>g> go<str<strong>on</strong>g>in</str<strong>on</strong>g>g from layer 1 to layer 2. The<br />

top image (Figure 8A) has the via-hole <str<strong>on</strong>g>in</str<strong>on</strong>g> the center <str<strong>on</strong>g>of</str<strong>on</strong>g> the<br />

<str<strong>on</strong>g>pad</str<strong>on</strong>g> while the sec<strong>on</strong>d image (Figure 8B) uses a via-hole<br />

<str<strong>on</strong>g>of</str<strong>on</strong>g>fset from the center <str<strong>on</strong>g>of</str<strong>on</strong>g> the <str<strong>on</strong>g>pad</str<strong>on</strong>g>. Void<str<strong>on</strong>g>in</str<strong>on</strong>g>g was reduced by<br />

us<str<strong>on</strong>g>in</str<strong>on</strong>g>g the <str<strong>on</strong>g>of</str<strong>on</strong>g>fset via-hole c<strong>on</strong>figurati<strong>on</strong>.<br />

Figure 8A: 1.0 mm BGA<br />

Figure 8B: 1.0 mm BGA<br />

Lam<str<strong>on</strong>g>in</str<strong>on</strong>g>ography X-Ray Test<str<strong>on</strong>g>in</str<strong>on</strong>g>g:<br />

Three locati<strong>on</strong>s were exam<str<strong>on</strong>g>in</str<strong>on</strong>g>ed <str<strong>on</strong>g>in</str<strong>on</strong>g> the BGA solder jo<str<strong>on</strong>g>in</str<strong>on</strong>g>ts<br />

us<str<strong>on</strong>g>in</str<strong>on</strong>g>g Lam<str<strong>on</strong>g>in</str<strong>on</strong>g>ography – See Figure 9:<br />

Slice # 1: Center <str<strong>on</strong>g>of</str<strong>on</strong>g> the ball<br />

Slice #2: Interface between ball and BGA substrate<br />

Slice #3: Interface between the ball and the PCB<br />

Figure 9: Lam<str<strong>on</strong>g>in</str<strong>on</strong>g>ography Slices<br />

(image courtesy <str<strong>on</strong>g>of</str<strong>on</strong>g> Agilent)

Each measurement tested for: the presence <str<strong>on</strong>g>of</str<strong>on</strong>g> <strong>void</strong>s, the<br />

number <str<strong>on</strong>g>of</str<strong>on</strong>g> <strong>void</strong>s, the size <str<strong>on</strong>g>of</str<strong>on</strong>g> the <strong>void</strong>s, and the locati<strong>on</strong> <str<strong>on</strong>g>of</str<strong>on</strong>g><br />

the <strong>void</strong>s. Figure 10 shows an example <str<strong>on</strong>g>of</str<strong>on</strong>g> BGA <strong>void</strong> cross<br />

secti<strong>on</strong>.<br />

The data generated from the Lam<str<strong>on</strong>g>in</str<strong>on</strong>g>ography test<str<strong>on</strong>g>in</str<strong>on</strong>g>g was<br />

fairly extensive and was parsed based <strong>on</strong> the follow<str<strong>on</strong>g>in</str<strong>on</strong>g>g<br />

criteria:<br />

• Board Surface F<str<strong>on</strong>g>in</str<strong>on</strong>g>ish<br />

• Board Thickness<br />

• Board Pad Design<br />

• Comp<strong>on</strong>ent Type<br />

• Via-Hole Size<br />

• Layer 1 to Layer 2 Via-Hole<br />

• Layer 1 to Layer 3 Via-Hole<br />

Figure 10: Example <str<strong>on</strong>g>of</str<strong>on</strong>g> BGA Void<br />

This was performed for each <str<strong>on</strong>g>of</str<strong>on</strong>g> the measurement slices<br />

look<str<strong>on</strong>g>in</str<strong>on</strong>g>g to determ<str<strong>on</strong>g>in</str<strong>on</strong>g>e the effect <str<strong>on</strong>g>of</str<strong>on</strong>g> each variable.<br />

Measurements were taken and recorded <strong>on</strong> the<br />

Lam<str<strong>on</strong>g>in</str<strong>on</strong>g>ography equipment and then calculati<strong>on</strong>s were<br />

performed for the mean <strong>void</strong> size, the standard deviati<strong>on</strong>,<br />

the range, the m<str<strong>on</strong>g>in</str<strong>on</strong>g>imum <strong>void</strong> size, the maximum <strong>void</strong><br />

size, and the number <str<strong>on</strong>g>of</str<strong>on</strong>g> <strong>void</strong>s.<br />

Def<str<strong>on</strong>g>in</str<strong>on</strong>g>iti<strong>on</strong>s for the charts with all units be<str<strong>on</strong>g>in</str<strong>on</strong>g>g <str<strong>on</strong>g>in</str<strong>on</strong>g> mils:<br />

• Mean – Standard mean calculati<strong>on</strong> for the viahole<br />

size<br />

• Std. Dev. – Standard Deviati<strong>on</strong> for the via-hole<br />

size<br />

• Range – Largest via-hole m<str<strong>on</strong>g>in</str<strong>on</strong>g>us the smallest<br />

• M<str<strong>on</strong>g>in</str<strong>on</strong>g>imum – Smallest <strong>void</strong> size<br />

• Maximum – Largest <strong>void</strong> size<br />

Test 1: Effect <str<strong>on</strong>g>of</str<strong>on</strong>g> Board Thickness<br />

In general the .093 boards produced less <strong>void</strong><str<strong>on</strong>g>in</str<strong>on</strong>g>g than the<br />

.062 boards. The mean and standard deviati<strong>on</strong> for the<br />

<strong>void</strong>s were close <str<strong>on</strong>g>in</str<strong>on</strong>g> each thickness but the total <strong>void</strong>s<br />

found numbered about 15% higher for the th<str<strong>on</strong>g>in</str<strong>on</strong>g>ner boards.<br />

All other data showed little variati<strong>on</strong>. Further work will<br />

be d<strong>on</strong>e <str<strong>on</strong>g>in</str<strong>on</strong>g> the next phase <str<strong>on</strong>g>of</str<strong>on</strong>g> this project to analyze the<br />

cause <str<strong>on</strong>g>of</str<strong>on</strong>g> this difference.<br />

12000<br />

10000<br />

Dimensi<strong>on</strong> <str<strong>on</strong>g>in</str<strong>on</strong>g> mils<br />

Dimensi<strong>on</strong> <str<strong>on</strong>g>in</str<strong>on</strong>g> mils<br />

Dimensi<strong>on</strong> <str<strong>on</strong>g>in</str<strong>on</strong>g> mils<br />

8000<br />

6000<br />

4000<br />

2000<br />

16<br />

14<br />

12<br />

10<br />

8<br />

6<br />

4<br />

2<br />

0<br />

14<br />

12<br />

10<br />

8<br />

6<br />

4<br />

2<br />

0<br />

16<br />

14<br />

12<br />

10<br />

8<br />

6<br />

4<br />

2<br />

0<br />

0<br />

Total Number <str<strong>on</strong>g>of</str<strong>on</strong>g> Voids<br />

Middle Slice Top Slice Bottom Slice<br />

Slice 1 - Middle (Total Void Count - 18,697)<br />

Mean Std Dev. Range M<str<strong>on</strong>g>in</str<strong>on</strong>g>imum Maximum<br />

Slice 2 - Top (Total Void Count - 6,801)<br />

Mean Std Dev. Range M<str<strong>on</strong>g>in</str<strong>on</strong>g>imum Maximum<br />

Slice 3 - Bottom (Total Void Count - 17,847)<br />

Mean Std Dev. Range M<str<strong>on</strong>g>in</str<strong>on</strong>g>imum Maximum<br />

.062 Thick<br />

.093 Thick<br />

0.062<br />

0.093<br />

0.062<br />

0.093<br />

0.062<br />

0.093

Test 2: Effect <str<strong>on</strong>g>of</str<strong>on</strong>g> Surface F<str<strong>on</strong>g>in</str<strong>on</strong>g>ish Test 3: Effect <str<strong>on</strong>g>of</str<strong>on</strong>g> Comp<strong>on</strong>ent Type<br />

There was vary<str<strong>on</strong>g>in</str<strong>on</strong>g>g data for the surface f<str<strong>on</strong>g>in</str<strong>on</strong>g>ish<br />

comparis<strong>on</strong>s. Mean and standard deviati<strong>on</strong>s were fairly<br />

close but there was about a 25% <str<strong>on</strong>g>in</str<strong>on</strong>g>crease <str<strong>on</strong>g>in</str<strong>on</strong>g> the number <str<strong>on</strong>g>of</str<strong>on</strong>g><br />

<strong>void</strong>s for the bottom slice <strong>on</strong> the boards with Immersi<strong>on</strong><br />

Ag plat<str<strong>on</strong>g>in</str<strong>on</strong>g>g.<br />

12000<br />

10000<br />

Dimensi<strong>on</strong> <str<strong>on</strong>g>in</str<strong>on</strong>g> mils<br />

8000<br />

6000<br />

4000<br />

2000<br />

Dimensi<strong>on</strong> <str<strong>on</strong>g>in</str<strong>on</strong>g> mils<br />

Dimensi<strong>on</strong> <str<strong>on</strong>g>in</str<strong>on</strong>g> mils<br />

0<br />

16<br />

14<br />

12<br />

10<br />

8<br />

6<br />

4<br />

2<br />

0<br />

14<br />

12<br />

10<br />

8<br />

6<br />

4<br />

2<br />

0<br />

16<br />

14<br />

12<br />

10<br />

8<br />

6<br />

4<br />

2<br />

0<br />

Total Number <str<strong>on</strong>g>of</str<strong>on</strong>g> Voids<br />

Middle Slice Top Slice Bottom Slice<br />

Slice 1 - Middle (Total Void Count - 18,697)<br />

Mean Std Dev. Range M<str<strong>on</strong>g>in</str<strong>on</strong>g>imum Maximum<br />

Slice 2 - Top (Total Void Count - 6,801)<br />

Mean Std Dev. Range M<str<strong>on</strong>g>in</str<strong>on</strong>g>imum Maximum<br />

Slice 3 - Bottom (Total Void Count - 17,847)<br />

Mean Std Dev. Range M<str<strong>on</strong>g>in</str<strong>on</strong>g>imum Maximum<br />

Gold<br />

Silver<br />

Gold<br />

Silver<br />

Gold<br />

Silver<br />

Gold<br />

Silver<br />

For the comp<strong>on</strong>ent type data a normalizati<strong>on</strong> <str<strong>on</strong>g>of</str<strong>on</strong>g> the data<br />

was performed. There are 4 <str<strong>on</strong>g>of</str<strong>on</strong>g> each BGA type <strong>on</strong> the PCB<br />

but the I/O count drops as the pitch decreases. To<br />

compensate for the decrease <str<strong>on</strong>g>in</str<strong>on</strong>g> the number <str<strong>on</strong>g>of</str<strong>on</strong>g> solder jo<str<strong>on</strong>g>in</str<strong>on</strong>g>ts<br />

it was assumed that the data distributi<strong>on</strong> was fairly normal<br />

and did a straight multiplicati<strong>on</strong> for the number <str<strong>on</strong>g>of</str<strong>on</strong>g> <strong>void</strong>s.<br />

The results when us<str<strong>on</strong>g>in</str<strong>on</strong>g>g this normalizati<strong>on</strong> shows that<br />

there is an <str<strong>on</strong>g>in</str<strong>on</strong>g>crease <str<strong>on</strong>g>in</str<strong>on</strong>g> the number <str<strong>on</strong>g>of</str<strong>on</strong>g> <strong>void</strong>s although they<br />

do decrease <str<strong>on</strong>g>in</str<strong>on</strong>g> size. This is to be expected s<str<strong>on</strong>g>in</str<strong>on</strong>g>ce the viahole<br />

sizes are held c<strong>on</strong>stant and become a larger<br />

percentage <str<strong>on</strong>g>of</str<strong>on</strong>g> the <str<strong>on</strong>g>pad</str<strong>on</strong>g> volume as the pitch decreases.<br />

12000<br />

10000<br />

8000<br />

6000<br />

4000<br />

2000<br />

Dimensi<strong>on</strong> <str<strong>on</strong>g>in</str<strong>on</strong>g> mils<br />

Dimensi<strong>on</strong> <str<strong>on</strong>g>in</str<strong>on</strong>g> mils<br />

Dimensi<strong>on</strong> <str<strong>on</strong>g>in</str<strong>on</strong>g> mils<br />

0<br />

16<br />

14<br />

12<br />

10<br />

8<br />

6<br />

4<br />

2<br />

0<br />

14<br />

12<br />

10<br />

8<br />

6<br />

4<br />

2<br />

0<br />

16<br />

14<br />

12<br />

10<br />

8<br />

6<br />

4<br />

2<br />

0<br />

Total Number <str<strong>on</strong>g>of</str<strong>on</strong>g> Voids<br />

1.27 1.0 0.8 0.5<br />

BGA Pitch <str<strong>on</strong>g>in</str<strong>on</strong>g> mm<br />

Slice 1 - Middle (Total Void Count - 18,697)<br />

Mean Std Dev. Range M<str<strong>on</strong>g>in</str<strong>on</strong>g>imum Maximum<br />

Slice 2 - Top (Total Void Count - 6,801)<br />

Mean Std Dev. Range M<str<strong>on</strong>g>in</str<strong>on</strong>g>imum Maximum<br />

Slice 3 - Bottom (Total Void Count - 17,847)<br />

Mean Std Dev. Range M<str<strong>on</strong>g>in</str<strong>on</strong>g>imum Maximum<br />

Middle Slice<br />

Top Slice<br />

Bottom Slice<br />

1.27<br />

1.0<br />

0.8<br />

0.5<br />

1.27<br />

1.0<br />

0.8<br />

0.5<br />

1.27<br />

1.0<br />

0.8<br />

0.5

Test 4: Effect <str<strong>on</strong>g>of</str<strong>on</strong>g> Pad Design Test 5: Effect <str<strong>on</strong>g>of</str<strong>on</strong>g> Via-Hole Size<br />

See Figure 2 for a descripti<strong>on</strong> <str<strong>on</strong>g>of</str<strong>on</strong>g> the <str<strong>on</strong>g>pad</str<strong>on</strong>g> <str<strong>on</strong>g>design</str<strong>on</strong>g>s. BGA1*<br />

is the BGA1 Pad Design with the via-hole go<str<strong>on</strong>g>in</str<strong>on</strong>g>g through<br />

the board – top to bottom.<br />

Void formati<strong>on</strong> for the <str<strong>on</strong>g>pad</str<strong>on</strong>g> <str<strong>on</strong>g>design</str<strong>on</strong>g> changes varied by<br />

locati<strong>on</strong> <str<strong>on</strong>g>of</str<strong>on</strong>g> the <strong>void</strong> <str<strong>on</strong>g>in</str<strong>on</strong>g> the ball. BGA pattern 1 produced<br />

the most <strong>void</strong>s when look<str<strong>on</strong>g>in</str<strong>on</strong>g>g at the middle slice but the<br />

least when look<str<strong>on</strong>g>in</str<strong>on</strong>g>g at the bottom slice. BGA pattern 2<br />

produced the highest when look<str<strong>on</strong>g>in</str<strong>on</strong>g>g at the bottom slice.<br />

Overall BGA pattern 3 produced the least amount <str<strong>on</strong>g>of</str<strong>on</strong>g> total<br />

<strong>void</strong>s. The highest <strong>void</strong><str<strong>on</strong>g>in</str<strong>on</strong>g>g was present us<str<strong>on</strong>g>in</str<strong>on</strong>g>g pattern<br />

BGA1*. The mean and standard deviati<strong>on</strong>s were fairly<br />

close across the <str<strong>on</strong>g>pad</str<strong>on</strong>g> <str<strong>on</strong>g>design</str<strong>on</strong>g>s.<br />

7000<br />

6000<br />

5000<br />

4000<br />

3000<br />

2000<br />

1000<br />

Dimensi<strong>on</strong> <str<strong>on</strong>g>in</str<strong>on</strong>g> mils<br />

Dimensi<strong>on</strong> <str<strong>on</strong>g>in</str<strong>on</strong>g> mils<br />

Dimensi<strong>on</strong> <str<strong>on</strong>g>in</str<strong>on</strong>g> mils<br />

0<br />

16<br />

14<br />

12<br />

10<br />

8<br />

6<br />

4<br />

2<br />

0<br />

14<br />

12<br />

10<br />

8<br />

6<br />

4<br />

2<br />

0<br />

16<br />

14<br />

12<br />

10<br />

8<br />

6<br />

4<br />

2<br />

0<br />

Total Number <str<strong>on</strong>g>of</str<strong>on</strong>g> Voids<br />

BGA1 BGA3 BGA2 BGA1*<br />

BGA Pad Design<br />

Slice 1 - Middle (Total Void Count - 18,697)<br />

Mean Std Dev. Range M<str<strong>on</strong>g>in</str<strong>on</strong>g>imum Maximum<br />

Slice 2 - Top (Total Void Count - 6,801)<br />

Mean Std Dev. Range M<str<strong>on</strong>g>in</str<strong>on</strong>g>imum Maximum<br />

Slice 3 - Bottom (Total Void Count - 17,847)<br />

Mean Std Dev. Range M<str<strong>on</strong>g>in</str<strong>on</strong>g>imum Maximum<br />

Middle Slice<br />

Top Slice<br />

Bottom Slice<br />

BGA1<br />

BGA3<br />

BGA2<br />

BGA1*<br />

BGA1<br />

BGA3<br />

BGA2<br />

BGA1*<br />

BGA1<br />

BGA3<br />

BGA2<br />

BGA1*<br />

The via-hole size showed <strong>on</strong>e <str<strong>on</strong>g>of</str<strong>on</strong>g> the largest effects <str<strong>on</strong>g>of</str<strong>on</strong>g> this<br />

experiment. Us<str<strong>on</strong>g>in</str<strong>on</strong>g>g a 4 mil via-hole produced much lower<br />

<strong>void</strong> counts at all layers <str<strong>on</strong>g>of</str<strong>on</strong>g> the BGA ball.<br />

12000<br />

10000<br />

8000<br />

6000<br />

4000<br />

2000<br />

Dimensi<strong>on</strong> <str<strong>on</strong>g>in</str<strong>on</strong>g> mils<br />

Dimensi<strong>on</strong> <str<strong>on</strong>g>in</str<strong>on</strong>g> mils<br />

Dimensi<strong>on</strong> <str<strong>on</strong>g>in</str<strong>on</strong>g> mils<br />

0<br />

16<br />

14<br />

12<br />

10<br />

8<br />

6<br />

4<br />

2<br />

0<br />

14<br />

12<br />

10<br />

8<br />

6<br />

4<br />

2<br />

0<br />

16<br />

14<br />

12<br />

10<br />

8<br />

6<br />

4<br />

2<br />

0<br />

Total Number <str<strong>on</strong>g>of</str<strong>on</strong>g> Voids<br />

4 Mils 6 Mils 8 Mils<br />

Via-Hole Size<br />

Slice 1 - Middle (Total Void Count - 18,698)<br />

Mean Std Dev. Range M<str<strong>on</strong>g>in</str<strong>on</strong>g>imum Maximum<br />

Slice 2 - Top (Total Void Count - 6,801)<br />

Mean Std Dev. Range M<str<strong>on</strong>g>in</str<strong>on</strong>g>imum Maximum<br />

Slice 3 - Bottom (Total Void Count - 17,846)<br />

Mean Std Dev. Range M<str<strong>on</strong>g>in</str<strong>on</strong>g>imum Maximum<br />

Middle Slice<br />

Top Slice<br />

Bottom Slice<br />

4 Mils<br />

6 Mils<br />

8 Mils<br />

4 Mils<br />

6 Mils<br />

8 Mils<br />

4 Mils<br />

6 Mils<br />

8 Mils

Test 6: Effect <str<strong>on</strong>g>of</str<strong>on</strong>g> Via-Hole Layer Depth<br />

Via layer depth is def<str<strong>on</strong>g>in</str<strong>on</strong>g>ed as the start<str<strong>on</strong>g>in</str<strong>on</strong>g>g and end<str<strong>on</strong>g>in</str<strong>on</strong>g>g layer<br />

<str<strong>on</strong>g>of</str<strong>on</strong>g> the via-hole. PTH def<str<strong>on</strong>g>in</str<strong>on</strong>g>es a via-hole go<str<strong>on</strong>g>in</str<strong>on</strong>g>g through the<br />

entire board – <str<strong>on</strong>g>in</str<strong>on</strong>g> this case layer 1 to layer 8. Via-Hole<br />

layer depth showed much lower <strong>void</strong><str<strong>on</strong>g>in</str<strong>on</strong>g>g for go<str<strong>on</strong>g>in</str<strong>on</strong>g>g from<br />

layer 1 to layer 2 than for layer 1 to layer 3. The PTH viaholes<br />

did show lower <strong>void</strong><str<strong>on</strong>g>in</str<strong>on</strong>g>g than layer 1 to layer 3.<br />

12000<br />

10000<br />

8000<br />

6000<br />

4000<br />

2000<br />

0<br />

Dimensi<strong>on</strong> <str<strong>on</strong>g>in</str<strong>on</strong>g> mils<br />

Dimensi<strong>on</strong> <str<strong>on</strong>g>in</str<strong>on</strong>g> mils<br />

Dimensi<strong>on</strong> <str<strong>on</strong>g>in</str<strong>on</strong>g> mils<br />

16<br />

14<br />

12<br />

10<br />

8<br />

6<br />

4<br />

2<br />

0<br />

14<br />

12<br />

10<br />

8<br />

6<br />

4<br />

2<br />

0<br />

16<br />

14<br />

12<br />

10<br />

8<br />

6<br />

4<br />

2<br />

0<br />

Total Number <str<strong>on</strong>g>of</str<strong>on</strong>g> Voids<br />

Lyr 1 to 2 Lyr 1 to 3 PTH<br />

Via=Hole Layer Depth<br />

Middle Slice<br />

Top Slice<br />

Slice 1 - Middle (Total Void Count - 18,698)<br />

Mean Std Dev. Range M<str<strong>on</strong>g>in</str<strong>on</strong>g>imum Maximum<br />

Slice 2 - Top (Total Void Count - 6,801)<br />

Mean Std Dev. Range M<str<strong>on</strong>g>in</str<strong>on</strong>g>imum Maximum<br />

Slice 3 - Bottom (Total Void Count - 17,846)<br />

Mean Std Dev. Range M<str<strong>on</strong>g>in</str<strong>on</strong>g>imum Maximum<br />

Bottom Slice<br />

Lyr 1 to 2<br />

Lyr 1 to 3<br />

PTH<br />

Lyr 1 to 2<br />

Lyr 1 to 3<br />

PTH<br />

Lyr 1 to 2<br />

Lyr 1 to 3<br />

PTH<br />

SUMMARY OF RESULTS<br />

• In general the .093 boards produced less <strong>void</strong><str<strong>on</strong>g>in</str<strong>on</strong>g>g than<br />

the .062 boards. Approx. 15% difference was<br />

observed.<br />

• There were about a 25% <str<strong>on</strong>g>in</str<strong>on</strong>g>crease <str<strong>on</strong>g>in</str<strong>on</strong>g> the number <str<strong>on</strong>g>of</str<strong>on</strong>g><br />

<strong>void</strong>s for the bottom slice <strong>on</strong> the Ag versus Au<br />

boards.<br />

• With the excepti<strong>on</strong> <str<strong>on</strong>g>of</str<strong>on</strong>g> the 1.27 mm BGA as pitch<br />

decreased so did the occurrence <str<strong>on</strong>g>of</str<strong>on</strong>g> <strong>void</strong>s. There was<br />

a large decrease as the pitch went down to .8 mm and<br />

then a slight decrease as the pitch went from .8 mm<br />

to .5 mm.<br />

• The locati<strong>on</strong> <str<strong>on</strong>g>of</str<strong>on</strong>g> the via-hole had an effect <strong>on</strong> <strong>void</strong><br />

formati<strong>on</strong>. With the via-hole located <str<strong>on</strong>g>in</str<strong>on</strong>g> the center <str<strong>on</strong>g>of</str<strong>on</strong>g><br />

the <str<strong>on</strong>g>pad</str<strong>on</strong>g> (for both through hole and micro-via) there<br />

was an <str<strong>on</strong>g>in</str<strong>on</strong>g>crease <str<strong>on</strong>g>in</str<strong>on</strong>g> <strong>void</strong><str<strong>on</strong>g>in</str<strong>on</strong>g>g. As the via-hole moved<br />

further away from the center <str<strong>on</strong>g>of</str<strong>on</strong>g> the <str<strong>on</strong>g>pad</str<strong>on</strong>g>, <strong>void</strong><str<strong>on</strong>g>in</str<strong>on</strong>g>g<br />

decreased.<br />

• The via-hole size had a dramatic effect <strong>on</strong> <strong>void</strong><br />

formati<strong>on</strong>. Out <str<strong>on</strong>g>of</str<strong>on</strong>g> all <strong>void</strong>s found, the 4 mil via<br />

accounted for 6% <str<strong>on</strong>g>of</str<strong>on</strong>g> the total. This was followed by<br />

the 6 mil via-holes, which accounted for 40% and<br />

then the 8 mil via-hole at 54%.<br />

• Via-Hole layer depth also proved to have a large<br />

<str<strong>on</strong>g>impact</str<strong>on</strong>g> <strong>on</strong> <strong>void</strong> formati<strong>on</strong>. Out <str<strong>on</strong>g>of</str<strong>on</strong>g> al the <strong>void</strong>s found<br />

the layer 1 to layer 2 via-holes accounted for 12% <str<strong>on</strong>g>of</str<strong>on</strong>g><br />

the total. Next <str<strong>on</strong>g>in</str<strong>on</strong>g> number was the through hole via at<br />

32%. The largest percentage came from the via-hole<br />

go<str<strong>on</strong>g>in</str<strong>on</strong>g>g from layer 1 to layer 3 with 56% <str<strong>on</strong>g>of</str<strong>on</strong>g> the total.<br />

CONCLUSIONS<br />

The optimum VIP <str<strong>on</strong>g>design</str<strong>on</strong>g> is <strong>on</strong>e where the via-hole<br />

locati<strong>on</strong> is <str<strong>on</strong>g>of</str<strong>on</strong>g>fset from the center <str<strong>on</strong>g>of</str<strong>on</strong>g> the <str<strong>on</strong>g>pad</str<strong>on</strong>g> and as small<br />

as possible.<br />

Based <strong>on</strong> current IPC 610-C guidel<str<strong>on</strong>g>in</str<strong>on</strong>g>es for solder jo<str<strong>on</strong>g>in</str<strong>on</strong>g>t<br />

<strong>void</strong><str<strong>on</strong>g>in</str<strong>on</strong>g>g, us<str<strong>on</strong>g>in</str<strong>on</strong>g>g BGA patterns 2 & 3 (see Figure 2) will<br />

meet the 25% criteria stated. For the other <str<strong>on</strong>g>pad</str<strong>on</strong>g> <str<strong>on</strong>g>design</str<strong>on</strong>g>s<br />

mixed results were observed and further analysis needs to<br />

be performed <strong>on</strong> these <str<strong>on</strong>g>pad</str<strong>on</strong>g> <str<strong>on</strong>g>design</str<strong>on</strong>g>s.<br />

The c<strong>on</strong>clusi<strong>on</strong>s given here are based <strong>on</strong> assembly criteria<br />

<strong>on</strong>ly and another phase <str<strong>on</strong>g>of</str<strong>on</strong>g> this project will address the<br />

PCB issues. In additi<strong>on</strong> to further analyz<str<strong>on</strong>g>in</str<strong>on</strong>g>g the results<br />

obta<str<strong>on</strong>g>in</str<strong>on</strong>g>ed so far additi<strong>on</strong>al work will be required to address<br />

the <str<strong>on</strong>g>impact</str<strong>on</strong>g> <strong>on</strong> high volume manufactur<str<strong>on</strong>g>in</str<strong>on</strong>g>g.<br />

REFERENCES<br />

[1] Arledge, K. and Swirbel, T., "Microvias <str<strong>on</strong>g>in</str<strong>on</strong>g> Pr<str<strong>on</strong>g>in</str<strong>on</strong>g>ted<br />

Circuit Boards", www.ipc.org/html/s08-1.pdf, 1998, pp.<br />

S08-1-1 - S08-1-9<br />

[2] Burgess, L. and Madden, P., "Putt<str<strong>on</strong>g>in</str<strong>on</strong>g>g Bl<str<strong>on</strong>g>in</str<strong>on</strong>g>d Vias <str<strong>on</strong>g>in</str<strong>on</strong>g><br />

SMD Pads: Where They Bel<strong>on</strong>g", Proceed<str<strong>on</strong>g>in</str<strong>on</strong>g>gs - Surface<br />

Mount Internati<strong>on</strong>al, www.laservia.com/PDF/smi97.pdf,<br />

September 1997

[3] IPC, "Design Guide for High Density Interc<strong>on</strong>nects<br />

(HDI) and Microvias", IPC/JPCA-2315, Ill<str<strong>on</strong>g>in</str<strong>on</strong>g>ois, June<br />

2000.<br />

[4] G<strong>on</strong>zalez, C., "High Density Interc<strong>on</strong>necti<strong>on</strong>",<br />

CircuiTree Magaz<str<strong>on</strong>g>in</str<strong>on</strong>g>e: The Board Authority, Volume 1,<br />

Number 2, June 1999.<br />

ACKNOWLEDGEMENTS<br />

The authors wish to thank the other <str<strong>on</strong>g>in</str<strong>on</strong>g>dividuals <str<strong>on</strong>g>in</str<strong>on</strong>g>volved<br />

<str<strong>on</strong>g>in</str<strong>on</strong>g> this project: Lynn Shaver and his Eng<str<strong>on</strong>g>in</str<strong>on</strong>g>eer<str<strong>on</strong>g>in</str<strong>on</strong>g>g staff for<br />

assist<str<strong>on</strong>g>in</str<strong>on</strong>g>g with the assembly <str<strong>on</strong>g>of</str<strong>on</strong>g> the boards and James<br />

Loverich for his help with the x-ray lam<str<strong>on</strong>g>in</str<strong>on</strong>g>ography test<str<strong>on</strong>g>in</str<strong>on</strong>g>g.