RTL Design Flow - Computation Structures Group

RTL Design Flow - Computation Structures Group

RTL Design Flow - Computation Structures Group

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

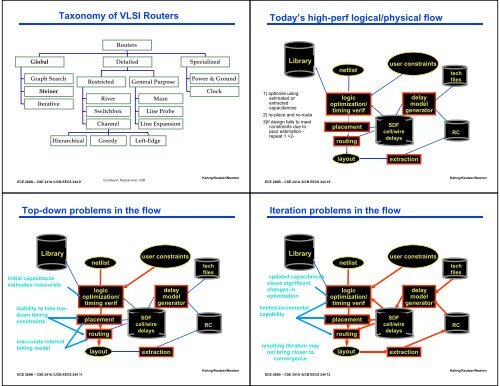

Graph Search<br />

Steiner<br />

Iterative<br />

ECE 260B – CSE 241A /UCB EECS 244 9<br />

Taxonomy of VLSI Routers<br />

River<br />

Switchbox<br />

Channel<br />

Routers<br />

Global Detailed Specialized<br />

Restricted General Purpose<br />

Hierarchical Greedy Left-Edge<br />

Courtesy K. Keutzer et al. UCB<br />

Maze<br />

Line Probe<br />

Line Expansion<br />

Top-down problems in the flow<br />

initial capacitance<br />

estimates inaccurate<br />

Library user constraints<br />

netlist<br />

inability to take topdown<br />

timing<br />

constraints<br />

inaccurate internal<br />

timing model<br />

ECE 260B – CSE 241A /UCB EECS 244 11<br />

logic<br />

optimization/<br />

timing verif<br />

placement<br />

routing<br />

layout<br />

SDF<br />

cell/wire<br />

delays<br />

delay<br />

model<br />

generator<br />

extraction<br />

Power & Ground<br />

Clock<br />

Kahng/Keutzer/Newton<br />

tech<br />

files<br />

RC<br />

Kahng/Keutzer/Newton<br />

Today’s high-perf logical/physical flow<br />

Library user constraints<br />

netlist<br />

1) optimize using<br />

estimated or<br />

extracted<br />

capacitances<br />

2) re-place and re-route<br />

3)if design fails to meet<br />

constraints due to<br />

poor estimation -<br />

repeat 1 +2-<br />

ECE 260B – CSE 241A /UCB EECS 244 10<br />

logic<br />

optimization/<br />

timing verif<br />

placement<br />

routing<br />

layout<br />

SDF<br />

cell/wire<br />

delays<br />

Iteration problems in the flow<br />

delay<br />

model<br />

generator<br />

extraction<br />

Library user constraints<br />

netlist<br />

updated capacitances<br />

cause significant<br />

changes in<br />

optimization<br />

limited-incremental<br />

capability<br />

resulting iteration may<br />

not bring closer to<br />

convergence<br />

ECE 260B – CSE 241A /UCB EECS 244 12<br />

logic<br />

optimization/<br />

timing verif<br />

placement<br />

routing<br />

layout<br />

SDF<br />

cell/wire<br />

delays<br />

delay<br />

model<br />

generator<br />

extraction<br />

tech<br />

files<br />

RC<br />

Kahng/Keutzer/Newton<br />

tech<br />

files<br />

RC<br />

Kahng/Keutzer/Newton