RTL Design Flow - Computation Structures Group

RTL Design Flow - Computation Structures Group

RTL Design Flow - Computation Structures Group

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

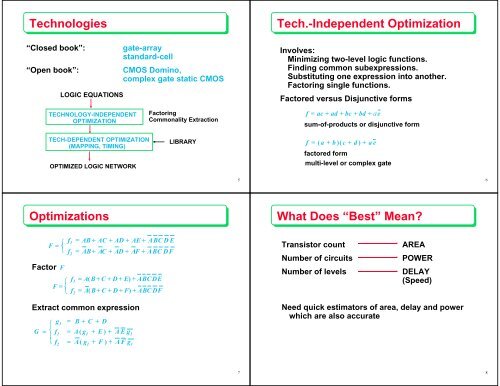

Technologies<br />

“Closed book”: gate-array<br />

standard-cell<br />

“Open book”: CMOS Domino,<br />

complex gate static CMOS<br />

LOGIC EQUATIONS<br />

TECHNOLOGY-INDEPENDENT<br />

OPTIMIZATION<br />

TECH-DEPENDENT OPTIMIZATION<br />

(MAPPING, TIMING)<br />

OPTIMIZED LOGIC NETWORK<br />

Optimizations<br />

F =<br />

⎧<br />

⎨<br />

⎩<br />

Factor F<br />

⎧<br />

F = ⎨<br />

⎩<br />

f 1 = AB + AC + AD + AE + A BC D E<br />

f 2 = AB + AC + AD + AF + A BC D F<br />

f1 = AB+ ( C + D + E)+ABCDE<br />

f2 = A( B + C + D + F)+ABCDF<br />

Extract common expression<br />

⎧ g1 = B + C + D<br />

G = ⎨ f1 ⎪<br />

⎩ f2 = A( g1 + E ) + A E g1 = A( g1 + F )+ A F g1 Factoring<br />

Commonality Extraction<br />

LIBRARY<br />

5<br />

7<br />

Tech.-Independent Optimization<br />

Involves:<br />

Minimizing two-level logic functions.<br />

Finding common subexpressions.<br />

Substituting one expression into another.<br />

Factoring single functions.<br />

Factored versus Disjunctive forms<br />

f = ac + ad + bc + bd + ae<br />

sum-of-products or disjunctive form<br />

f = ( a + b ) ( c + d ) + ae<br />

factored form<br />

multi-level or complex gate<br />

What Does “Best” Mean?<br />

Transistor count AREA<br />

Number of circuits POWER<br />

Number of levels DELAY<br />

(Speed)<br />

Need quick estimators of area, delay and power<br />

which are also accurate<br />

6<br />

8