Expect a Breakthrough Advantage in Next-Generation FPGAs - Altera

Expect a Breakthrough Advantage in Next-Generation FPGAs - Altera

Expect a Breakthrough Advantage in Next-Generation FPGAs - Altera

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

<strong>Next</strong>-<strong>Generation</strong> <strong>FPGAs</strong> and SoCs Are Com<strong>in</strong>g Page 9<br />

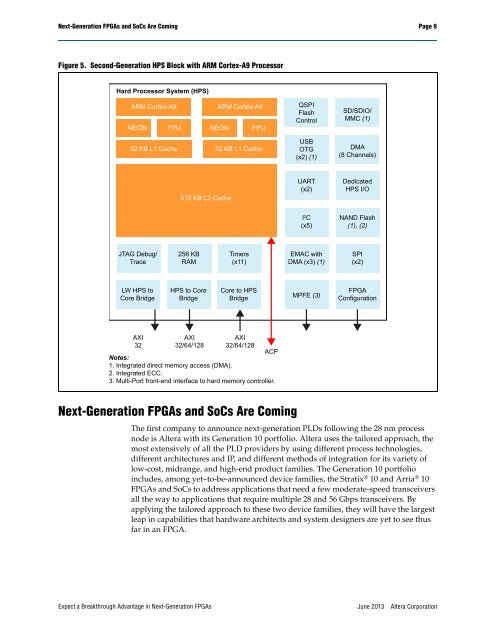

Figure 5. Second-<strong>Generation</strong> HPS Block with ARM Cortex-A9 Processor<br />

Hard Processor System (HPS)<br />

ARM Cortex-A9<br />

ARM Cortex-A9<br />

NEON FPU NEON FPU<br />

32 KB L1 Cache 32 KB L1 Cache<br />

QSPI<br />

Flash<br />

Control<br />

USB<br />

OTG<br />

(x2) (1)<br />

SD/SDIO/<br />

MMC (1)<br />

DMA<br />

(8 Channels)<br />

512 KB L2 Cache<br />

UART<br />

(x2)<br />

Dedicated<br />

HPS I/O<br />

I 2 C<br />

(x5)<br />

NAND Flash<br />

(1), (2)<br />

JTAG Debug/<br />

Trace<br />

256 KB<br />

RAM<br />

Timers<br />

(x11)<br />

EMAC with<br />

DMA (x3) (1)<br />

SPI<br />

(x2)<br />

LW HPS to<br />

Core Bridge<br />

HPS to Core<br />

Bridge<br />

Core to HPS<br />

Bridge<br />

MPFE (3)<br />

FPGA<br />

Configuration<br />

AXI<br />

32<br />

AXI<br />

32/64/128<br />

AXI<br />

32/64/128<br />

ACP<br />

Notes:<br />

1. Integrated direct memory access (DMA).<br />

2. Integrated ECC.<br />

3. Multi-Port front-end <strong>in</strong>terface to hard memory controller.<br />

<strong>Next</strong>-<strong>Generation</strong> <strong>FPGAs</strong> and SoCs Are Com<strong>in</strong>g<br />

The first company to announce next-generation PLDs follow<strong>in</strong>g the 28 nm process<br />

node is <strong>Altera</strong> with its <strong>Generation</strong> 10 portfolio. <strong>Altera</strong> uses the tailored approach, the<br />

most extensively of all the PLD providers by us<strong>in</strong>g different process technologies,<br />

different architectures and IP, and different methods of <strong>in</strong>tegration for its variety of<br />

low-cost, midrange, and high-end product families. The <strong>Generation</strong> 10 portfolio<br />

<strong>in</strong>cludes, among yet–to-be-announced device families, the Stratix ® 10 and Arria ® 10<br />

<strong>FPGAs</strong> and SoCs to address applications that need a few moderate-speed transceivers<br />

all the way to applications that require multiple 28 and 56 Gbps transceivers. By<br />

apply<strong>in</strong>g the tailored approach to these two device families, they will have the largest<br />

leap <strong>in</strong> capabilities that hardware architects and system designers are yet to see thus<br />

far <strong>in</strong> an FPGA.<br />

<strong>Expect</strong> a <strong>Breakthrough</strong> <strong>Advantage</strong> <strong>in</strong> <strong>Next</strong>-<strong>Generation</strong> <strong>FPGAs</strong><br />

June 2013<br />

<strong>Altera</strong> Corporation