ADF4251 Dual Fractional-N/Interger-N Frequency ... - Analog Devices

ADF4251 Dual Fractional-N/Interger-N Frequency ... - Analog Devices

ADF4251 Dual Fractional-N/Interger-N Frequency ... - Analog Devices

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

<strong>ADF4251</strong><br />

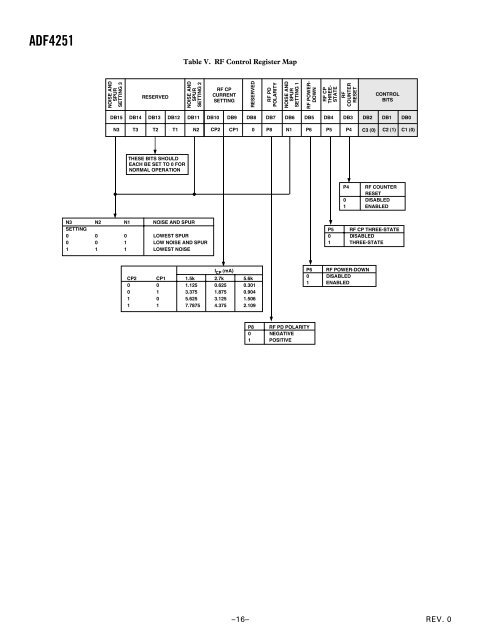

Table V. RF Control Register Map<br />

NOISE AND<br />

SPUR<br />

SETTING 3<br />

RESERVED<br />

NOISE AND<br />

SPUR<br />

SETTING 2<br />

RF CP<br />

CURRENT<br />

SETTING<br />

RESERVED<br />

RF PD<br />

POLARITY<br />

NOISE AND<br />

SPUR<br />

SETTING 1<br />

RF POWER-<br />

DOWN<br />

RF CP<br />

THREE-<br />

STATE<br />

RF<br />

COUNTER<br />

RESET<br />

CONTROL<br />

BITS<br />

DB15 DB14 DB13 DB12 DB11 DB10 DB9 DB8 DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0<br />

N3<br />

T3<br />

T2<br />

T1<br />

N2<br />

CP2<br />

CP1<br />

0<br />

P8<br />

N1<br />

P6<br />

P5<br />

P4<br />

C3 (0)<br />

C2 (1) C1 (0)<br />

THESE BITS SHOULD<br />

EACH BE SET TO 0 FOR<br />

NORMAL OPERATION<br />

P4 RF COUNTER<br />

RESET<br />

0 DISABLED<br />

1 ENABLED<br />

N3 N2 N1 NOISE AND SPUR<br />

SETTING<br />

0 0 0 LOWEST SPUR<br />

0 0 1 LOW NOISE AND SPUR<br />

1 1 1 LOWEST NOISE<br />

P5 RF CP THREE-STATE<br />

0 DISABLED<br />

1 THREE-STATE<br />

I CP (mA)<br />

CP2 CP1 1.5k 2.7k 5.6k<br />

0 0 1.125 0.625 0.301<br />

0 1 3.375 1.875 0.904<br />

1 0 5.625 3.125 1.506<br />

1 1 7.7875 4.375 2.109<br />

P6 RF POWER-DOWN<br />

0 DISABLED<br />

1 ENABLED<br />

P8 RF PD POLARITY<br />

0 NEGATIVE<br />

1 POSITIVE<br />

–16–<br />

REV. 0