PCS - Part 2: Multiprocessor Architectures

PCS - Part 2: Multiprocessor Architectures

PCS - Part 2: Multiprocessor Architectures

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

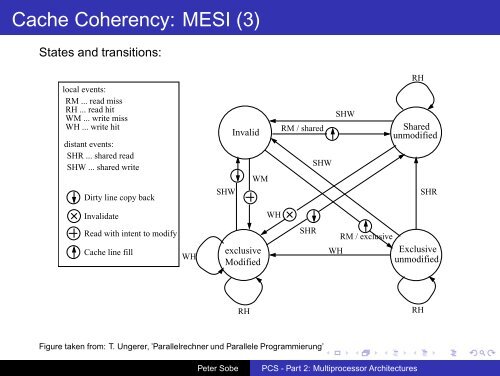

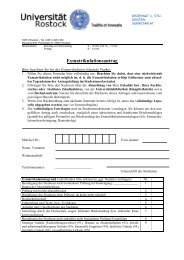

Cache Coherency: MESI (3)<br />

States and transitions:<br />

local events:<br />

RM ... read miss<br />

RH ... read hit<br />

WM ... write miss<br />

WH ... write hit<br />

distant events:<br />

SHR ... shared read<br />

SHW ... shared write<br />

Dirty line copy back<br />

Invalidate<br />

Read with intent to modify<br />

Cache line fill<br />

WH<br />

SHW<br />

Invalid<br />

WM<br />

exclusive<br />

Modified<br />

WH<br />

RM / shared<br />

SHR<br />

SHW<br />

WH<br />

SHW<br />

RM / exclusive<br />

RH<br />

Shared<br />

unmodified<br />

SHR<br />

Exclusive<br />

unmodified<br />

RH<br />

RH<br />

Figure taken from: T. Ungerer, ’Parallelrechner und Parallele Programmierung’<br />

Peter Sobe<br />

<strong>PCS</strong> - <strong>Part</strong> 2: <strong>Multiprocessor</strong> <strong>Architectures</strong>