PCS - Part 2: Multiprocessor Architectures

PCS - Part 2: Multiprocessor Architectures

PCS - Part 2: Multiprocessor Architectures

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

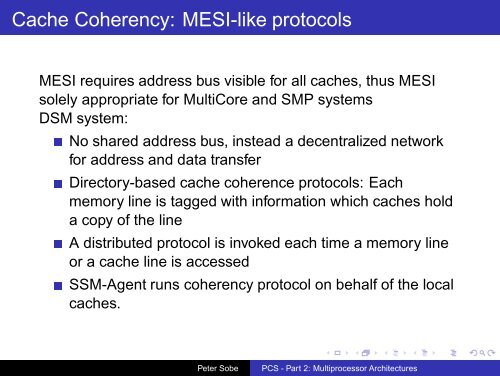

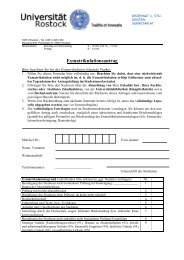

Cache Coherency: MESI-like protocols<br />

MESI requires address bus visible for all caches, thus MESI<br />

solely appropriate for MultiCore and SMP systems<br />

DSM system:<br />

No shared address bus, instead a decentralized network<br />

for address and data transfer<br />

Directory-based cache coherence protocols: Each<br />

memory line is tagged with information which caches hold<br />

a copy of the line<br />

A distributed protocol is invoked each time a memory line<br />

or a cache line is accessed<br />

SSM-Agent runs coherency protocol on behalf of the local<br />

caches.<br />

Peter Sobe<br />

<strong>PCS</strong> - <strong>Part</strong> 2: <strong>Multiprocessor</strong> <strong>Architectures</strong>