Unit – 3 Session - 12 Data Processing Circuits - VTU e-Learning ...

Unit – 3 Session - 12 Data Processing Circuits - VTU e-Learning ...

Unit – 3 Session - 12 Data Processing Circuits - VTU e-Learning ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

10CS 33 LOGIC DESIGN<br />

UNIT <strong>–</strong> 3 <strong>Data</strong> <strong>Processing</strong> <strong>Circuits</strong><br />

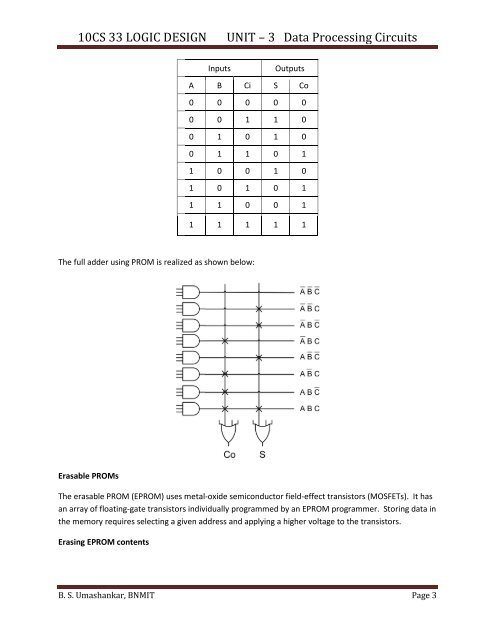

Inputs<br />

Outputs<br />

A B Ci S Co<br />

0 0 0 0 0<br />

0 0 1 1 0<br />

0 1 0 1 0<br />

0 1 1 0 1<br />

1 0 0 1 0<br />

1 0 1 0 1<br />

1 1 0 0 1<br />

1 1 1 1 1<br />

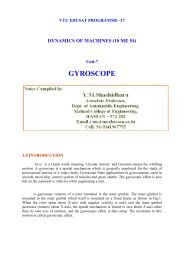

The full adder using PROM is realized as shown below:<br />

Erasable PROMs<br />

The erasable PROM (EPROM) uses metal-oxide semiconductor field-effect effect transistors (MOSFETs). It has<br />

an array of floating-gate gate transistors individually programmed by an EPROM programmer. Storing data in<br />

the memory requires selecting a given address and applying a higher voltage to the transistors.<br />

Erasing EPROM contents<br />

B. S. Umashankar, BNMIT<br />

Page 3