DUAL-PORT MEMORY BLOCK DIAGRAM DUALL-PORT RAM CELL

DUAL-PORT MEMORY BLOCK DIAGRAM DUALL-PORT RAM CELL

DUAL-PORT MEMORY BLOCK DIAGRAM DUALL-PORT RAM CELL

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

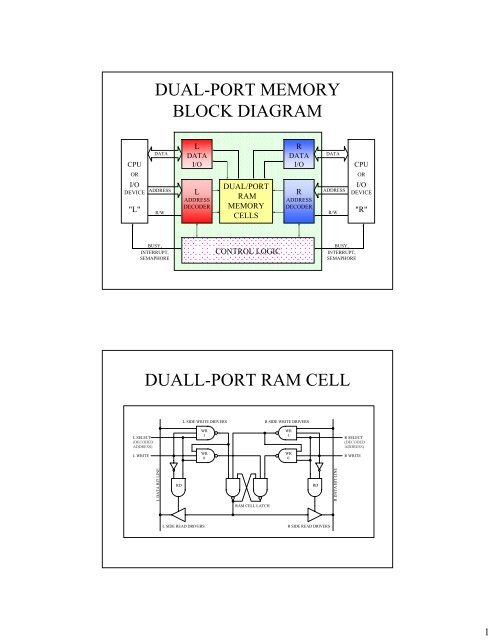

<strong>DUAL</strong>-<strong>PORT</strong> <strong>MEMORY</strong><br />

<strong>BLOCK</strong> <strong>DIAG<strong>RAM</strong></strong><br />

CPU<br />

OR<br />

I/O<br />

DEVICE<br />

"L"<br />

DATA<br />

ADDRESS<br />

R/W<br />

L<br />

DATA<br />

I/O<br />

L<br />

ADDRESS<br />

DECODER<br />

<strong>DUAL</strong>/<strong>PORT</strong><br />

<strong>RAM</strong><br />

<strong>MEMORY</strong><br />

<strong>CELL</strong>S<br />

R<br />

DATA<br />

I/O<br />

R<br />

ADDRESS<br />

DECODER<br />

DATA<br />

ADDRESS<br />

R/W<br />

CPU<br />

OR<br />

I/O<br />

DEVICE<br />

"R"<br />

BUSY,<br />

INTERRUPT,<br />

SEMAPHORE<br />

CONTROL LOGIC<br />

BUSY,<br />

INTERRUPT,<br />

SEMAPHORE<br />

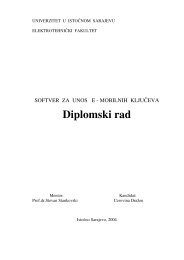

<strong>DUAL</strong>L-<strong>PORT</strong> <strong>RAM</strong> <strong>CELL</strong><br />

L SIDE WRITE DRIVERS<br />

R SIDE WRITE DRIVERS<br />

L SELECT<br />

(DECODED<br />

ADDRESS)<br />

L WRITE<br />

WR<br />

1<br />

WR<br />

0<br />

WR<br />

1<br />

WR<br />

0<br />

R SELECT<br />

(DECODED<br />

ADDRESS)<br />

R WRITE<br />

L DATA BIT LINE<br />

RD<br />

RD<br />

R DATA BIT LINE<br />

<strong>RAM</strong> <strong>CELL</strong> LATCH<br />

L SIDE READ DRIVERS<br />

R SIDE READ DRIVERS<br />

1

<strong>DUAL</strong>L-<strong>PORT</strong> <strong>RAM</strong> <strong>CELL</strong> - Read<br />

L SIDE WRITE DRIVERS<br />

R SIDE WRITE DRIVERS<br />

L SELECT<br />

(DECODED<br />

ADDRESS)<br />

L WRITE<br />

WR<br />

1<br />

WR<br />

0<br />

WR<br />

1<br />

WR<br />

0<br />

R SELECT<br />

(DECODED<br />

ADDRESS)<br />

R WRITE<br />

L DATA BIT LINE<br />

RD<br />

RD<br />

R DATA BIT LINE<br />

<strong>RAM</strong> <strong>CELL</strong> LATCH<br />

L SIDE READ DRIVERS<br />

R SIDE READ DRIVERS<br />

<strong>DUAL</strong>L-<strong>PORT</strong> <strong>RAM</strong> <strong>CELL</strong> - Write<br />

L SIDE WRITE DRIVERS<br />

R SIDE WRITE DRIVERS<br />

L SELECT<br />

(DECODED<br />

ADDRESS)<br />

L WRITE<br />

WR<br />

1<br />

WR<br />

0<br />

WR<br />

1<br />

WR<br />

0<br />

R SELECT<br />

(DECODED<br />

ADDRESS)<br />

R WRITE<br />

L DATA BIT LINE<br />

RD<br />

RD<br />

R DATA BIT LINE<br />

<strong>RAM</strong> <strong>CELL</strong> LATCH<br />

L SIDE READ DRIVERS<br />

R SIDE READ DRIVERS<br />

2

<strong>DUAL</strong>L-<strong>PORT</strong> <strong>RAM</strong><br />

Interrupt Logic<br />

L SIDE WRITE<br />

INTERRUPT<br />

TO R SIDE<br />

L SIDE<br />

ADDRESS<br />

ADDRESS<br />

= 3FF<br />

ADDRESS<br />

= 3FE<br />

R SIDE READ<br />

L SIDE READ<br />

ADDRESS<br />

= 3FF<br />

ADDRESS<br />

= 3FE<br />

R SIDE<br />

ADDRESS<br />

INTERRUPT<br />

TO L SIDE<br />

R SIDE WRITE<br />

DUUALL-<strong>PORT</strong> <strong>RAM</strong><br />

Busy Logic<br />

ADDRESS (L)<br />

DELAY BUFFER<br />

DELAY BUFFER<br />

ADDRESS (R)<br />

ADDRESS<br />

EQUAL<br />

COMPARATOR<br />

ADDRESS<br />

EQUAL<br />

COMPARATOR<br />

CE (L)<br />

CE (R)<br />

BUSY (L)<br />

L<br />

R<br />

BUSY (R)<br />

WRITE INHIBIT (L)<br />

A<br />

B<br />

WRITE INHIBIT (R)<br />

3

<strong>DUAL</strong>-<strong>PORT</strong> <strong>RAM</strong><br />

Semaphore Logic<br />

CPU<br />

OR<br />

I/O<br />

DEVICE<br />

"L"<br />

DATA<br />

ADDRESS<br />

R/W<br />

L<br />

DATA<br />

I/O<br />

L<br />

ADDRESS<br />

DECODER<br />

<strong>DUAL</strong>/<strong>PORT</strong><br />

<strong>RAM</strong><br />

<strong>MEMORY</strong><br />

<strong>CELL</strong>S<br />

R<br />

DATA<br />

I/O<br />

R<br />

ADDRESS<br />

DECODER<br />

DATA<br />

ADDRESS<br />

R/W<br />

CPU<br />

OR<br />

I/O<br />

DEVICE<br />

"R"<br />

SEMAPHORE<br />

SELECT<br />

SEMAPHORE<br />

<strong>CELL</strong>S<br />

SEMAPHORE<br />

SELECT<br />

<strong>DUAL</strong>-<strong>PORT</strong> <strong>RAM</strong><br />

Semaphore Logic cell<br />

L D-LATCH<br />

R D-LATCH<br />

L REQUEST<br />

D<br />

Q<br />

1 1<br />

Q<br />

D<br />

R REQUEST<br />

L WR SEMAPHORE<br />

E<br />

E<br />

R WR SEMAPHORE<br />

GRANT (L)<br />

SEMAPHORE<br />

ARBITRATION<br />

LATCH<br />

GRANT (R)<br />

4