STM8S and STM8A microcontroller families

STM8S and STM8A microcontroller families

STM8S and STM8A microcontroller families

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

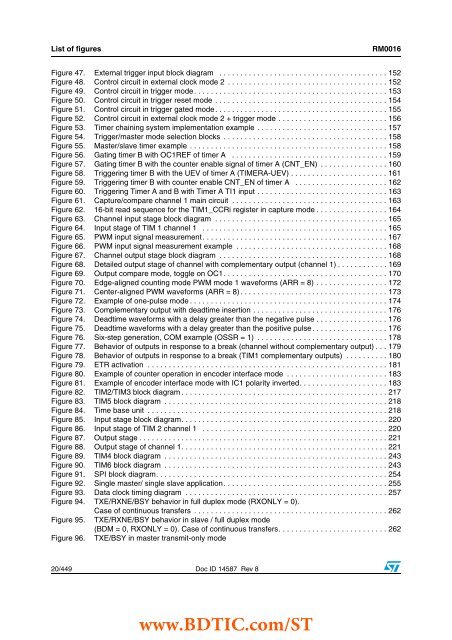

List of figures<br />

RM0016<br />

Figure 47. External trigger input block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152<br />

Figure 48. Control circuit in external clock mode 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152<br />

Figure 49. Control circuit in trigger mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153<br />

Figure 50. Control circuit in trigger reset mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 154<br />

Figure 51. Control circuit in trigger gated mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155<br />

Figure 52. Control circuit in external clock mode 2 + trigger mode . . . . . . . . . . . . . . . . . . . . . . . . . . 156<br />

Figure 53. Timer chaining system implementation example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157<br />

Figure 54. Trigger/master mode selection blocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158<br />

Figure 55. Master/slave timer example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158<br />

Figure 56. Gating timer B with OC1REF of timer A . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159<br />

Figure 57. Gating timer B with the counter enable signal of timer A (CNT_EN) . . . . . . . . . . . . . . . . 160<br />

Figure 58. Triggering timer B with the UEV of timer A (TIMERA-UEV) . . . . . . . . . . . . . . . . . . . . . . . 161<br />

Figure 59. Triggering timer B with counter enable CNT_EN of timer A . . . . . . . . . . . . . . . . . . . . . . 162<br />

Figure 60. Triggering Timer A <strong>and</strong> B with Timer A TI1 input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163<br />

Figure 61. Capture/compare channel 1 main circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163<br />

Figure 62. 16-bit read sequence for the TIM1_CCRi register in capture mode . . . . . . . . . . . . . . . . . 164<br />

Figure 63. Channel input stage block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165<br />

Figure 64. Input stage of TIM 1 channel 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165<br />

Figure 65. PWM input signal measurement. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167<br />

Figure 66. PWM input signal measurement example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168<br />

Figure 67. Channel output stage block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168<br />

Figure 68. Detailed output stage of channel with complementary output (channel 1) . . . . . . . . . . . . 169<br />

Figure 69. Output compare mode, toggle on OC1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 170<br />

Figure 70. Edge-aligned counting mode PWM mode 1 waveforms (ARR = 8) . . . . . . . . . . . . . . . . . 172<br />

Figure 71. Center-aligned PWM waveforms (ARR = 8) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173<br />

Figure 72. Example of one-pulse mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 174<br />

Figure 73. Complementary output with deadtime insertion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 176<br />

Figure 74. Deadtime waveforms with a delay greater than the negative pulse . . . . . . . . . . . . . . . . . 176<br />

Figure 75. Deadtime waveforms with a delay greater than the positive pulse. . . . . . . . . . . . . . . . . . 176<br />

Figure 76. Six-step generation, COM example (OSSR = 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 178<br />

Figure 77. Behavior of outputs in response to a break (channel without complementary output) . . . 179<br />

Figure 78. Behavior of outputs in response to a break (TIM1 complementary outputs) . . . . . . . . . . 180<br />

Figure 79. ETR activation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 181<br />

Figure 80. Example of counter operation in encoder interface mode . . . . . . . . . . . . . . . . . . . . . . . . 183<br />

Figure 81. Example of encoder interface mode with IC1 polarity inverted. . . . . . . . . . . . . . . . . . . . . 183<br />

Figure 82. TIM2/TIM3 block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 217<br />

Figure 83. TIM5 block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 218<br />

Figure 84. Time base unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 218<br />

Figure 85. Input stage block diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 220<br />

Figure 86. Input stage of TIM 2 channel 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 220<br />

Figure 87. Output stage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 221<br />

Figure 88. Output stage of channel 1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 221<br />

Figure 89. TIM4 block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 243<br />

Figure 90. TIM6 block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 243<br />

Figure 91. SPI block diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 254<br />

Figure 92. Single master/ single slave application. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 255<br />

Figure 93. Data clock timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 257<br />

Figure 94. TXE/RXNE/BSY behavior in full duplex mode (RXONLY = 0).<br />

Case of continuous transfers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 262<br />

Figure 95. TXE/RXNE/BSY behavior in slave / full duplex mode<br />

(BDM = 0, RXONLY = 0). Case of continuous transfers. . . . . . . . . . . . . . . . . . . . . . . . . . 262<br />

Figure 96. TXE/BSY in master transmit-only mode<br />

20/449 Doc ID 14587 Rev 8<br />

www.BDTIC.com/ST