implementation of turbo decoder using max-log-map ... - ijater

implementation of turbo decoder using max-log-map ... - ijater

implementation of turbo decoder using max-log-map ... - ijater

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

The MAP algorithm provides the best performance in<br />

BER while its complexity is higher than the two-step SO-<br />

VA.<br />

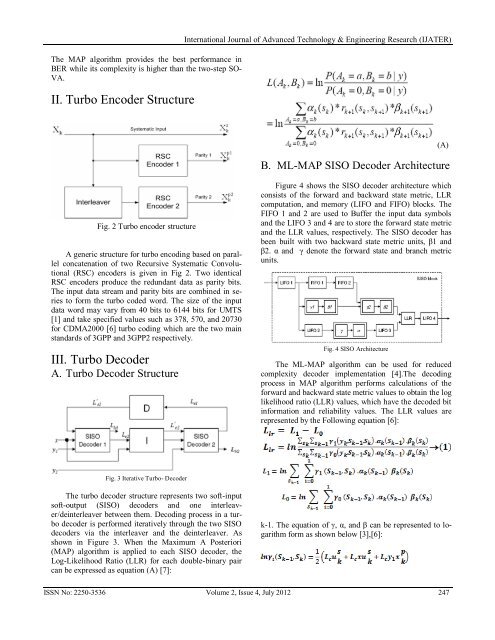

II. Turbo Encoder Structure<br />

International Journal <strong>of</strong> Advanced Techno<strong>log</strong>y & Engineering Research (IJATER)<br />

(A)<br />

B. ML-MAP SISO Decoder Architecture<br />

Fig. 2 Turbo encoder structure<br />

A generic structure for <strong>turbo</strong> encoding based on parallel<br />

concatenation <strong>of</strong> two Recursive Systematic Convolutional<br />

(RSC) encoders is given in Fig 2. Two identical<br />

RSC encoders produce the redundant data as parity bits.<br />

The input data stream and parity bits are combined in series<br />

to form the <strong>turbo</strong> coded word. The size <strong>of</strong> the input<br />

data word may vary from 40 bits to 6144 bits for UMTS<br />

[1] and take specified values such as 378, 570, and 20730<br />

for CDMA2000 [6] <strong>turbo</strong> coding which are the two main<br />

standards <strong>of</strong> 3GPP and 3GPP2 respectively.<br />

III. Turbo Decoder<br />

A. Turbo Decoder Structure<br />

Figure 4 shows the SISO <strong>decoder</strong> architecture which<br />

consists <strong>of</strong> the forward and backward state metric, LLR<br />

computation, and memory (LIFO and FIFO) blocks. The<br />

FIFO 1 and 2 are used to Buffer the input data symbols<br />

and the LIFO 3 and 4 are to store the forward state metric<br />

and the LLR values, respectively. The SISO <strong>decoder</strong> has<br />

been built with two backward state metric units, β1 and<br />

β2. α and γ denote the forward state and branch metric<br />

units.<br />

Fig. 4 SISO Architecture<br />

The ML-MAP algorithm can be used for reduced<br />

complexity <strong>decoder</strong> <strong>implementation</strong> [4].The decoding<br />

process in MAP algorithm performs calculations <strong>of</strong> the<br />

forward and backward state metric values to obtain the <strong>log</strong><br />

likelihood ratio (LLR) values, which have the decoded bit<br />

information and reliability values. The LLR values are<br />

represented by the Following equation [6]:<br />

Fig. 3 Iterative Turbo- Decoder<br />

The <strong>turbo</strong> <strong>decoder</strong> structure represents two s<strong>of</strong>t-input<br />

s<strong>of</strong>t-output (SISO) <strong>decoder</strong>s and one interleaver/deinterleaver<br />

between them. Decoding process in a <strong>turbo</strong><br />

<strong>decoder</strong> is performed iteratively through the two SISO<br />

<strong>decoder</strong>s via the interleaver and the deinterleaver. As<br />

shown in Figure 3. When the Maximum A Posteriori<br />

(MAP) algorithm is applied to each SISO <strong>decoder</strong>, the<br />

Log-Likelihood Ratio (LLR) for each double-binary pair<br />

can be expressed as equation (A) [7]:<br />

k-1. The equation <strong>of</strong> γ, α, and β can be represented to <strong>log</strong>arithm<br />

form as shown below [3],[6]:<br />

ISSN No: 2250-3536 Volume 2, Issue 4, July 2012 247