implementation of turbo decoder using max-log-map ... - ijater

implementation of turbo decoder using max-log-map ... - ijater

implementation of turbo decoder using max-log-map ... - ijater

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

International Journal <strong>of</strong> Advanced Techno<strong>log</strong>y & Engineering Research (IJATER)<br />

The <strong>log</strong>-MAP algorithm is the most complex <strong>of</strong> the<br />

four algorithms when implemented in s<strong>of</strong>tware, but as will<br />

be shown later, generally <strong>of</strong>fers the best bit error rate<br />

(BER) performance. The <strong>max</strong>-<strong>log</strong>-MAP algorithm is the<br />

least complex <strong>of</strong> the four algorithms (it has twice the<br />

complexity <strong>of</strong> the Viterbi algorithm for each half-iteration)<br />

but <strong>of</strong>fers the worst BER performance [9]. The <strong>max</strong>-<strong>log</strong>-<br />

MAP algorithm has the additional benefit <strong>of</strong> being tolerant<br />

<strong>of</strong> imperfect noise variance estimates when operating on<br />

an AWGN channel.<br />

F. SIMULATION RESULTS<br />

pipelining architecture introducing for performing LLR<br />

value computations, has been shown that <strong>decoder</strong><br />

achieved a slight reduction in power consumption and a<br />

slight increase in area usage, it has achieved 58% speedup<br />

compared to non-pipelined conventional <strong>decoder</strong>.<br />

Therefore, by adopting this kind <strong>of</strong> techniques, the <strong>turbo</strong><br />

<strong>decoder</strong> can be applied to wireless communication systems<br />

requiring high data rates and low power consumption.<br />

Further <strong>implementation</strong> <strong>of</strong> improved techno<strong>log</strong>ies<br />

like “sliding window” can improve the performance with<br />

slight increase in resources.<br />

V. Acknowledgment<br />

The authors would like to thank Dr. A. T. Kalghatgi,<br />

Chief Scientist, Mr. Manoj Jain, Member (Senior Research<br />

Staff), Mrs. A.Thirija Sharmila, Member (Senior<br />

Research Staff) and Mr. Chaitanya Umbare Member (Research<br />

Staff), Central Research Laboratory, Bangalore, for<br />

their constant encouragement and support to carry out this<br />

work.<br />

VI. References<br />

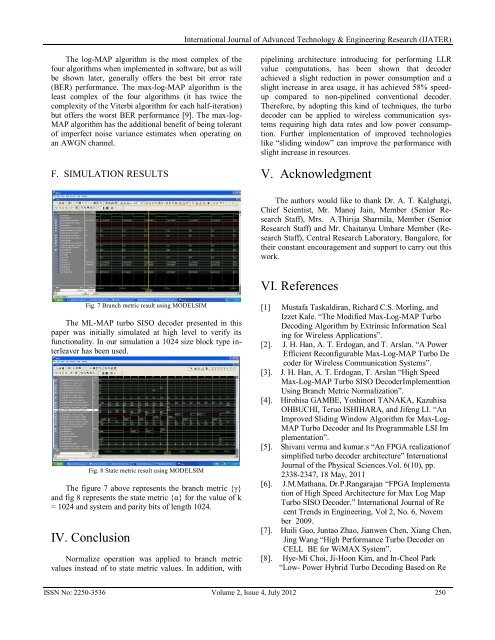

Fig. 7 Branch metric result <strong>using</strong> MODELSIM<br />

The ML-MAP <strong>turbo</strong> SISO <strong>decoder</strong> presented in this<br />

paper was initially simulated at high level to verify its<br />

functionality. In our simulation a 1024 size block type interleaver<br />

has been used.<br />

Fig. 8 State metric result <strong>using</strong> MODELSIM<br />

The figure 7 above represents the branch metric {γ}<br />

and fig 8 represents the state metric {α} for the value <strong>of</strong> k<br />

= 1024 and system and parity bits <strong>of</strong> length 1024.<br />

IV. Conclusion<br />

Normalize operation was applied to branch metric<br />

values instead <strong>of</strong> to state metric values. In addition, with<br />

[1] Mustafa Taskaldiran, Richard C.S. Morling, and<br />

Izzet Kale. “The Modified Max-Log-MAP Turbo<br />

Decoding Algorithm by Extrinsic Information Scal<br />

ing for Wireless Applications”.<br />

[2]. J. H. Han, A. T. Erdogan, and T. Arslan. “A Power<br />

Efficient Reconfigurable Max-Log-MAP Turbo De<br />

coder for Wireless Communication Systems”.<br />

[3]. J. H. Han, A. T. Erdogan, T. Arslan “High Speed<br />

Max-Log-MAP Turbo SISO DecoderImplementtion<br />

Using Branch Metric Normalization”.<br />

[4]. Hirohisa GAMBE, Yoshinori TANAKA, Kazuhisa<br />

OHBUCHI, Teruo ISHIHARA, and Jifeng LI. “An<br />

Improved Sliding Window Algorithm for Max-Log-<br />

MAP Turbo Decoder and Its Programmable LSI Im<br />

plementation”.<br />

[5]. Shivani verma and kumar.s “An FPGA realization<strong>of</strong><br />

simplified <strong>turbo</strong> <strong>decoder</strong> architecture” International<br />

Journal <strong>of</strong> the Physical Sciences.Vol. 6(10), pp.<br />

2338-2347, 18 May, 2011<br />

[6]. J.M.Mathana, Dr.P.Rangarajan “FPGA Implementa<br />

tion <strong>of</strong> High Speed Architecture for Max Log Map<br />

Turbo SISO Decoder.” International Journal <strong>of</strong> Re<br />

cent Trends in Engineering, Vol 2, No. 6, Novem<br />

ber 2009.<br />

[7]. Huili Guo, Juntao Zhao, Jianwen Chen, Xiang Chen,<br />

Jing Wang “High Performance Turbo Decoder on<br />

CELL BE for WiMAX System”.<br />

[8]. Hye-Mi Choi, Ji-Hoon Kim, and In-Cheol Park<br />

“Low- Power Hybrid Turbo Decoding Based on Re<br />

ISSN No: 2250-3536 Volume 2, Issue 4, July 2012 250