Ultra-low-power 32-bit MCU ARM-based Cortex-M3, 384KB ... - Keil

Ultra-low-power 32-bit MCU ARM-based Cortex-M3, 384KB ... - Keil

Ultra-low-power 32-bit MCU ARM-based Cortex-M3, 384KB ... - Keil

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

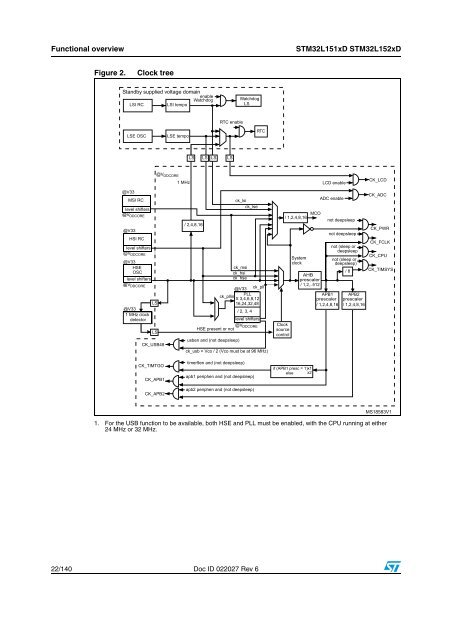

Functional overview<br />

STM<strong>32</strong>L151xD STM<strong>32</strong>L152xD<br />

Figure 2.<br />

Clock tree<br />

Standby supplied voltage domain<br />

enable<br />

Watchdog<br />

LSI RC<br />

LSI tempo<br />

Watchdog<br />

LS<br />

RTC enable<br />

LSE OSC<br />

LSE tempo<br />

RTC<br />

LS LS LS LS<br />

1 MHz<br />

LCD enable<br />

CK_LCD<br />

@V33<br />

MSI RC<br />

level shifters<br />

@V DDCORE<br />

@V33<br />

HSI RC<br />

level shifters<br />

@V DDCORE<br />

@V33<br />

HSE<br />

OSC<br />

level shifters<br />

@V DDCORE<br />

@V33<br />

1 MHz clock<br />

detector<br />

LS<br />

LS<br />

CK_USB48<br />

CK_TIMTGO<br />

CK_APB1<br />

CK_APB2<br />

@V DDCORE<br />

ck_lsi<br />

ck_lse<br />

/ 1,2,4,8,16<br />

/ 2,4,8,16<br />

ck_msi<br />

ck_hsi<br />

ck_hse<br />

@V33<br />

ck_pll<br />

PLL<br />

ck_pllin<br />

X 3,4,6,8,12<br />

16,24,<strong>32</strong>,48<br />

level shifters<br />

@V DDCORE<br />

HSE present or not<br />

usben and (not deepsleep)<br />

ck_usb = Vco / 2 (Vco must be at 96 MHz)<br />

timer9en and (not deepsleep)<br />

/ 2, 3, 4<br />

apb1 periphen and (not deepsleep)<br />

apb2 periphen and (not deepsleep)<br />

Clock<br />

source<br />

control<br />

System<br />

clock<br />

MCO<br />

AHB<br />

prescaler<br />

/ 1,2,..512<br />

if (APB1 presc = 1)x1<br />

else x2<br />

ADC enable<br />

not deepsleep<br />

not deepsleep<br />

not (sleep or<br />

deepsleep<br />

not (sleep or<br />

deepsleep)<br />

APB1 APB2<br />

prescaler prescaler<br />

/ 1,2,4,8,16 / 1,2,4,8,16<br />

CK_ADC<br />

CK_PWR<br />

CK_FCLK<br />

CK_CPU<br />

/ 8 CK_TIMSYS<br />

MS18583V1<br />

1. For the USB function to be available, both HSE and PLL must be enabled, with the CPU running at either<br />

24 MHz or <strong>32</strong> MHz.<br />

22/140 Doc ID 022027 Rev 6