- Page 3 and 4:

Hitachi 8-Bit MicrocomputerHD63265F

- Page 5 and 6:

CONTENTSSection 1.General Descripti

- Page 7 and 8:

SECTION 1.GENERAL DESCRIPTION1.1 IN

- Page 9 and 10:

. Maximum drive control range:- Num

- Page 11 and 12:

SECTION 2.PIN DESCRIPTION2.1 PIN CO

- Page 13 and 14:

Table 2-1.TypePin FunctionsPin No.D

- Page 15 and 16:

RS(Register Select): RS selects the

- Page 17 and 18:

They must be tied to low.NC(No Conn

- Page 19 and 20:

Bit 4BSY (Controller Busy): Bit 4 i

- Page 21 and 22:

During DMA transfer, in which the F

- Page 23 and 24:

During polling, if the ready signal

- Page 25 and 26:

A: Auto precompensationWhen A = 1,

- Page 27 and 28:

6.2.6 ESN: End Sector NumberFigure

- Page 29 and 30:

6.2.12 STEP: Stepo o o o o o S T E

- Page 31 and 32:

HOUT: HDUT specifies the time to wa

- Page 33 and 34:

6.2.17 PCl, PCO: Precompensation De

- Page 35 and 36:

INC (Interrupt Code): INC (figure 6

- Page 37 and 38:

DDA (Deleted Data Address Mark): DD

- Page 39 and 40:

Commands other than CHECK related a

- Page 41 and 42:

The above commands do not activate

- Page 43 and 44:

READ, WRITE,COMPARE commandRead a r

- Page 45 and 46:

CHECK DEVICEWrite a commandparamete

- Page 47 and 48:

SPECIFY 1, 2corrunandwrite a corrun

- Page 49 and 50:

6.5 COMMAND FUNCTIONS6.5.1 READ DAT

- Page 51 and 52:

egister within the periods shown in

- Page 53 and 54:

6.5.2 READ DELETED DATABit D7 D6 D5

- Page 55 and 56:

CA byte does not match, only the IN

- Page 57 and 58:

6.5.5 WRITE DATABi t D7 D6 D5 D4 D3

- Page 59 and 60:

HEX 00 is written for the remaining

- Page 61 and 62:

6.5.7 WRITE FORMATBi t D7 D6 D5 D4-

- Page 63 and 64:

6.5.8 SEEKBit D7 D6 D5 D4- D3 D2 Dl

- Page 65 and 66:

6.5.9 RECALIBRATEBit D7 D6 D5 D4- D

- Page 67 and 68:

Table 6-13.Data Overrun Times8"/S"

- Page 69 and 70:

6.5.11 COMPARE LOW OR EQUALBit D7 D

- Page 71 and 72:

6.5.13 CHECK DEVICE STATUSBit D7 D6

- Page 73 and 74:

6.5.15 SPECIFY 1Bit D7 I D6 I D5 I

- Page 75 and 76:

6.5.17 SLEEPBi t D7I D6 I D5 I D4-

- Page 77 and 78:

6.5.19 READ LONGBit D7 D6 D5 D4- D3

- Page 79 and 80: 6.5.21 INVALIDBit D'jI D6 I Ds I DI

- Page 81 and 82: 6.7 Command Code Rejection6.7.1 Phe

- Page 83 and 84: Command Rejection Timing Condition

- Page 85 and 86: 6.7.2 CountermeasuresHitachi recomm

- Page 87 and 88: STR Check (valid for all commands e

- Page 89 and 90: ABORT Command Issue (valid for all

- Page 91 and 92: SECTION 7.VFO CIRCUITThe VFO circui

- Page 93 and 94: Reset FDCFDC's operationReset SYNC

- Page 95 and 96: SECTION 8.WRITE PRECOMPENSATION CIR

- Page 97 and 98: 9.2 SYSTEM OPERATION SEQUENCEFigure

- Page 99 and 100: 9.3.2 WRITE OperationFigure 9-4 sho

- Page 101 and 102: Table 9-1.FDC Data Transfer Timing8

- Page 103 and 104: 9.5 FDC CONTROL9.5.1 FDC Operating

- Page 105 and 106: CSRS (Ao )RDWRDATAtAH(min)PVVimL On

- Page 107 and 108: Since the DACK signal of the FDC ca

- Page 109 and 110: 9.6.2 68-Series 8-Bit Bus SystemFig

- Page 111 and 112: R/W, CS and RS are sampled at the r

- Page 113 and 114: Table 9-3Data Transfer Rate Selecti

- Page 115 and 116: HD63265 (FDC)WDATA~----------------

- Page 117 and 118: Table 9-5.8" FDD Interface Signals

- Page 119 and 120: Table 9-7.3.5" FDD Interface Signal

- Page 121 and 122: 10.3 ELECTRICAL CHARACTERISTICS10.3

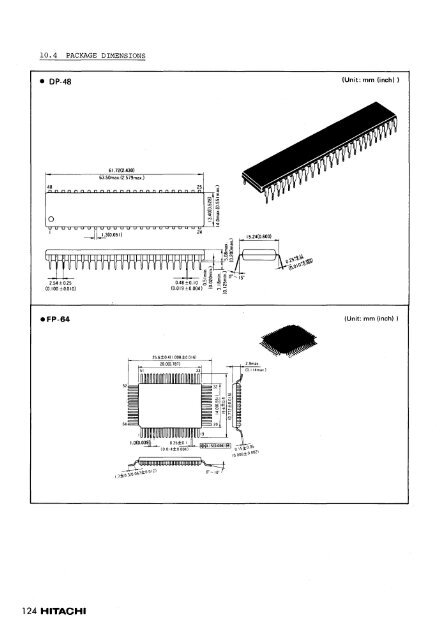

- Page 123 and 124: AC Specification (cant)No. Item Sym

- Page 125 and 126: ~ReadcycleWritecycleRS,C S00-07(out

- Page 127 and 128: @tususa. US1. HDIRtupSTEPFigure 10-

- Page 129: 5.0V2.4 kQIS2074 ®All diodesare 1S