FA526 32-BIT RISC CPU - Faraday Technology Corporation

FA526 32-BIT RISC CPU - Faraday Technology Corporation

FA526 32-BIT RISC CPU - Faraday Technology Corporation

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

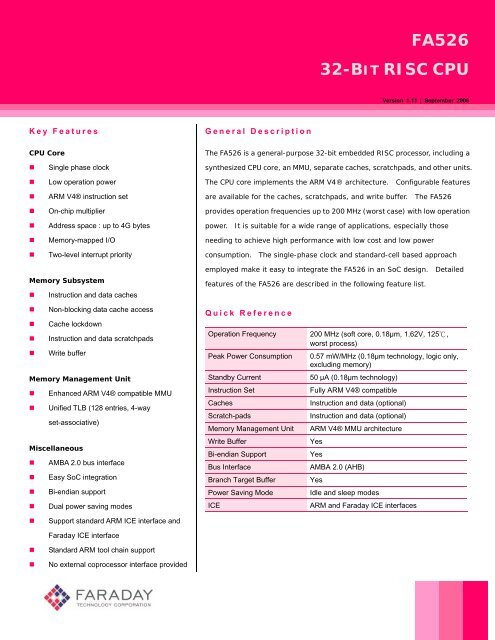

<strong>FA526</strong><strong>32</strong>-<strong>BIT</strong> <strong>RISC</strong> <strong>CPU</strong>Version 1.11 | September 2006Key FeaturesGeneral Description<strong>CPU</strong> Core• Single phase clock• Low operation power• ARM V4® instruction set• On-chip multiplier• Address space : up to 4G bytes• Memory-mapped I/O• Two-level interrupt priorityMemory Subsystem• Instruction and data caches• Non-blocking data cache access• Cache lockdown• Instruction and data scratchpads• Write bufferMemory Management Unit• Enhanced ARM V4® compatible MMU• Unified TLB (128 entries, 4-wayset-associative)Miscellaneous• AMBA 2.0 bus interface• Easy SoC integration• Bi-endian support• Dual power saving modesThe <strong>FA526</strong> is a general-purpose <strong>32</strong>-bit embedded <strong>RISC</strong> processor, including asynthesized <strong>CPU</strong> core, an MMU, separate caches, scratchpads, and other units.The <strong>CPU</strong> core implements the ARM V4® architecture. Configurable featuresare available for the caches, scratchpads, and write buffer. The <strong>FA526</strong>provides operation frequencies up to 200 MHz (worst case) with low operationpower. It is suitable for a wide range of applications, especially thoseneeding to achieve high performance with low cost and low powerconsumption. The single-phase clock and standard-cell based approachemployed make it easy to integrate the <strong>FA526</strong> in an SoC design. Detailedfeatures of the <strong>FA526</strong> are described in the following feature list.Quick ReferenceOperation Frequency 200 MHz (soft core, 0.18µm, 1.62V, 125℃,worst process)Peak Power Consumption 0.57 mW/MHz (0.18µm technology, logic only,excluding memory)Standby CurrentInstruction SetCachesScratch-padsMemory Management UnitWrite BufferBi-endian SupportBus InterfaceBranch Target BufferPower Saving ModeICE50 µA (0.18µm technology)Fully ARM V4® compatibleInstruction and data (optional)Instruction and data (optional)ARM V4® MMU architectureYesYesAMBA 2.0 (AHB)YesIdle and sleep modesARM and <strong>Faraday</strong> ICE interfaces• Support standard ARM ICE interface and<strong>Faraday</strong> ICE interface• Standard ARM tool chain support• No external coprocessor interface provided

<strong>FA526</strong><strong>32</strong>-<strong>BIT</strong> <strong>RISC</strong> <strong>CPU</strong>Version 1.11 | September 2006Functional BlocksJTAG ICE interfaceJTAG-ICE/F-ICEBTBFIQn, IRQnI-CachePowersavingcontrol<strong>CPU</strong> coreI-ScratchpadMMUAHB busD-CacheBusinterfaceD-ScratchpadASIEWBASIE interfaceReference1. ARM Architecture Reference Manual, second edition

HEADQUARTERSHsinchu, Taiwan,Tel: 886-3-578-7888Fax: 886-3-578-7889twsales@faraday-tech.comUSA OFFICESunnyvale, USATel: 1-408-522-8888Fax: 1-408-522-8889ussales@faraday-tech.comEUROPE OFFICEHoofddorp, NetherlandsTel: 31-2356-20496Fax: 31-2356-36297eusales@faraday-tech.comJAPAN OFFICETokyo, JapanTel: 81-3-5214-0070Fax: 81-3-5214-0076jpsales@faraday-tech.comCHINA OFFICEShanghai, P. R. ChinaTel: 86-21-6406-7523Fax: 86-21-6406-5<strong>32</strong>7cnsales@faraday-tech.comCopyright <strong>Faraday</strong> <strong>Technology</strong>, 2006. All Rights Reserved. <strong>Faraday</strong> and <strong>Faraday</strong> Logo are trademarks of <strong>Faraday</strong><strong>Technology</strong> <strong>Corporation</strong>. Nothing in this document shall operate as license or is with express or implied warranty.The <strong>Faraday</strong> home page can be found at www.faraday-tech.com