Graduate Profiles 2012 - National University of Science and ...

Graduate Profiles 2012 - National University of Science and ...

Graduate Profiles 2012 - National University of Science and ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

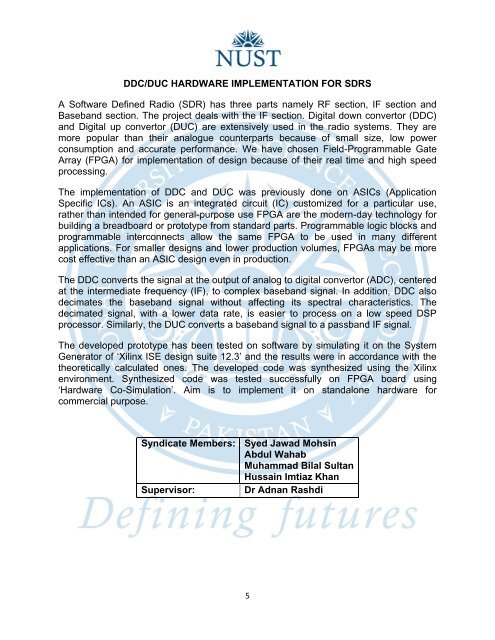

DDC/DUC HARDWARE IMPLEMENTATION FOR SDRSA S<strong>of</strong>tware Defined Radio (SDR) has three parts namely RF section, IF section <strong>and</strong>Baseb<strong>and</strong> section. The project deals with the IF section. Digital down convertor (DDC)<strong>and</strong> Digital up convertor (DUC) are extensively used in the radio systems. They aremore popular than their analogue counterparts because <strong>of</strong> small size, low powerconsumption <strong>and</strong> accurate performance. We have chosen Field-Programmable GateArray (FPGA) for implementation <strong>of</strong> design because <strong>of</strong> their real time <strong>and</strong> high speedprocessing.The implementation <strong>of</strong> DDC <strong>and</strong> DUC was previously done on ASICs (ApplicationSpecific ICs). An ASIC is an integrated circuit (IC) customized for a particular use,rather than intended for general-purpose use FPGA are the modern-day technology forbuilding a breadboard or prototype from st<strong>and</strong>ard parts. Programmable logic blocks <strong>and</strong>programmable interconnects allow the same FPGA to be used in many differentapplications. For smaller designs <strong>and</strong> lower production volumes, FPGAs may be morecost effective than an ASIC design even in production.The DDC converts the signal at the output <strong>of</strong> analog to digital convertor (ADC), centeredat the intermediate frequency (IF), to complex baseb<strong>and</strong> signal. In addition, DDC alsodecimates the baseb<strong>and</strong> signal without affecting its spectral characteristics. Thedecimated signal, with a lower data rate, is easier to process on a low speed DSPprocessor. Similarly, the DUC converts a baseb<strong>and</strong> signal to a passb<strong>and</strong> IF signal.The developed prototype has been tested on s<strong>of</strong>tware by simulating it on the SystemGenerator <strong>of</strong> ‗Xilinx ISE design suite 12.3‘ <strong>and</strong> the results were in accordance with thetheoretically calculated ones. The developed code was synthesized using the Xilinxenvironment. Synthesized code was tested successfully on FPGA board using‗Hardware Co-Simulation‘. Aim is to implement it on st<strong>and</strong>alone hardware forcommercial purpose.Syndicate Members: Syed Jawad MohsinAbdul WahabMuhammad Bilal SultanHussain Imtiaz KhanSupervisor:Dr Adnan Rashdi5