6-4Procesos_de_señales_electricas_con_amplificadores_operacionales-1

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

UTN REG. SANTA FE – ELECTRONICA I – ING. ELECTRICA I<br />

6-4-Apéndice 4: Procesos <strong>de</strong> <strong>señales</strong> eléctricas <strong>con</strong> <strong>amplificadores</strong> <strong>operacionales</strong><br />

--------------------------------------------------------------------------------------------------------<br />

Para el análisis <strong>de</strong>l circuito, <strong>con</strong>si<strong>de</strong>raremos al punto “s”, terminal inversor <strong>de</strong>l AO, una<br />

masa virtual dado que vi ≈ 0. Por tanto, la corriente entrante I1, estará <strong>de</strong>terminada por el<br />

voltaje <strong>de</strong> entrada V1.<br />

I1= v1/R<br />

Por otra parte por características <strong>de</strong>l AO, la corriente <strong>de</strong> entrada al terminal inversor es<br />

prácticamente nula (Ii≈0); Esto hace que la corriente <strong>de</strong> realimentación sea, por ley <strong>de</strong><br />

Kirchof, igual a la corriente entrante IR = I1.<br />

Como, vi ≈ 0 el voltaje <strong>de</strong> salida <strong>de</strong>l AO será la caída <strong>de</strong> voltaje en la resistencia <strong>de</strong><br />

realimentación Rr, siendo Vo = - Ir.Rr = - I1.Rr<br />

Sustituyendo las corriente entrante por las expresión <strong>de</strong>l voltaje que la genera,<br />

tendremos: vo = - (V1/R1).Rr = - V1.(Rr/R1)<br />

Como <strong>con</strong>clusión <strong>de</strong>l análisis <strong>de</strong> este circuito, tendremos:<br />

a) La corriente <strong>de</strong> realimentación Ir no <strong>de</strong>pen<strong>de</strong> <strong>de</strong> Rr sino <strong>de</strong> el voltaje entrante V1 y el<br />

resistor entrante R1.<br />

b) Como vi ≈ 0, el voltaje <strong>de</strong> salida <strong>de</strong>l circuito resulta prácticamente igual a la caida <strong>de</strong><br />

voltaje en el resistor Rr y por lo tanto su valor <strong>de</strong>pen<strong>de</strong>rá <strong>de</strong>l voltaje <strong>de</strong> entrada V1.<br />

c) La ganancia <strong>de</strong>l AO en circuito cerrado (realimentado) no <strong>de</strong>pen<strong>de</strong>ra <strong>de</strong> los<br />

elementos activos <strong>de</strong>l AO, sino <strong>de</strong> los resistores externos, dado que<br />

Avc ≡ Vo/V1 = - Rr/R1.<br />

d) El signo menos en la ecuación nos dice que el voltaje <strong>de</strong> salida Vo, tendrá polaridad<br />

opuesta al voltaje <strong>de</strong> entrada V1. para el caso <strong>de</strong> voltajes alternos, <strong>de</strong>cimos que el<br />

voltaje <strong>de</strong> salida esta <strong>de</strong>sfasado 180º respecto al voltaje <strong>de</strong> entrada.<br />

e) La corriente en la carga IL, estará <strong>de</strong>terminada solamente por el voltaje <strong>de</strong> salida Vo y<br />

RL y estará suministrada por el terminal <strong>de</strong> salida <strong>de</strong>l AO. De la misma forma , la<br />

corriente <strong>de</strong> realimentación Ir <strong>de</strong>berá ser suministrada (absorbida) por el AO. Por lo<br />

tanto la corriente total que <strong>de</strong>berá suministrar o absorber por el terminal <strong>de</strong> salida <strong>de</strong>l<br />

AO será Io = Ir + IL. El máximo valor <strong>de</strong> Io <strong>de</strong> los AO reales en circuito integrado<br />

oscila entre 5 y 10 mA aprox.<br />

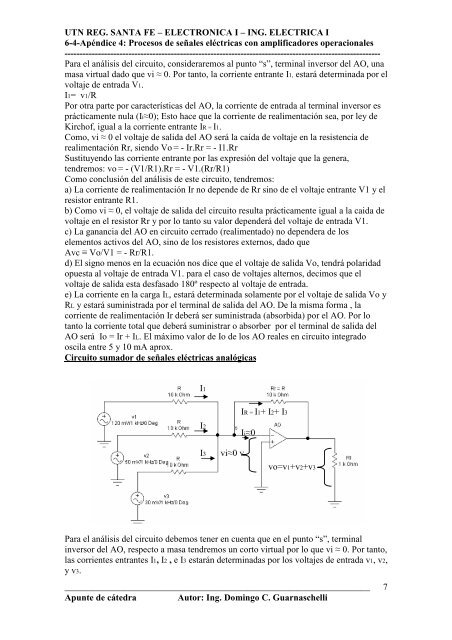

Circuito sumador <strong>de</strong> <strong>señales</strong> eléctricas analógicas<br />

I1<br />

IR = I1+ I2+ I3<br />

I2<br />

I3<br />

vi≈0 v<br />

Ii≈0<br />

vo=v1+v2+v3<br />

Para el análisis <strong>de</strong>l circuito <strong>de</strong>bemos tener en cuenta que en el punto “s”, terminal<br />

inversor <strong>de</strong>l AO, respecto a masa tendremos un corto virtual por lo que vi ≈ 0. Por tanto,<br />

las corrientes entrantes I1, I2 , e I3 estarán <strong>de</strong>terminadas por los voltajes <strong>de</strong> entrada v1, v2,<br />

y v3.<br />

___________________________________________________________________<br />

Apunte <strong>de</strong> cátedra Autor: Ing. Domingo C. Guarnaschelli<br />

7