You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

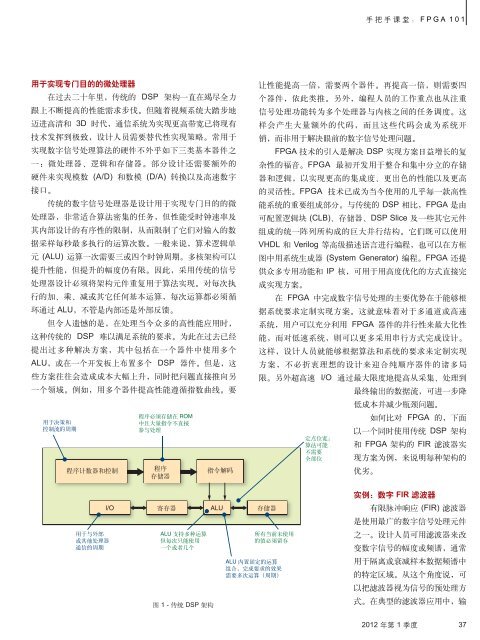

用于实现专门目的的微处理器<br />

在过去二十年里,传统的 DSP 架构一直在竭尽全力<br />

跟上不断提高的性能需求步伐。但随着视频系统大踏步地<br />

迈进高清和 3D 时代,通信系统为实现更高带宽已将现有<br />

技术发挥到极致,设计人员需要替代性实现策略。常用于<br />

实现数字信号处理算法的硬件不外乎如下三类基本器件之<br />

一:微处理器、逻辑和存储器。部分设计还需要额外的<br />

硬件来实现模数 (A/D) 和数模 (D/A) 转换以及高速数字<br />

接口。<br />

传统的数字信号处理器是设计用于实现专门目的的微<br />

处理器,非常适合算法密集的任务,但性能受时钟速率及<br />

其内部设计的有序性的限制,从而限制了它们对输入的数<br />

据采样每秒最多执行的运算次数。一般来说,算术逻辑单<br />

元 (ALU) 运算一次需要三或四个时钟周<strong>期</strong>。多核架构可以<br />

提升性能,但提升的幅度仍有限。因此,采用传统的信号<br />

处理器设计必须将架构元件重复用于算法实现。对每次执<br />

行的加、乘、减或其它任何基本运算,每次运算都必须循<br />

环通过 ALU,不管是内部还是外部反馈。<br />

但令人遗憾的是,在处理当今众多的高性能应用时,<br />

这种传统的 DSP 难以满足系统的要求。为此在过去已经<br />

提出过多种解决方案,其中包括在一个器件中使用多个<br />

ALU,或在一个开发板上布置多个 DSP 器件。但是,这<br />

些方案往往会造成成本大幅上升,同时把问题直接推向另<br />

一个领域。例如,用多个器件提高性能遵循指数曲线。要<br />

<br />

<br />

<br />

<br />

<br />

<br />

ROM<br />

<br />

<br />

<br />

<br />

ALU <br />

<br />

<br />

<br />

I/O ALU <br />

图 1 - 传统 DSP 架构<br />

让性能提高一倍,需要两个器件。再提高一倍,则需要四<br />

个器件,依此类推。另外,编程人员的工作重点也从注重<br />

信号处理功能转为多个处理器与内核之间的任务调度。这<br />

样会产生大量额外的代码,而且这些代码会成为系统开<br />

销,而非用于解决眼前的数字信号处理问题。<br />

FPGA 技术的引入是解决 DSP 实现方案日益增长的复<br />

杂性的福音。FPGA 最初开发用于整合和集中分立的存储<br />

器和逻辑,以实现更高的集成度、更出色的性能以及更高<br />

的灵活性。FPGA 技术已成为当今使用的几乎每一款高性<br />

能系统的重要组成部分。与传统的 DSP 相比,FPGA 是由<br />

可配置逻辑块 (CLB)、存储器、DSP Slice 及一些其它元件<br />

组成的统一阵列所构成的巨大并行结构。它们既可以使用<br />

VHDL 和 Verilog 等高级描述语言进行编程,也可以在方框<br />

图中用系统生成器 (System Generator) 编程。FPGA 还提<br />

供众多专用功能和 IP 核,可用于用高度优化的方式直接完<br />

成实现方案。<br />

手 把 手 课 堂 : F P G A 1 0 1<br />

在 FPGA 中完成数字信号处理的主要优势在于能够根<br />

据系统要求定制实现方案。这就意味着对于多通道或高速<br />

系统,用户可以充分利用 FPGA 器件的并行性来最大化性<br />

能,而对低速系统,则可以更多采用串行方式完成设计。<br />

这样,设计人员就能够根据算法和系统的要求来定制实现<br />

方案,不必折衷理想的设计来迎合纯顺序器件的诸多局<br />

限。另外超高速 I/O 通过最大限度地提高从采集、处理到<br />

<br />

<br />

ALU <br />

<br />

<br />

<br />

<br />

<br />

<br />

最终输出的数据流,可进一步降<br />

低成本并减少瓶颈问题。<br />

如何比对 FPGA 的,下面<br />

以一个同时使用传统 DSP 架构<br />

和 FPGA 架构的 FIR 滤波器实<br />

现方案为例,来说明每种架构的<br />

优劣。<br />

实例:数字 FIR 滤波器<br />

有限脉冲响应 (FIR) 滤波器<br />

是使用最广的数字信号处理元件<br />

之一。设计人员可用滤波器来改<br />

变数字信号的幅度或频谱,通常<br />

用于隔离或衰减样本数据频谱中<br />

的特定区域。从这个角度说,可<br />

以把滤波器视为信号的预处理方<br />

式。在典型的滤波器应用中,输<br />

2012 年第 1 季度 37