You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

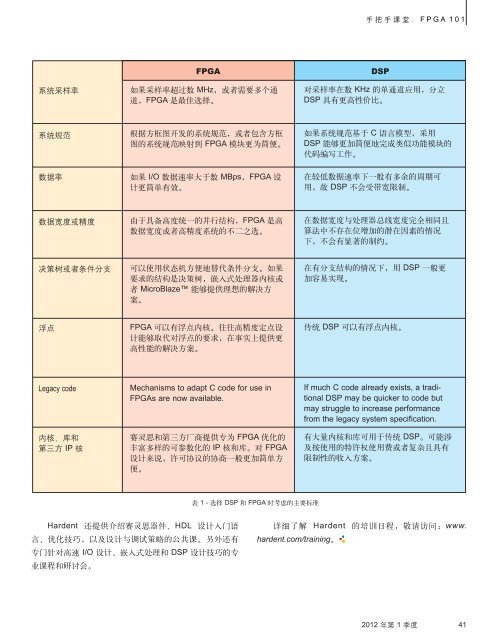

系统采样率 如果采样率超过数 MHz,或者需要多个通<br />

道,FPGA 是最佳选择。<br />

系统规范<br />

Hardent 还提供介绍赛灵思器件、HDL 设计入门语<br />

言、优化技巧,以及设计与调试策略的公共课。另外还有<br />

专门针对高速 I/O 设计、嵌入式处理和 DSP 设计技巧的专<br />

业课程和研讨会。<br />

根据方框图开发的系统规范,或者包含方框<br />

图的系统规范映射到 FPGA 模块更为简便。<br />

数据率 如果 I/O 数据速率大于数 MBps,FPGA 设<br />

计更简单有效。<br />

数据宽度或精度<br />

由于具备高度统一的并行结构,FPGA 是高<br />

数据宽度或者高精度系统的不二之选。<br />

决策树或者条件分支 可以使用状态机方便地替代条件分支。如果<br />

要求的结构是决策树,嵌入式处理器内核或<br />

者 MicroBlaze 能够提供理想的解决方<br />

案。<br />

浮点 FPGA 可以有浮点内核。往往高精度定点设<br />

计能够取代对浮点的要求,在事实上提供更<br />

高性能的解决方案。<br />

Legacy code Mechanisms to adapt C code for use in<br />

FPGAs are now available.<br />

内核、库和<br />

第三方 IP 核<br />

FPGA DSP<br />

赛灵思和第三方厂商提供专为 FPGA 优化的<br />

丰富多样的可参数化的 IP 核和库。对 FPGA<br />

设计来说,许可协议的协商一般更加简单方<br />

便。<br />

表 1 - 选择 DSP 和 FPGA 时考虑的主要标准<br />

手 把 手 课 堂 : F P G A 1 0 1<br />

详细了解 Hardent 的培训日程,敬请访问:www.<br />

hardent.com/training。<br />

对采样率在数 KHz 的单通道应用,分立<br />

DSP 具有更高性价比。<br />

如果系统规范基于 C 语言模型,采用<br />

DSP 能够更加简便地完成类似功能模块的<br />

代码编写工作。<br />

在较低数据速率下一般有多余的周<strong>期</strong>可<br />

用,故 DSP 不会受带宽限制。<br />

在数据宽度与处理器总线宽度完全相同且<br />

算法中不存在位增加的潜在因素的情况<br />

下,不会有显著的制约。<br />

在有分支结构的情况下,用 DSP 一般更<br />

加容易实现。<br />

传统 DSP 可以有浮点内核。<br />

If much C code already exists, a traditional<br />

DSP may be quicker to code but<br />

may struggle to increase performance<br />

from the legacy system specification.<br />

有大量内核和库可用于传统 DSP。可能涉<br />

及按使用的特许权使用费或者复杂且具有<br />

限制性的收入方案。<br />

2012 年第 1 季度 41