You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

手 把 手 课 堂 : F P G A 1 0 1<br />

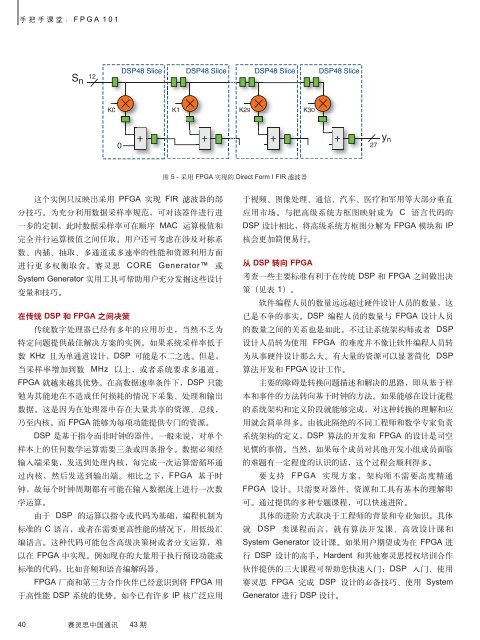

这个实例只反映出采用 PFGA 实现 FIR 滤波器的部<br />

分技巧。为充分利用数据采样率规范,可对该器件进行进<br />

一步的定制,此时数据采样率可在顺序 MAC 运算极值和<br />

完全并行运算极值之间任取。用户还可考虑在涉及对称系<br />

数、内插、抽取、多通道或多速率的性能和资源利用方面<br />

进行更多权衡取舍。赛灵思 CORE Generator 或<br />

System Generator 实用工具可帮助用户充分发掘这些设计<br />

变量和技巧。<br />

S n<br />

12<br />

K0<br />

0<br />

DSP48 Slice<br />

在传统 DSP 和 FPGA 之间决策<br />

传统数字处理器已经有多年的应用历史,当然不乏为<br />

特定问题提供最佳解决方案的实例。如果系统采样率低于<br />

数 KHz 且为单通道设计,DSP 可能是不二之选。但是,<br />

当采样率增加到数 MHz 以上,或者系统要求多通道,<br />

FPGA 就越来越具优势。在高数据速率条件下,DSP 只能<br />

勉为其能地在不造成任何损耗的情况下采集、处理和输出<br />

数据。这是因为在处理器中存在大量共享的资源、总线,<br />

乃至内核。而 FPGA 能够为每项功能提供专门的资源。<br />

DSP 是基于指令而非时钟的器件。一般来说,对单个<br />

样本上的任何数学运算需要三条或四条指令。数据必须经<br />

输入端采集,发送到处理内核,每完成一次运算需循环通<br />

过内核,然后发送到输出端。相比之下,FPGA 基于时<br />

钟,故每个时钟周<strong>期</strong>都有可能在输入数据流上进行一次数<br />

学运算。<br />

由于 DSP 的运算以指令或代码为基础,编程机制为<br />

标准的 C 语言,或者在需要更高性能的情况下,用低级汇<br />

编语言。这种代码可能包含高级决策树或者分支运算,难<br />

以在 FPGA 中实现。例如现存的大量用于执行预设功能或<br />

标准的代码,比如音频和语音编解码器。<br />

FPGA 厂商和第三方合作伙伴已经意识到将 FPGA 用<br />

于高性能 DSP 系统的优势。如今已有许多 IP 核广泛应用<br />

40 赛灵思中国通讯 43 <strong>期</strong><br />

K1<br />

DSP48 Slice<br />

K29<br />

DSP48 Slice<br />

图 5 - 采用 FPGA 实现的 Direct Form I FIR 滤波器<br />

K30<br />

DSP48 Slice<br />

于视频、图像处理、通信、汽车、医疗和军用等大部分垂直<br />

应用市场。与把高级系统方框图映射成为 C 语言代码的<br />

DSP 设计相比,将高级系统方框图分解为 FPGA 模块和 IP<br />

核会更加简便易行。<br />

从 DSP 转向 FPGA<br />

考查一些主要标准有利于在传统 DSP 和 FPGA 之间做出决<br />

策(见表 1)。<br />

软件编程人员的数量远远超过硬件设计人员的数量,这<br />

已是不争的事实。DSP 编程人员的数量与 FPGA 设计人员<br />

的数量之间的关系也是如此。不过让系统架构师或者 DSP<br />

设计人员转为使用 FPGA 的难度并不像让软件编程人员转<br />

为从事硬件设计那么大。有大量的资源可以显著简化 DSP<br />

算法开发和 FPGA 设计工作。<br />

主要的障碍是转换问题描述和解决的思路,即从基于样<br />

本和事件的方法转向基于时钟的方法。如果能够在设计流程<br />

的系统架构和定义阶段就能够完成,对这种转换的理解和应<br />

用就会简单得多。由彼此隔绝的不同工程师和数学专家负责<br />

系统架构的定义,DSP 算法的开发和 FPGA 的设计是司空<br />

见惯的事情。当然,如果每个成员对其他开发小组成员面临<br />

的难题有一定程度的认识的话,这个过程会顺利得多。<br />

要支持 FPGA 实现方案,架构师不需要高度精通<br />

FPGA 设计。只需要对器件、资源和工具有基本的理解即<br />

可。通过提供的多种专题课程,可以快速进阶。<br />

具体的进阶方式取决于工程师的背景和专业知识。具体<br />

就 DSP 类课程而言,就有算法开发课、高效设计课和<br />

System Generator 设计课。如果用户<strong>期</strong>望成为在 FPGA 进<br />

行 DSP 设计的高手,Hardent 和其他赛灵思授权培训合作<br />

伙伴提供的三大课程可帮助您快速入门:DSP 入门、使用<br />

赛灵思 FPGA 完成 DSP 设计的必备技巧、使用 System<br />

Generator 进行 DSP 设计。<br />

27<br />

yn