You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

封 面 文 章<br />

以及综合全面的技术文档,以便用户<br />

立即着手工作。实例设计和演示包括<br />

开发板诊断演示、ChipScope Pro<br />

串行 I/O 工具套件、IBERT 收发器测<br />

试 设 计 、 多 重 启 动 参 考 设 计 、 P C I<br />

Express Gen 2 (x8) 测试设计和<br />

DDR3 存储器接口设计。<br />

在技术文档方面,本套件包括入<br />

门指南、硬件用户指南、参考设计和<br />

实例设计指南。另外还附送原理图和<br />

UCF 文件,以提供根据最佳实践加速<br />

开发板布局和开发进程的必要信息。<br />

如欲了解关于该板件的更多详情,<br />

比如器件配置、时钟设置、控制和电<br />

源,敬请访问 http://www.xilinx.com/cn/<br />

vc707 上的 Virtex-7 FPGA VC707 评估<br />

套件目标设计平台套件页面。<br />

Kintex-7 FPGA KC705 评估套件<br />

采用 XC7K325T-FF900 FPGA 的<br />

Kintex-7 FPGA KC705 评估套件是<br />

Kintex-7 系列的基础目标设计平台。<br />

Moran 指出,该套件旨在实现最高灵<br />

活性,以帮助设计人员加速无线电/基<br />

带、雷达、边缘 QAM、三速率 SDI 以<br />

及其它要求高能效高速通信和处理等<br />

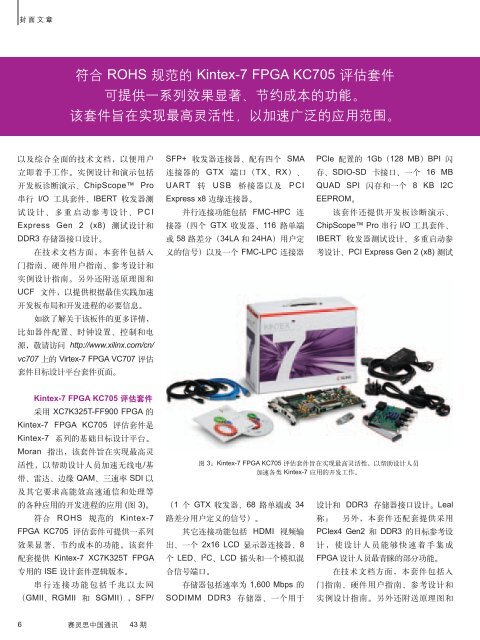

的各种应用的开发进程的应用 (图 3)。<br />

符合 ROHS 规范的 Kintex-7<br />

FPGA KC705 评估套件可提供一系列<br />

效果显著、节约成本的功能。该套件<br />

配套提供 Kintex-7 XC7K325T FPGA<br />

专用的 ISE 设计套件逻辑版本。<br />

符合 ROHS 规范的 Kintex-7 FPGA KC705 评估套件<br />

串 行 连 接 功 能 包 括 千 兆 以 太 网<br />

(GMII、RGMII 和 SGMII),SFP/<br />

可提供一系列效果显著、节约成本的功能。<br />

该套件旨在实现最高灵活性,以加速广泛的应用范围。<br />

6 赛灵思中国通讯 43 <strong>期</strong><br />

SFP+ 收发器连接器、配有四个 SMA<br />

连接器的 GTX 端口(TX、RX)、<br />

UART 转 USB 桥接器以及 PCI<br />

Express x8 边缘连接器。<br />

并行连接功能包括 FMC-HPC 连<br />

接器(四个 GTX 收发器、116 路单端<br />

或 58 路差分(34LA 和 24HA)用户定<br />

义的信号)以及一个 FMC-LPC 连接器<br />

(1 个 GTX 收发器、68 路单端或 34<br />

路差分用户定义的信号)。<br />

其它连接功能包括 HDMI 视频输<br />

出、一个 2x16 LCD 显示器连接器、8<br />

个 LED、I 2 C、LCD 插头和一个模拟混<br />

合信号端口。<br />

存储器包括速率为 1,600 Mbps 的<br />

SODIMM DDR3 存储器、一个用于<br />

PCIe 配置的 1Gb(128 MB)BPI 闪<br />

存、SDIO-SD 卡接口、一个 16 MB<br />

QUAD SPI 闪存和一个 8 KB I2C<br />

EEPROM。<br />

该套件还提供开发板诊断演示、<br />

ChipScope Pro 串行 I/O 工具套件、<br />

IBERT 收发器测试设计、多重启动参<br />

考设计、PCI Express Gen 2 (x8) 测试<br />

图 3:Kintex-7 FPGA KC705 评估套件旨在实现最高灵活性,以帮助设计人员<br />

加速各类 Kintex-7 应用的开发工作。<br />

设计和 DDR3 存储器接口设计。Leal<br />

称:“另外,本套件还配套提供采用<br />

PCIex4 Gen2 和 DDR3 的目标参考设<br />

计 , 使 设 计 人 员 能 够 快 速 着 手 集 成<br />

FPGA 设计人员最青睐的部分功能。”<br />

在技术文档方面,本套件包括入<br />

门指南、硬件用户指南、参考设计和<br />

实例设计指南。另外还附送原理图和