i Ä°ÃÄ°NDEKÄ°LER Sayfa Ä°ÃÄ°NDEKÄ°LER ...

i Ä°ÃÄ°NDEKÄ°LER Sayfa Ä°ÃÄ°NDEKÄ°LER ...

i Ä°ÃÄ°NDEKÄ°LER Sayfa Ä°ÃÄ°NDEKÄ°LER ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

8<br />

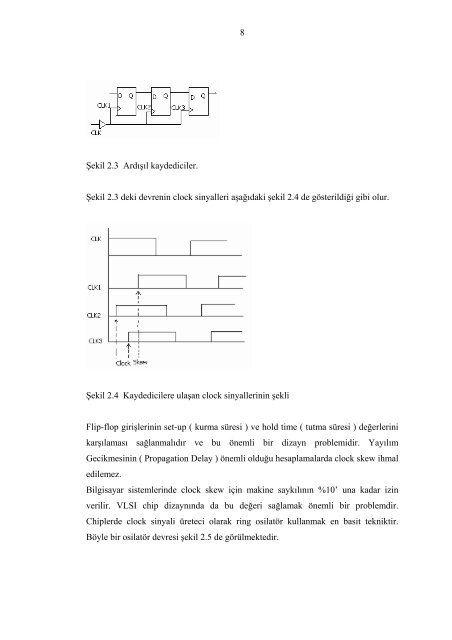

Şekil 2.3 Ardışıl kaydediciler.<br />

Şekil 2.3 deki devrenin clock sinyalleri aşağıdaki şekil 2.4 de gösterildiği gibi olur.<br />

Şekil 2.4 Kaydedicilere ulaşan clock sinyallerinin şekli<br />

Flip-flop girişlerinin set-up ( kurma süresi ) ve hold time ( tutma süresi ) değerlerini<br />

karşılaması sağlanmalıdır ve bu önemli bir dizayn problemidir. Yayılım<br />

Gecikmesinin ( Propagation Delay ) önemli olduğu hesaplamalarda clock skew ihmal<br />

edilemez.<br />

Bilgisayar sistemlerinde clock skew için makine saykılının %10’ una kadar izin<br />

verilir. VLSI chip dizaynında da bu değeri sağlamak önemli bir problemdir.<br />

Chiplerde clock sinyali üreteci olarak ring osilatör kullanmak en basit tekniktir.<br />

Böyle bir osilatör devresi şekil 2.5 de görülmektedir.