i Ä°ÃÄ°NDEKÄ°LER Sayfa Ä°ÃÄ°NDEKÄ°LER ...

i Ä°ÃÄ°NDEKÄ°LER Sayfa Ä°ÃÄ°NDEKÄ°LER ...

i Ä°ÃÄ°NDEKÄ°LER Sayfa Ä°ÃÄ°NDEKÄ°LER ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

i<br />

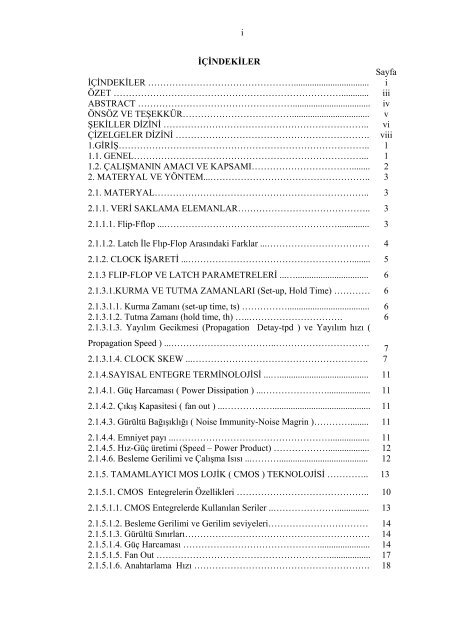

İÇİNDEKİLER<br />

<strong>Sayfa</strong><br />

İÇİNDEKİLER …………………………………………................................. i<br />

ÖZET …………………………………………………………………............ iii<br />

ABSTRACT …………………………………………….................................. iv<br />

ÖNSÖZ VE TEŞEKKÜR……………………………….................................. v<br />

ŞEKİLLER DİZİNİ ………………………………………………………….. vi<br />

ÇİZELGELER DİZİNİ ………………………………………………………. viii<br />

1.GİRİŞ……………………………………………………………………….. 1<br />

1.1. GENEL…………………………………………………………………... 1<br />

1.2. ÇALIŞMANIN AMACI VE KAPSAMI……………………………........ 2<br />

2. MATERYAL VE YÖNTEM...…………………………………………….. 3<br />

2.1. MATERYAL…………………………………………………………….. 3<br />

2.1.1. VERİ SAKLAMA ELEMANLAR…………………………………….. 3<br />

2.1.1.1. Flip-Fflop ...………………………………………………….............. 3<br />

2.1.1.2. Latch İle Flıp-Flop Arasındaki Farklar ...……………………………. 4<br />

2.1.2. CLOCK İŞARETİ ...………………………………………………........ 5<br />

2.1.3 FLIP-FLOP VE LATCH PARAMETRELERİ ...…................................ 6<br />

2.1.3.1.KURMA VE TUTMA ZAMANLARI (Set-up, Hold Time) ………… 6<br />

2.1.3.1.1. Kurma Zamanı (set-up time, ts) …………….................................... 6<br />

2.1.3.1.2. Tutma Zamanı (hold time, th) …..…………………………. 6<br />

2.1.3.1.3. Yayılım Gecikmesi (Propagation Detay-tpd ) ve Yayılım hızı (<br />

Propagation Speed ) ...……………………………..………………………….<br />

7<br />

2.1.3.1.4. CLOCK SKEW ...…………………………………………………. 7<br />

2.1.4.SAYISAL ENTEGRE TERMİNOLOJİSİ ...…....................................... 11<br />

2.1.4.1. Güç Harcaması ( Power Dissipation ) ...…………………................... 11<br />

2.1.4.2. Çıkış Kapasitesi ( fan out ) ...………….…........................................... 11<br />

2.1.4.3. Gürültü Bağışıklığı ( Noise Immunity-Noise Magrin )…………........ 11<br />

2.1.4.4. Emniyet payı ...……………………………………………................. 11<br />

2.1.4.5. Hız-Güç üretimi (Speed – Power Product) ……………….................. 12<br />

2.1.4.6. Besleme Gerilimi ve Çalışma Isısı ...………....................................... 12<br />

2.1.5. TAMAMLAYICI MOS LOJİK ( CMOS ) TEKNOLOJİSİ ………….. 13<br />

2.1.5.1. CMOS Entegrelerin Özellikleri …………………………………….. 10<br />

2.1.5.1.1. CMOS Entegrelerde Kullanılan Seriler ..………………….............. 13<br />

2.1.5.1.2. Besleme Gerilimi ve Gerilim seviyeleri…………………………… 14<br />

2.1.5.1.3. Gürültü Sınırları……………………………………………………. 14<br />

2.1.5.1.4. Güç Harcaması ………………………………………...................... 14<br />

2.1.5.1.5. Fan Out ………………………………………………….................. 17<br />

2.1.5.1.6. Anahtarlama Hızı …………………………………………………. 18

ii<br />

2.1.6. LATCH ………………………………………....................................... 19<br />

2.1.6.1. İki Kararlı Elemanların Elektriksel Davranışları ...………………….. 19<br />

2.1.6.2. S – R LATCH ……………………………………………………….. 25<br />

2.1.7. STATİK LATCH DEVRESİNİN ………………………….................. 30<br />

2.1.7.1. Makromodelin Yapısı …………………………………….................. 30<br />

2.1.7.2. S/R Latch Similasyonu ……………………………………………… 42<br />

2.2. YÖNTEM………………………………………………………………...<br />

2.2.1. BULANIK MANTIK ………………………………………………….. 46<br />

2.2.2. KLASİK VE BULANIK KÜMELER ………………………………… 47<br />

2.2.3. Üyelik Fonksiyonları …………………………...................................... 48<br />

2.2.4. Üyelik Fonksiyonlarının Kısımları …………………………................. 49<br />

2.2.5. BULANIK DENETİM SİSTEMİ ……………....................................... 51<br />

2.2.5.1. Bulanıklaştırma ……………………………………………………… 52<br />

2.2.5.2. BULANIK ÇIKARIM (BULANIK KURALLAR)…………............. 52<br />

2.2.5.3. DURULAŞTIRMA ………………………………………….............. 52<br />

3. ARAŞTIRMA VE BULGULAR………………………………………….. 55<br />

3.1. Yük ve Kaynak Gerilimine Bağlı Olarak Yayılım Gecikmesinin<br />

Bulunması ……………………………….........................................................<br />

55<br />

3.2. Giriş ve Çıkış Değerlerine Bağlı Olarak Transistor Boyutunun<br />

Bulunması …………………………………………………………………….<br />

60<br />

4. SONUÇ VE DEĞERLENDİRME…………………………………………. 81<br />

4.1. Değerlerin Fuzzy Logicte İşlenmesi …………………………….............. 81<br />

KAYNAKLAR …………………………………………................................. 87<br />

EK-1…………………………………………………………………………... 88<br />

ÖZGEÇMİŞ …………………………………………….................................. 90

iii<br />

ÖZET<br />

BULANIK MANTIL İLE LATCH OPTİMİZASYONU<br />

Bu çalışmada veri saklama elemanları olan latchler ve genel parametreleri<br />

araştırılmıştır. Latch devrelerinin temel yapılarından olan SR Latch devresi<br />

üzerinde latchlerin çalışması incelenmiş ve PSPICE yazılımında simülasyonları<br />

yapılmıştır.<br />

Temel bir Latch devresinin girişine ve çıkışına birer tane invertör bağlanarak,<br />

invertörlerin boyutlarının değişmesi durumunda latch’de kullanılan invertörlerin<br />

boyutlarının değişimi ve çıkışta meydana gelen zaman gecikmeleri incelenmiştir.<br />

Çalışma sonucunda, latchlerin boyutlarının belirlenebilmesi için Fuzzy Logic ile<br />

modeller oluşturulmuştur. Oluşturulan modeller sayesinde PSPICE’ da similasyon<br />

yapmaya gerek kalmadan, Latch’ de kullanılması gereken ideal invertörlerin<br />

boyutları belirlenmeye çalışılmıştır.<br />

Ayrıca devre tasarımı yapılırken dikkat edilmesi gereken bazı parametreler bu<br />

çalışmada incelenmiştir. İncelenen parametreler set-up hold time, clock skew, W/L<br />

ve güç harcamasıdır.<br />

Anahtar Kelimeler : Latch, Flip-flop, W/L değerleri

iv<br />

ABSTRACT<br />

LATCH OPTIMIZATION WITH FUZZY LOGIC<br />

The latches as a data storage element and their common parameters were researched<br />

in this study. Performance of the latches was examined over the SR Latch circuit<br />

which is one of the fundamental components of Latch circuits. Additionally, the<br />

results were simulated by using PSPICE software.<br />

The time detentions at the exit and the dimensional changes of the latch inverters<br />

caused by the change of the inverters dimensions were searched by attaching dual<br />

inverter at the beginning and the end of a basic Latch circuit.<br />

At the end of the study, sample models were formed for the determination of the<br />

dimensions of the latches by using fuzzy logic approach. Finally, these models were<br />

used to determine the dimensions of the ideal inverters without doing simulations by<br />

using PSPICE software. Moreover some parameters such as; set-up hold time, clock<br />

skew, W/L and power expenses that should be considered while designing a circuit<br />

were examined in this study.<br />

Keywords: Latch, Flip-flop, W/L values

v<br />

ÖNSÖZ VE TEŞEKKÜR<br />

Çalışmam sırasında OrCad PSPICE ve MATLAB Fuzzy Logic programları<br />

kullanılmıştır. Bu programlar hemen her bilgisayarda çalışabildiklerinden<br />

çalışmaların yapılabilmesi için donanımsal açıdan bir sorun yaşanmamıştır. Ancak<br />

yapmış olduğum çalışmanın devre şekillerinin temini ve konu anlatımlarının<br />

Türkiye’deki üniversitelerin kütüphanelerinde bulunamaması nedeniyle bazı sorunlar<br />

yaşanmıştır.<br />

TEŞEKKÜR<br />

Yrd.Doç.Dr. Ali MANZAK ( Tez Danışmanı ), çalışmanın sonuca ulaştırılmasında<br />

ve karşılaşılan güçlüklerin aşılmasında yön gösterici olmuştur.<br />

Öğr.Gör. Mehmet ALBAYRAK, tezin baskıya hazırlanmasında ve çevirilerde<br />

katkıları olmuştur.

vi<br />

ŞEKİLLER DİZİNİ<br />

<strong>Sayfa</strong><br />

Şekil 2.1. FF Kontrol Girişleri İçin Kurma-Tutma Zamanları ………….. 6<br />

Şekil 2.2. Lojik Entegrelerde Meydana Gelen Yayılım Gecikmesi …….. 7<br />

Şekil 2.3. Ardışıl Kaydediciler…….. ........................................................ 8<br />

Şekil 2.4. Kaydedicilere Ulaşan Clock Sinyallerinin Şekli……………… 8<br />

Şekil 2.5. Ring Osilatörü Kullanılarak Yapılmış Basit bir Clock Üreteci.. 9<br />

Şekil 2.6. Kristal Osilatör Devresi ………………………………………. 9<br />

Şekil 2.7. H Ağaç Yapısı ………………………………………………... 10<br />

Şekil 2.8 Dijital Entegrelerde Gürültü Emniyet Payının Tespiti ……….. 12<br />

Şekil 2.9. Dinamik Güç Harcaması Analizi İçin CMOS İnverter .……… 15<br />

Şekil 2.10. CMOS invertörün anahtarlaması süresince, giriş ve çıkış<br />

gerilim dalga şekilleri ile kondansatör akımının dalga şeklileri 16<br />

Şekil 2.11. CMOS bağlı yüklerin kapasite etkisi oluşturması ……………. 17<br />

Şekil 2.12. a) İki Kararlı Devrelerin Basit Blok diyagramı<br />

b) Gerilim Transfer Eğrisi ………..................................... 20<br />

Şekil 2.13. Statik Latch Devre Şekli ……………………………………... 20<br />

Şekil 2.14. Gerilim Değişim Eğrisi ………………..................................... 21<br />

Şekil 2.15. Kaskad Bağlı İki İnverter …………………………………….. 21<br />

Sekil 2.16. İki kararlı Devrelerin Davranışını Temsil Eden Faz Aralığı …. 24<br />

Şekil 2.17.<br />

Kurma Süresince İki İnvertörden Oluşan Döngüdeki Geçici<br />

Durum Sinyalinin Yayılım Gecikmesi ……………………….. 24<br />

Şekil 2.18. S-R Latch Devre Şekli ………………………………………... 26<br />

Şekil 2.19. Giriş ve Çıkış Dalga Şekilleri ………………………………… 28<br />

Şekil 2.20. NAND-Tipi CMOS Statik Latch Devre Şekli ………………... 31<br />

Şekil 2.21.<br />

NAND-Tipi CMOS Statik Latch Devresinin Karakteristik<br />

Dalga Şekli …………………………………………………… 32<br />

Şekil 2.22. Devrede kullanılan MOSFET'lerin İşlem Bölgeleri …………. 33<br />

Şekil 2.23. MOSFET’in Büyük İşaret Eşdeğer Devresi ………………….. 34<br />

Şekil 2.24. a) Yükselme Zamanı<br />

b) Düşme Zamanı ………………………………………… 35<br />

Şekil 2.25. Yükselme ve Düşme Zamanlarındaki Kapasite ve İletkenlik<br />

Faktörleri………………………………………………………. 36<br />

Şekil 2.26. Mosfetin Drain Akımının Denklemleri………………………... 39<br />

Şekil 2.27. S-R Latch Devre Şekli ………………………………………… 42<br />

Şekil 2.28. S-R Latch Devresinin Giriş ve Çıkış Sinyalleri ………………. 43<br />

Şekil 2.29. Kapasitif Yüke Bağlı Olarak Yayılım Gecikmesinin Değişimi.. 44<br />

Şekil 2.30. Kapasitif Yüke Bağlı Olarak Düşme Zamanı Gecikmesinin<br />

Değişimi ………………………………………………………. 44<br />

Şekil 2.31. Kapasitif Yüke Bağlı Olarak Yükselme Zamanı Gecikmesinin<br />

Değişimi ………………………………………………………. 45<br />

Şekil 2.32. Kaynak Gerilimine Bağlı Olarak Yayılım Gecikmesinin<br />

Değişimi ………………………………………………………. 45<br />

Şekil 2.33. Bulanık Küme …………………………………………………. 48<br />

Şekil 2.34. Üyelik Fonksiyonu ……………………………………………. 49<br />

Şekil 2.35. Üyelik Derecelerinin Gösterimi ……………………………….. 50<br />

Şekil 2.36. Bulanık Kümeler<br />

(a) Dış Bükey<br />

(b) Dış Bükey Olmayan …………………………………… 51

vii<br />

<strong>Sayfa</strong><br />

Şekil 2.37. Bulanık Denetleyicinin Genel Yapısı ......................................... 52<br />

Şekil 2.38. Sinirsel Bulanık Kontrol Sisteminin İşlem Adımları …………. 54<br />

Şekil 3.1. Fuzzy Logic Fis Editörü ………………………………………. 55<br />

Şekil 3.2. Kapasitif Yüke Ait Üyelik Fonksiyonu ……………………….. 56<br />

Şekil 3.3. Kaynak Gerilimine Ait Üyelik Fonksiyonu …………………… 56<br />

Şekil 3.4. Yayılım Gecikmesine Ait Üyelik Fonksiyonu ………………... 57<br />

Şekil 3.5. Kurallar ………………………………....................................... 57<br />

Şekil 3.6. Giriş Değişkenlerine Göre Çıkış Değerinin Değişimi ………… 58<br />

Şekil 3.7.<br />

Giriş Değişkenlerine Bağlı Olarak Çıkışın Üç Boyutlu<br />

Değişimi………………………………………………………… 58<br />

Şekil 3.8. Latch ve Sürme Devresinin Blok Diyagramı ………………….. 60<br />

Şekil 3.9. Latch ve Sürme Devresinin Açık Şekli ....................................... 60<br />

Şekil 3.10. Giriş, Çıkış ve Clock Sinyalleri ………………………………... 62<br />

Şekil 4.1. Fuzzy Logic Fis Editörü ……………………………………….. 81<br />

Şekil 4.2. Yük İnvertörünün Üyelik Fonksiyonu …………………………. 82<br />

Şekil 4.3. Kurallar ………………………………........................................ 83<br />

Şekil 4.4. Giriş Değişkenlerine Göre Çıkış Değerinin Değişimi …………. 84<br />

Şekil 4.5.<br />

Giriş Değişkenlerine Bağlı Olarak Gecikmenin Üç Boyutlu<br />

Değişimi ……………………………………………………….. 85<br />

Şekil 4.6 Girişe Bağlı Olarak 1.İnvertör Boyutunun Üç Boyutlu Değişimi 85<br />

Şekil 4.7. Girişe Bağlı Olarak 2.İnvertör Boyutunun Üç Boyutlu Değişimi 86

viii<br />

ÇİZELGELER DİZİNİ<br />

<strong>Sayfa</strong><br />

Çizelge 2.1. S-R Latch Devresinin Doğruluk Tablosu…………………... 26<br />

Çizelge 2.2. PMOS Transistorların İşlem Modları ……………………… 27<br />

Çizelge 2.3 Farklı İşlem Bölgelerindeki Gate Kapasitesi ………………. 34<br />

Çizelge 2.4. Yüke Bağlı Olarak 1. İnvertörün Boyutları ………………... 72<br />

Çizelge 2.5. Yük ve 1. İnvertöre bağlı olarak 2. İnvertörün Boyutları …. 73<br />

Çizelge 2.6.<br />

Yük İnvertörünün Değişimine Bağlı Olarak 1. ve 2. İnvertör<br />

Boyutları ve Gecikme Zamanının Değişimi ………………. 79<br />

Çizelge 2.7. Giriş İnvertörünün Değişimine Bağlı Olarak 1. ve 2.<br />

İnvertör Boyutları ve Gecikme Zamanının Değişimi ……… 79

1<br />

1. GİRİŞ<br />

1.1. GENEL<br />

Elektronikte veri saklama elemanı olarak birçok yapı kullanılmaktadır. Veri saklama<br />

elemanlarından bazıları latch, flip-flop, Sram, Ddram dir. Çağdaş sayısal elektronikte<br />

temel hafıza elemanı olarak flip-flop denilen elemanlar kullanılmaktadır ( Ekiz, H.,<br />

2003 ). İkili bilgilerin flip-floplara farklı şekilde uygulanması sonucu, flip-flop<br />

çeşitleri oluşmaktadır. Flip-floplar giriş sinyaline veya zamanlayıcı ( clock ) olarak<br />

kullanılan sinyalin durumuna göre tepki gösterirler. Zamanlayıcı olarak kullanılan<br />

sinyale senkronlayıcı darbe denilmektedir. Senkronlayıcı darbenin hangi durumuna<br />

tepki gösterdiğine bağlı olarak flip-floplar iki gruba ayrılırlar. Darbenin yalnız kararlı<br />

durumuna tepki gösteren flip-floplara LATCH ( Kilit ) denir.<br />

Latchler genellikle dijital devrelerde sinyal depolama ve sinyal geciktirme elemanı<br />

olarak kullanılmaktadırlar ( Dejhan, K., vd., 2000 ). Letchler temel olarak birbirine<br />

kaskad bağlı iki adet invertörden ( çevirici ) oluşmaktadır.<br />

Statik ardışıl devrelerin temel yapısını S/R latchler oluşturmaktadır. S/R latchler<br />

genellikle kaskad bağlı iki adet NOR Gates ya da NAND Gates den oluşmaktadır. Bu<br />

her iki tip S/R latchde de pozitif geri besleme kullanılmaktadır ( Wu, C.Y., 1988 ).<br />

Kullanılan bu pozitif geri beslemeden ötürü latchler PSPICE similasyonlarında fazla<br />

işlem zamanı gerektirmektedirler.<br />

Latchler diğer hafıza elemanları ile karşılaştırıldıklarında; daha fazla güç harcadıkları<br />

ve daha fazla yer kapladıkları görülmektedir. Ayrıca latchlerde yarı kararlı ( metastable<br />

) durumlar oluşmaktadır. Yani giriş sinyallerinin durumuna göre, çıkış sinyali<br />

kararsız bir durum göstermektedir ( Dejhan, K., vd., 2000 ).<br />

Dijital devrelerde clock sinyalinin yükselme ve düşme zamanı minimum olmalı ve<br />

gecikmesi sıfır olmalıdır. Gerçek uygulamalarda ise gecikme sıfır olmamaktadır. Bir<br />

dijital devrede clock sinyalinin devre elemanı olan chiplere ulaşmasındaki zaman<br />

farklılığına clock skew denilmektedir ( Nedovic, N., vd., 2003 )

2<br />

1.2. ÇALIŞMANIN AMACI VE KAPSAMI<br />

Dijital uygulamalarda latchler için birçok modelleme yapılmıştır. Bunlardan bir<br />

kısmı; en küçük boyutta, en az güç harcamasını sağlamak ve hızı en yüksek seviyeye<br />

çıkarmaktır. Bir kısmının amacıda; clcok skew ve yarı kararlı durumları ortadan<br />

kaldırmaktır. Clock sinyalindeki gecikmeyi azaltmak için; ring osilatörler, kristal<br />

osilatörler, H ağaç yapısı gibi yöntemler geliştirilmiştir ( Yoshizava, H., 1998 ).<br />

En küçük transistor boyutu ile en az güç harcamasını ve en hızlı latchi tasarlamak<br />

için de, latchlerin çıkışına kondansatör bağlayarak yük oluşturulmuş ve zaman<br />

gecikmeleri ile güç harcamaları ölçülmüştür. Bu similasyonlardan alınan değerlere<br />

göre en ideal durumu bulabilmek için algoritmalar oluşturulmuştur.<br />

Bu çalışmada latchin çıkışına kondansatöre göre daha gerçekçi olan MOSFET’<br />

lerden oluşan invertör bağlanmıştır. Bağlanan bu invertördeki MOSFET’ lerin<br />

boyutları değiştirilerek çıkış kapasitesi arttırılıp azaltılmıştır. Çıkış kapasitesinin<br />

değişimine göre zaman gecikmeleri ölçülmüştür. Bulunan zaman gecikmelerini en<br />

aza indirebilmek için latch’in girişinde kullanılan invertörün ve latch’ de kullanılan<br />

invertörlerin boyutları değiştirilerek yüzlerce similasyon yapılmıştır.<br />

Sonuç olarak bu çalışmada; similasyonlardan elde edilen en ideal zaman gecikmesine<br />

ait transistör boyutlarını, yüzlerce similasyon yapmadan bulduran bir algoritma<br />

yazılması amaçlanmıştır. Bu doğrultuda MATLAB Programının FUZZY<br />

TOOLBOX’ ında ( Bulanık Mantık ) giriş ve yük invertörlerinin boyutlarına göre en<br />

ideal latch boyutunu ve zaman gecikmesini bulduran bir program oluşturulmuştur.

3<br />

2. MATERYAL VE YÖNTEM<br />

2.1. MATERYAL<br />

2.1.1. VERİ SAKLAMA ELEMANLARI<br />

2.1.1.1. Flip-Fflop<br />

Çağdaş sayısal elektronikte temel hafızalı devre elemanı olarak FLİP – FLOP denilen<br />

elemanlar kullanılmaktadır. Flip-flop ların değişik şekilleri vardır. Bu çeşitlerin tümü<br />

aşağıdaki ortak özelliklere sahiptir (Ekiz, H., 2003 ).<br />

• Bir flip-flopun iki çıkışı vardır. Q ve Q’<br />

• Kararlı bir flip-flop da Q’ çıkışının lojik durumu Q çıkışının lojik durumunun<br />

tam tersidir. Kararlı bir flip-flopta QQ’=00 ve QQ’=11 durumları olmaz. Bu<br />

durumlar yalnız flip-flopun bir kararlı durumdan diğer kararlı duruma geçişi<br />

sırasında ve hissedilmez kadar kısa sürede meydana çıkar ve kayıp olurlar.<br />

• Q=1 ve Q’=0 durumu flip-flopun lojik 1 durumu olarak, Q=0 ve Q’=1<br />

durumu ise flip flopun lojik 0 durumu olarak kabul edilmiştir.<br />

• Flip flopa giriş sinyali uygulanmadığı sürece flip flop mevcut durumunu<br />

korumaya devam eder. Yani bir bit hafıza elemanı görevini sürdürür.<br />

• Değişik çeşit flip floplar görevine göre değil, yalnız giriş sinyallerinin<br />

sayısına ve bu sinyallere verilecek olan tepkilere göre farklılaşırlar.<br />

İkili bilgilerin flip-flopa farklı şekilde uygulanması sonucu, flip-flop çeşitleri oluşur.<br />

Diğer bir değişle; temel flip-flop devresinin bağlantısının değiştirilmesi ve yeni<br />

özellikler eklenmesi ile oluşturulan değişik flip flop çeşitleri bulunmaktadır.<br />

Bunlardan en çok kullanılanlar:<br />

1. R – S (Reset-Set) tipi FF<br />

2. Tetiklemeli (clocked) R-S FF<br />

3. J – K tipi FF

4<br />

4. Ana – Uydu (Master – Slave) tipi FF<br />

5. D (Data) tipi FF<br />

Ayrıca flip-floplar Asenkron veya Senkron olarak ikiye de ayrılır. Asenkron giriş<br />

sinyallerinin hiçbir şarta bağlı olamadan istenilen anda uygulanabileceği ve<br />

uygulandığı anda etkili olabileceği anlamını taşır. Asenkron flip-floplardan farklı<br />

olarak senkron flip-floplar esas giriş sinyallerine ( R, S, D , J, K ) bu sinyallerin<br />

durum değiştirdiği anlarda değil Senkronlayıcı ( zamanlayıcı ) olarak kullanılan CLK<br />

veya diğer bir sinyalin sabitliği veya ani olarak durum değiştirmesi sırasında tepki<br />

gösterirler.<br />

Senkronlayıcı darbenin hangi elemanına ( seviyesi, yükselişi, düşüşü ) tepki<br />

gösterdiğine bağlı olarak flip-floplar iki sınıfa ayrılır. Darbenin yalnız kararlı<br />

durumuna tepki veren flip-floplara KİLİT ( LATCH ) denir. Darbenin ani olarak<br />

yükselişine veya düşüşüne tepki veren flip-floplara ise TETİKLENEN (<br />

TRIGGERLER ) denir (Ekiz, H., 2003 ).<br />

2.1.1.2. Latch İle Flıp-Flop Arasındaki Farklar<br />

• Latch flip-floplar iki şekilde dizayn edilebilirler. Bunlardan birincisinde clock<br />

sinyali kullanılmaz. Giriş sinyallerinin ( R, S, J, K, D ) durum değişikliğine<br />

göre tepki verirler. İkinci yapıda clock sinyali kullanılır. Fakat bu yapıdaki<br />

latch flip-floplar; esas giriş sinyallerine bu sinyallerin durum değiştirdiği<br />

anlarda değil senkronlayıcı olarak kullanılan clock veya diğer bir sinyalin<br />

varlığı ve sabitliği sırasında tepki gösterirler.bunu sağlamak için esas sinyal<br />

kaynakları asenkron R-S flip-flopun girişlerine direkt olarak değil, bir girişi<br />

senkronlayıcı sinyal kaynağına ( C ) bağlanmış olan VE kapıları veya<br />

VEDEĞİL kapıları üzerinden bağlanır.<br />

• Latch tipi devrelerde girişler etkin olduğu sürece o elemanın içeriği<br />

değiştirilebilir.<br />

• Flip-flop larda clock sinyalinin yükselişi veya düşüşüne göre çıkış değeri<br />

değişir. Clock sinyalinin kararlı durumlarında ( clock sinyalinin sabit bir<br />

seviyede olduğunda ) flip-flop un çıkışı değişmez.

5<br />

Register ( Kaydedici ) tasarımında dikkat edilmesi gereken bazı hususlar vardır.<br />

Bunlar yerine getirilmezse register çalışmaz veya verimsiz çalışır. Bunları sırasıyla<br />

inceleyelim.<br />

2.1.2. CLOCK İŞARETİ<br />

Sayısal sistemlerdeki elemanların eş zamanlı çalışmasını sağlayan dikdörtgen dalga<br />

şeklinde bir işarettir. Clock işareti ile denetlenen elemanlar sadece clock işareti etkin<br />

olunca işlem yaparlar. Onun dışında eski konumlarını korurlar. Clock işaretinin<br />

kullanılması açısından elemanlar ikiye ayrılırlar.<br />

2.3.1. Düzey Tetiklemeli Elemanlar : Clock işaretinin bir düzeyini ( pozitif lojikte<br />

‘1’ düzeyini ) etkin düzey olarak kabul ederler. Bu elemanlar clock işareti ‘1’<br />

düzeyindeyken işlem yaparak durumlarını ve çıkışlarını değiştirirler.<br />

Clock işaretinin ‘1’ düzeyindeyken girişler işleme sokulduğundan, bu süre boyunca<br />

giriş değerleri sabit tutulmalıdır. Aksi durumda ardışıl elemanın çıkışının alacağı<br />

değer belirsiz olur. Bu süreye kayıt süresi denir clock işaretinin ‘0’ olduğu sürede<br />

ise girişler değiştirilebilir. Bu süreye yerleşme süresi denir.<br />

2.3.2. Kenar Tetiklemeli Elemanlar : clock işaretinin bir kenarını ( pozitif lojikte<br />

çıkan kenar ) etkin kenar olarak kabul ederler. Bu elemanlar clock işareti 0-1 geçişi<br />

yapınca ( çıkan kenar ) işlem yaparak durumlarını ve çıkışlarını değiştirirler. Clock<br />

işareti geçiş yapmazsa eski durumlarını korurlar. Negatif lojikte ise işlemler 1-0<br />

geçişinde ( inen kenar ) yapılır. Clock işaretinin 0-1 geçişi yaparken girişler işleme<br />

sokulduğundan, bu kenardan belli bir süre önce ve sonra giriş değerleri sabit<br />

tutulmalıdır. Aksi durumda ardışıl elemanın çıkışının alacağı değer belirsiz olur.

6<br />

2.1.3. FLIP-FLOP VE LATCH PARAMETRELERİ<br />

2.1.3.1. KURMA VE TUTMA ZAMANLARI ( Set-up, Hold Time )<br />

2.1.3.1.1. Kurma Zamanı (set-up time, ts) : Flip-floplar girişlerdeki tetikleme<br />

sinyalinin durumuna göre çıkış değerini değiştirirler. Flip-flop girişlerindeki<br />

tetikleme sinyalinin flip-flop çıkışını (Q,Q’) değiştirmesi için geçen zamana kurma<br />

zamanı denir. Devreler dizayn edilirken izin verilebilen minimum kurma zamanı<br />

belirlenmelidir. Eğer bu zaman gereksinimi sağlanmazsa, devre tetikleme sinyalinin<br />

durum değişikliklerine güvenli tepki vermeye bilir.<br />

2.1.3.1.2. Tutma Zamanı (hold time, th) : Tetikleme sinyalinin senkronize<br />

girişlerdeki durum değişikliğini hissedebilmesi için gerekli zaman aralığıdır. Devre<br />

tasarımcıları tarafından minimum sınırı belirlenen bu zamanın sağlanmaması<br />

durumunda flip-flop güvenli olarak tetiklenemez.<br />

Şekil 2.1. FF Kontrol Girişleri İçin Kurma-Tutma Zamanları<br />

Tetiklemeli flip-flop un tetikleme sinyaline düzgün tepki verebilmesi için, senkronize<br />

girişlerin belirli bir süre değişmeden durması gerekir (Kurma ve tutma<br />

zamanlarından dolayı). Bu süre, tetikleme sinyalinin durum değiştirmesinden önce<br />

‘ts’ kadar, durum değişikliğinden sonra ‘th’ kadar olmalıdır. Senkron sistemlerde çok<br />

önemli olan bu zamanların ölçümünde, durum değişikliklerinin %50 seviyesi<br />

referans olarak alınır.

7<br />

2.1.3.1.3. Yayılım Gecikmesi (Propagation Detay-tpd ) ve Yayılım hızı (<br />

Propagation Speed )<br />

Dijital devrenin veya lojik kapının girişindeki değişme ile buna bağlı olarak çıkışta<br />

meydana gelecek değişme arasındaki zaman farkına ‘yayılma gecikmesi’ adı verilir<br />

ve nanosaniye (nsn) cinsinden ifade edilir. Yayılım hızı ise yapılan işlemin hızını<br />

belirtir ve MHz cinsinden ifade edilir.<br />

Şekil 2.2. Lojik entegrelerde meydana gelen yayılım gecikmesi<br />

tpHL → 1’ den 0’a geçerken harcanan zaman,<br />

tpLH → 0’dan 1’e geçerken harcanan zaman,<br />

tpd → iki değerin (tphl ve tplh ) ortalaması.<br />

Genelde tpHL ve tpLH değerleri yükleme durumlarına baglı olarak değişebilir ve<br />

aynı değerlerinde olmayabilir. Aynı değerde olmaması durumunda , iki değerin<br />

aritmetik ortalaması alınır.<br />

2.1.3.1.4. CLOCK SKEW<br />

İdeal clock sinyalinin yükselme ve düşme zamanları minimum olmalıdır ve<br />

gecikmesi sıfır olmalıdır. Gerçek uygulamalarda clock sinyalinin gecikmesi sıfır<br />

değildir.<br />

Bir sayısal devrede clock sinyalinin devre elemanları olan çiplere ulaşmasındaki<br />

zaman farklılığına clock skew denir. Bir başka değişle devrede tek bir clock sinyali<br />

olmasına rağmen her bir devre elemanının clock sinyali diğerine göre faz farklıdır.<br />

Aşağıdaki şekilde ardışıl kaydediciler görülmektedir. Şekil 2.3 deki bütün<br />

kaydedicilere aynı clock sinyali uygulanmıştır ama her bir kaydediciye ulaşan clock<br />

sinyali birbirinden farklıdır (Nedovic, N., 2003)

8<br />

Şekil 2.3 Ardışıl kaydediciler.<br />

Şekil 2.3 deki devrenin clock sinyalleri aşağıdaki şekil 2.4 de gösterildiği gibi olur.<br />

Şekil 2.4 Kaydedicilere ulaşan clock sinyallerinin şekli<br />

Flip-flop girişlerinin set-up ( kurma süresi ) ve hold time ( tutma süresi ) değerlerini<br />

karşılaması sağlanmalıdır ve bu önemli bir dizayn problemidir. Yayılım<br />

Gecikmesinin ( Propagation Delay ) önemli olduğu hesaplamalarda clock skew ihmal<br />

edilemez.<br />

Bilgisayar sistemlerinde clock skew için makine saykılının %10’ una kadar izin<br />

verilir. VLSI chip dizaynında da bu değeri sağlamak önemli bir problemdir.<br />

Chiplerde clock sinyali üreteci olarak ring osilatör kullanmak en basit tekniktir.<br />

Böyle bir osilatör devresi şekil 2.5 de görülmektedir.

9<br />

Şekil 2.5. Ring osilatörü kullanılarak yapılmış basit bir clock üreteci<br />

VLSI chip ailesinde yüksek performans için kristal osilatör kullanan ayrı clock<br />

chipleri kullanılır. Şekil 2.6 da kristal osilatör devresi görülmektedir. Bu devre<br />

hemen hemen seri rezonans devresidir. Devredeki kristal çıkışta düşük yük<br />

empedansı oluşturur. Bu devrenin eşdeğer modeli kristal seri RLC devresi gibi<br />

düşünülebilir. Bu devre sayesinde daha yüksek seri direnç, daha düşük osilasyonlu<br />

frekans meydana gelir. Ayrıca kristalin terminallerindeki çıkış yükü frekans ve<br />

frekans kararlılığı üzerinde etkilidir.<br />

Şekil 2.6. Kristal Osilatör Devresi<br />

Clock sinyalindeki gecikmeleri önlemenin ideal yolu H ağacı denilen bir yapıdır.<br />

Böyle bir yapı şekilde görülmektedir. Bu yapıda bütün dal noktalarının merkeze olan<br />

mesafesi aynıdır. Böylelikle sinyal gecikmesi aynı olmuş olur. Fakat bu yapının<br />

uygulanması kaynak sınırlaması ve fanout gereksinimi için oldukça zordur (Nedovic,<br />

N., 2003).

Şekil 2.7. H Ağaç Yapısı<br />

10

11<br />

2.1.4. SAYISAL ENTEGRE TERMİNOLOJİSİ<br />

2.1.4.1. Güç Harcaması ( Power Dissipation )<br />

‘Güç Harcaması’; bir lojik kapının harcadığı güç miktarıdır ve mW cinsinden ifade<br />

edilir.Entegrede harcanan güç genelde tek bir kaynaktan elde edilir . Entegrenin güç<br />

kaynağına bağlanacak ucu bipolar entegrelerde ‘Vcc’, CMOS entegrelerde ‘Vdd’<br />

olarak isimlendirilir. Bir lojik kapının bağlı olduğu güç kaynağından çekeceği akım,<br />

kapının çıkışının aldığı değere (0 veya 1) göre değişir. Bu değişiklik, entegre<br />

devrenin harcadığı gücün değişmesi sonucunu doğurur. Entegre devrenin harcadığı<br />

gücü bulmak için, çıkısın ‘0’ ve ‘1’ olduğu anlarda entegrede harcanan gücün<br />

ortalaması alınır.<br />

2.1.4.2. Çıkış Kapasitesi ( fan out )<br />

Bir lojik kapının çıkışına bağlanabilecek maksimum yük sayısına ‘çıkış kapasitesi –<br />

fan out ’denir.’fan out’ değeri entegre çeşidine göre farklılık gösterir. Karmaşık<br />

devrelerde ,kullanılan entegrenin çıkışına kaç tane kapı devresinin<br />

bağlanabileceğinin bilinmesi gerekir.Çıkış ucuna fazla sayıda yük bağlanırsa entegre<br />

bozulur.<br />

Ardı ardına bağlanacak entegrelerin aynı cins olması uygulamada kolaylık sağlar.<br />

‘Fan Out’ değeri ,kullanılan entegrelerin giriş ve çıkış akımlarına göre hesaplanır.<br />

2.1.4.3. Gürültü Bağışıklığı ( Noise Immunity-Noise Magrin )<br />

Gürültü bağışıklığı ,devrenin çalışmasına etki etmeyecek şekilde izin verilebilen<br />

gürültü sınırıdır ve mV cinsinden ifade edilir.TTL entegrelerin 1 konumuna gelmesi<br />

için 2.4v Gereklidir derken ,bunun 0.4V’u gürültü payı olarak konmuştur. ‘o’<br />

seviyesi için de durum aynıdır.<br />

2.1.4.4. Emniyet payı: Bir sayısal devrenin girişine gelen gürültü işaretlerini, gerçek<br />

işaretten ayırabilmek için konulan gerilim farkına sayısal devrenin ‘gürültü-emniyet

12<br />

payı’ denir. ( Şekil 2.8 ) Diğer bir değişle ,lojik devrede giriş ve çıkış işaretlerinde<br />

‘1’ve ‘0’ seviyeleri arasındaki fark , ‘gürültü emniyet payı’ olarak isimlendirilir.<br />

Şekil 2.8 Dijital entegrelerde gürültü emniyet payının tespiti<br />

2.1.4.5. Hız-Güç üretimi (Speed – Power Product)<br />

Sayısal entegreler başlangıçtan beri düşük yayılım gecikmesi ve küçük güç<br />

harcaması özellikleriyle tanımlanır. Lojik entegre aileleri çok değişik hız-güç<br />

harcaması oranına sahiptirler. Bu nedenle sayısal entegreleri kıyaslamada<br />

kullanılacak özelliklerden birisi , ‘hız-güç üretimi’ olarak isimlendirilen ve kapı<br />

yayılım gecikmesi ile kapı güç harcamasının çarpımından elde edilen değerdir.<br />

Örneğin; bir entegrede yayılım gecikmesi 10 nsn ve ortalama güç harcaması 50 mw<br />

ise ;Hız-güç üretimi =10 nsn *50 piko watt-sn (50 piko joule) olarak bulunur.<br />

Sayısal entegrelerin seçiminde düşük hız-güç üretimi tercih edilir. Bu nedenle ,<br />

tasarımcılar entegrenin hızını artırarak yayılım gecikmesini düşürmeye veya güç<br />

harcamasını düşürerek hız-güç üretimini küçültmeye çalışmaktadır. Ancak, transistör<br />

tetiklemeli devrelerin özelliği nedeniyle her ikisini beraber yapmak zordur.<br />

2.1.4.6. Besleme Gerilimi ve Çalışma Isısı<br />

Besleme gerilimi ; entegrenin çalışması için güç kaynağından entegreye uygulanması<br />

gereken gerilim değerini ifade eder.<br />

Çalışma ısısı; entegrenin normal çalışmasını gerçekleyebilmesi ve bozulmadan<br />

çalışabilmesi için imalatçı firma tarafından belirlenen sıcaklık bandıdır.

13<br />

2.1.5. TAMAMLAYICI MOS LOJİK (CMOS) TEKNOLOJİSİ<br />

Tamamlayıcı MOS ( CMOS ) lojik ailesinde P ve N kanal MOSFET’ler birlikte<br />

kullanılmaktadır. CMOS ailesi, P-MOS ve N-MOS kanalın sahip olduğu üstünlükleri<br />

aynı devrede toplar. CMOS entegreler, P ve N tipi MOS’lara göre çok daha karmaşık<br />

bir yapıya ve daha düşük eleman yoğunluğuna sahiptirler.<br />

CMOS entegreler PMOS ve NMOS teknolojilerine göre daha yüksek hız ve daha<br />

düşük güç tüketimi gibi avantajlara sahiptirler. LSI alanı içerisinde pek fazla<br />

kullanılmayan CMOS ailesi, MSI alanında TTL’nin rakibi olarak kullanılmaktadır.<br />

TTL’ye göre daha basit üretim işlemine ve daha yüksek paketleme yoğunluğuna<br />

sahip CMOS ailesi, bu özellikleri nedeni ile bir entegre içerisinde daha fazla sayıda<br />

eleman oluşturmasına imkan tanır. Genelde TTL’lere göre daha yavaş olan CMOS<br />

entegrelerin yeni serilerinde yüksek hızlı elemanlar üretilmektedir.<br />

2.1.5.1. CMOS Entegrelerin Özellikleri<br />

2.1.5.1.1. CMOS Entegrelerde Kullanılan Seriler : CMOS ailesindeki dijital<br />

entegreler çeşitli serilerde üretilmektedir. İlk üretilen CMOS’lar 400A serisinde<br />

iken, geliştirilmiş versiyonu olan CMOS’ lar daha yüksek çıkış akımı ile 400B serisi<br />

olarak üretilmektedirler. 74C ve 54C seriri olarak üretilen CMOS serisi entegreler,<br />

TTL entegresi ile fonksiyon ve pin olarak tam uyumludur. TTL eşdeğeri yerine<br />

kullanılabilen 74C serisinin performansı, 4000 serisi ile aynıdır. Motorola firması<br />

4000 serisini 14000 serisi olarak üretmektedir. Yani, 4004 ile 14004 fonksiyon ve<br />

ayak uyumludur. Sygnetics firması, aynı seriyi HCT4001 şeklinde tanımlamaktadır.<br />

74C serisinin geliştirilmiş şekli daha hızlı olarak imal edilen 74LS serisi TTL’lerin<br />

karşılığı olan 74HC serisi (yüksek hızlı CMOS) entegrelerdir. Bu tipin daha<br />

geliştirilmiş serisi ise, doğrudan TTL çıkışlar tarafından sürülebilen 74HCT serisidir.<br />

Farklı lojik ailelere mensup entegrelerin birlikte kullanılma durumu daha sonraki<br />

konularda izlenecektir.

14<br />

2.1.5.1.2. Besleme Gerilimi ve Gerilim seviyeleri : 4000 ve 74C serisi entegreler;<br />

3-15 Volt arasındaki gerilimler ile, 74HC ve 74HCT serileri ise 2-6 volt arasındaki<br />

gerilimler ile çalışırlar. CMOS ve TTL entegreler birlikte kullanıldığı zaman,<br />

CMOS’un Vdd ve TTL’nin Vcc gerilimlerini aynı kaynaktan sağlamak için her iki<br />

tip eleman +5V ile çalıştırılabilir.<br />

CMOS elemanların yalnızca CMOS elemanları sürme durumunda çıkış gerilim<br />

seviyesi; ‘0’ konumunda yaklaşık 0 V, ‘1’ konumunda ise + Vdd değerinde olur.<br />

CMOS entegreler Vdd = +5 V ile çalıştırıldığı zaman, V IL(MAX) = 1.5V ve V IH(MIN) =<br />

3.5 V olarak kabul edilir.<br />

2.1.5.1.3. Gürültü Sınırları : CMOS entegrelerin DC gürültü bağışıklıkları; Vnmh<br />

=Vnml =%30 Vdd olarak ifade edilir.Vdd=+5 V ise, her iki lojik durumundaki<br />

gürültü sınırı 1.5V olarak bulunur. Bu değer TTL ve ECL’den daha iyidir ve bu<br />

durum yüksek gürültü ortamındaki uygulamalarda CMOS’u üstün duruma geçirir.<br />

2.1.5.1.4. Güç Harcaması : CMOS lojik devreler statik durumda iken (durum<br />

değişmediği zaman) güç harcaması çok düşüktür. Vdd = +5 V olduğu zaman her bir<br />

kapı için 2.5 Nw’lık bir güç harcaması, Vdd=+10 V durumunda ise 10 NW’lık bir<br />

güç harcaması oluşur.<br />

DC çalışmada düşük seviyede kalan CMOS entegrelerin güç tüketimi, anahtarlama<br />

durumu söz konusu olduğu durumlarda yükselir. Örneğin; DC çalışmada 10mW olan<br />

güç tüketimi;100KHZ’de Pd= 0.1 mW değerini alır. Bunun nedeni, çıkışa bağlı yük<br />

nedeni ile oluşan kapasitenin üzerinden akan şarj akımıdır.<br />

CMOS İnverter lerde statik ve dinamik güç olmak üzere iki tip güç harcaması vardır.<br />

CMOS inverterlerdeki statik güç ihmal edilebilir.<br />

Anahtarlama süresince, çıkış yük kapasitansı sırasıyla şarj ve deşarj olurken CMOS<br />

inverter kaçınılmaz olarak güç harcar. Basit bir CMOS inverter devresi şekilde<br />

görülmektedir. Burada giriş geriliminin dalga şekli ideal olarak kabul edilecek ve

15<br />

yükselme, düşme zamanları ihmal edilecektir. Tipik giriş ve çıkış gerilimlerinin<br />

dalga şekilleri ve yük kondansatörünün olması beklenen akım dalga şekli şekilde<br />

görülmektedir.<br />

Giriş gerilimi düşükten yükseğe ( low to high ) devredeki pMOS transistor off<br />

konumuna gelir ve nMOS transistor akım iletmeye başlar. Faz süresince çıkış yük<br />

kapasitansı C load , nMOS transistor üzerinden deşarj olur. Böylece, kondansatör akımı<br />

aniden nMOS transistorun drain akımına eşit olur.<br />

Giriş gerilimi yüksekten düşüğe anahtarlandığında ( high to low ), devredeki nMOS<br />

transistor off konumuna gelir ve pMOS transistor iletime geçer. Faz süresince çıkış<br />

yük kapasitansı C load , pMOS transistor üzerinden deşarj olur. Bundan dolayı<br />

kondansatör akımı aniden pMOS transistorun drain akımına eşit olur.<br />

Şekil 2.9 Dinamik güç harcaması analizi için CMOS inverter<br />

Bir periyottaki ortalama güç harcaması aşağıdaki formülle bulunabilir.<br />

P<br />

avg<br />

1<br />

=<br />

T<br />

∫<br />

T<br />

0<br />

v(<br />

t).<br />

i(<br />

t)<br />

dt<br />

Anahtarlama süresince CMOS inverter içindeki PMOS ve NMOS transistorlar her<br />

bir yarım periyot için akımı iletirler. CMOS inverter için ortalama güç harcaması;<br />

çıkış yük kapasitansının şarj ve dejarjı için gereken güç olarak hesaplanabilir.

16<br />

Şekil 2.10. CMOS invertörün anahtarlaması süresince, giriş ve çıkış gerilim dalga<br />

şekilleri ile kondansatör akımının dalga şeklileri<br />

P<br />

avg<br />

1 ⎡ T / 2 ⎛ dVout ⎞<br />

= ⎢∫<br />

Vout⎜<br />

− Cload<br />

⎟dt<br />

+<br />

T<br />

0<br />

∫<br />

⎣ ⎝ dt ⎠<br />

T<br />

T<br />

/ 2<br />

⎛<br />

out ⎞ ⎤<br />

( V −V<br />

) C dt⎥ ⎦<br />

DD<br />

out<br />

⎜<br />

⎝<br />

Load<br />

dV<br />

dt<br />

⎟<br />

⎠<br />

P<br />

avg<br />

⎡<br />

2<br />

1 ⎛ ⎞<br />

⎤<br />

⎢⎜<br />

V ⎛<br />

⎞<br />

= ⎟<br />

−<br />

out T / 2<br />

1<br />

2 T / 2<br />

Cload<br />

+ ⎜V<br />

−<br />

0 DD.<br />

Vout.<br />

Cload<br />

Cload<br />

. Vout<br />

⎟<br />

T<br />

⎥<br />

T ⎢⎣<br />

⎝ 2 ⎠ ⎝<br />

2 ⎠ ⎥⎦<br />

1<br />

P avg = . C<br />

T<br />

load<br />

. V<br />

2<br />

DD<br />

f= 1/T olduğundan, denklem yeniden yazılırsa;<br />

P<br />

2<br />

avg load DD .<br />

= C V f olarak hesaplanabilir.<br />

Formülden de açıkça görülebileceği gibi, CMOS invertörün güç harcaması frekans<br />

ile orantılıdır. Bundan dolayı, anahtarlama frekansının yüksek olduğu yüksek hızlı<br />

işlemlerde, CMOS devrelerin düşük güç avantajı daha az önemli olmaya başlar. Aynı

17<br />

zamanda ortalama güç harcaması bütün transistorların karakteristiklerine ve<br />

boyutlarına bağlıdır. Dolayısıyla, anahtarlama olayı süresince güç tüketiminin<br />

miktarı anahtarlamanın gecikme zamanı ile ilgili değildir. Sonuç olarak, güç<br />

tüketimi, giriş geriliminin V OL den V OH ye geçerken çıkış kondansatörünün şarj ve<br />

deşarj durumlarında oluşur.<br />

2.1.5.1.5. Fan Out : N-MOS ve P-MOS’larda olduğu gibi, CMOS girişleride çok<br />

büyük bir dirence sahiptirler (10 10 Ω) ve sinyal kaynağından akım çekmezler.Ancak<br />

her bir CMOS giriş 5 pF’lık yük etkisi oluşturur. ( Şekil 2.11 ).Bu giriş kapasitesi ,bir<br />

CMOS elemanın sürebileceği giriş sayısını sınırlar.Bir CMOS elemanın çıkışı, bağlı<br />

bulunduğu tüm girişlerdeki kapasitelerin paralel kombinasyonunu şarj deşarj etmek<br />

zorunda olduğundan,sürülen elemanlarının sayısının artması çıkış anahtarlama<br />

zamanını arttırır.<br />

Şekil 2.11. CMOS bağlı yüklerin kapasite etkisi oluşturması.<br />

CMOS elemanlarda eklenen her bir yük ile ,sürücü devrenin yayılım gecikmesi<br />

ortalama 3 nsn artar. Yüksüz durumda tphl =30 nsn yayılım gecikmesine sahip bir<br />

‘VEDEĞİL’ kapısının 20 yüke sahip olması durumundaki yayılım gecikmesi:<br />

Toplam yayılım gecikmesi = tphl (yüksüz)+(yük sayısı )*3<br />

= 30 nsn +(30nsn)=90nsn olur<br />

Bu durumda fan_out’un maksimum yayılım gecikmesine bağlı olduğu sonucu<br />

doğurur .Genel olarak 1mhz’in altındaki uygulamalarda ‘fan –out’ değeri 50 sayısı<br />

ile sınırlandırılır.

18<br />

2.1.5.1.6. Anahtarlama Hızı : Her ne kadar CMOS büyük kapasitif yükleri sürmek<br />

zorunda olsada ,düşük çıkış direnci (P-MOSFET’in 1 durumundaki Ron direnci ≤<br />

1kΩ dur) yük kapasitansının hızlı şarj olmasını sağlar . Bu durum anahtarlama hızını<br />

arttırır.<br />

4000 serisi ‘VEDEĞİL’ kapısı;<br />

VDD = +5 V’ta ortalama tpd =50 nsn,<br />

VDD = 10V’ ta tpd =25nsn<br />

yayılım gecikmesine sahiptir. Vdd nin artmasıyla tpd değerinin artmasının nedeni;<br />

yüksek besleme geriliminde MOSFET’in R ON değerinin küçülmesidir. Bu durum,<br />

yüksek hız gerektiren yerlerde V DD geriliminin mümkün olduğu kadar yüksek<br />

tutulması gerektiğini ortaya çıkarsa da, V DD nin değerinin arttırılması(aynı devre<br />

üzerinde V DD sabittir, buradaki artıştan kasıt V DD değeri daha yüksek bir devre<br />

dizayn etmektir.) ile güç tüketiminin artacağı ortadadır.

19<br />

2.1.6. LATCH<br />

Latch ve Flip-Flop analizi yapmadan önce ARDIŞIL ( Sequential ) devrelerin<br />

elektriksel davranışlarını bilmek gerekmektedir. Çünkü latch ve flip-flop lar bu temel<br />

üzerine oluşturulmaktadır.<br />

Ardışıl devreler, bileşik devrelere geri besleme bloğu eklenerek elde edilen<br />

devrelerdir. Ardışıl devrelerde sıkça kullanılan bellek elemanları, bileşik devrelere<br />

geri besleme yolu ( feedback ) sağlayacak şekilde bağlanırlar.<br />

Belleklerde saklanan ikili bilgiler, sıralı devrelerin durumunu tanımlar. Harici<br />

girişlerden ikili bilgiler alan ardışıl devre, hariçten aldığı ikili bilgi ile, bellek<br />

elemanlarının mevcut durumlarını birleştirerek çıkışta oluşacak ikili değerleri belirler<br />

(Kang, S., 1999)<br />

Geri beslemeli bu devreler çift kararlı, tek kararlı ve serbest çalışan olmak üzere üç<br />

guruba ayrılmaktadırlar. Dışarıdan bir müdahaleye gereksinim duymadan, belirli<br />

aralıklarla durum değiştirerek sinyal üreten devrelere, serbest çalışan devreler<br />

denilmektedir. Dışarıdan uygulanan uygun bir sinyal ile durumunu geçici bir süre<br />

değiştirip, bir süre sonra tekrar eski konumuna dönen devrelere tek kararlı devreler<br />

denilir. Dışarıdan bir müdahale yapılmadığı sürece bulunduğu durumu sürekli<br />

koruyan devrelere de çift kararlı devreler denilmektedir.<br />

Latch ve flip-floplarda kullanılan elemanlar çift kararlı olduğundan, bu tip<br />

elemanların elektriksel davranışları incelenecektir.<br />

2.1.6.1. İki Kararlı Elemanların Elektriksel Davranışları<br />

İki kararlı elemanlar, birbirine çapraz bağlı iki özdeş çevirici ( inverter ) devresi<br />

içermektedir. İki kararalı devrelerin basit blok diyagramı Şekil 2.12.a da<br />

görülmektedir. Şekilden de anlaşılacağı gibi, 1 numaralı invertör çıkış gerilimi, 2<br />

numaralı invertör giriş gerilimine eşittir ( V 01 = V 12 ). Aynı şekilde 2 numaralı<br />

invertör çıkış gerilimi de 1 numaralı invertör giriş gerilimine eşittir ( V 02 = V 11 ). Her<br />

iki invertörün de giriş çıkış davranışını inceleyebilmek için, öncelikle invertörlerin<br />

gerilim transfer karakteristiklerinin çizilmesi gerekmektedir. Bu eğri çizilirken x<br />

ekseninde giriş gerilimi, y ekseninde çıkış gerilimi gösterilir. Buna göre çizilen

20<br />

gerilim transfer karakteristik eğrisi şekil 2.12.b de gösterilmiştir. Şekilde görüldüğü<br />

gibi iki gerilim eğrisi üç noktada kesişmektedir. Bu noktalardan iki tanesi kararlı, bir<br />

tanesi kararsız noktadır. Şayet devre bu iki kararlı durumdan birinde işleme başlarsa,<br />

harici bir etki olmadıkça bu konumunu sürekli koruyacaktır.<br />

(a)<br />

(b)<br />

Şekil 2.12.a) İki Kararlı Devrelerin Basit Blok Diyagramı b) Gerilim Transfer Eğrisi<br />

Bu anda geri besleme gerilim eğrisinin eğimi, kararlı iki işlem noktasının<br />

bileşkesinden daha küçüktür. Yani invertörlerin kazancı küçüktür. Bunun için; karalı<br />

durumların birinden diğerine geçerken yeterince büyük harici bir sinyal<br />

uygulanmalıdır. Harici sinyal sayesinde invertörlerin geri besleme gerilim kazancı<br />

kararlı noktaların bileşkesinden büyük olmaktadır. Şekil 2.12..b de gösterilen üçüncü<br />

noktada karasız işlem noktasıdır. İşte bu gibi kararlı iki işlem noktasına sahip<br />

devreler; çift kararlı devreler denilmektedir. (Kang, S., 1999)<br />

Şekil 2.12. de latch lerin temelini oluşturan iki kararlı devre şeması görülmektedir.<br />

Latchler genellikle dijital devrelerde sinyal depolama ve gecikme elemanı olarak<br />

kullanılmaktadırlar. Diğer hafıza elemanları ile karşılaştırıldığında latchler, daha<br />

fazla güç harcamaktadırlar ve daha fazla devre alanına ihtiyaç duymaktadırlar.<br />

Şekil 2.13. Statik Latch Devre Şekli

21<br />

Şekil 2.13 de görüldüğü gibi Latchler, birbirine çapraz bağlı iki adet çeviriciden (<br />

invertör ) oluşmaktadır. Bu şekildeki M1 ve M2 mosfetleri P-tipi, M3 ve M4<br />

mosfetleri N-tipi mosfetlerdir. Kararsız işlem noktasında buradaki dört MOSFET de<br />

saturation ( doyum ) bölgesindedir. Bu noktada, eğer devrenin ilk işlemi SET ise,<br />

küçük gerilim sinyalleri transistorların işlem modunda önemli değişikliklere sebep<br />

olacaktır. Bunun için her iki invertör çıkış geriliminde de değişiklik görülür. Örneğin<br />

Şekil 2.14. de görüldüğü gibi, birinci invertörün çıkış gerilimi V oH değerini alırken,<br />

ikinci invertörün çıkış gerilimi V oL değerini almaktadır.<br />

Şekil 2.14. Gerilimin Değişim Eğrisi<br />

Bu olay, küçük işaret analiz yöntemiyle Şekil 2.14. yardımıyla şu şekilde<br />

açıklanabilmektedir.<br />

Şekil 2.15. Kaskad Bağlı İki İnverter<br />

Bu analizde; her iki invertörün giriş ( gate ) kapasitesi C g , invertörlerin çıkış ( drain )<br />

kapasitesi C d den daha büyüktür( C g >> C d ). İlk önce, devrenin ( V 01 = V 02 = V th )<br />

kararsız işlem noktasında olduğunu varsayalım.<br />

Şekil 2.15. de görüldüğü gibi her bir invertörün Drain akımı diğer invertörön gate<br />

akımına eşit olmaktadır. Buna göre aşağıdaki eşitlik yazılabilir;<br />

i<br />

i<br />

= i = g ⋅ v<br />

……………...(6.1)<br />

g1 d 2 m g 2<br />

= i<br />

= g<br />

⋅ v<br />

g 2 d1<br />

m g1

22<br />

Bu formüllerde kullanılan g m , invertörün küçük işaret geçiş iletkenliğini temsil<br />

etmektedir. İnvertörlerin gate gerilimleri de şu şekilde ifade edilebilir;<br />

v<br />

q<br />

= 1<br />

2<br />

g 1 g<br />

C<br />

g<br />

C<br />

g<br />

q<br />

v = ……………...(6.2)<br />

2<br />

Her bir invertörün küçük sinyal gate akımı zamanın türevi şeklinde yazılabilir.<br />

i<br />

g1 =<br />

C<br />

g<br />

dv<br />

dt<br />

g1<br />

dvg<br />

2<br />

ig<br />

2<br />

= C<br />

g<br />

……………...(6.3)<br />

dt<br />

Denklem 6.1 ile 6.3 birlikte düzenlenirse;<br />

g<br />

g<br />

g<br />

C<br />

g<br />

C<br />

m<br />

m<br />

g<br />

dvg1<br />

⋅ vg<br />

2<br />

= C<br />

g<br />

……………...(6.4)<br />

dt<br />

dvg<br />

2<br />

⋅ vg1 = C<br />

g<br />

..…...………..(6.5)<br />

dt<br />

⋅ dq<br />

q = 2<br />

dt<br />

……………...(6.6)<br />

m 1<br />

g<br />

⋅ dq<br />

q = 1<br />

dt<br />

……………...(6.7)<br />

m 2<br />

Denklem 6.6 ve 6.7 deki diferansiyel eşitlikler birlikte q1 in zamana bağlı davranışını<br />

tanımlayarak ikinci dereceden diferansiyel eşitliği vermektedir.<br />

g<br />

C<br />

m<br />

g<br />

2<br />

2<br />

2<br />

C<br />

g d q1<br />

d q ⎛<br />

1<br />

g ⎞<br />

⋅ q1<br />

= ⋅ ise ⎜<br />

m<br />

⎟ q<br />

2<br />

2<br />

1<br />

g<br />

m<br />

dt dt<br />

C<br />

g<br />

= ……………...(6.8)<br />

⎝ ⎠

23<br />

Bu eşitlik geçici durum sabitesi τ 0 kullanılarak basitleştirilebilir,<br />

d<br />

2<br />

1<br />

2<br />

dt<br />

q<br />

1<br />

= q<br />

1<br />

ile<br />

τ<br />

2<br />

0<br />

C<br />

g<br />

τ<br />

0<br />

=<br />

……………...(6.9)<br />

g<br />

m<br />

q<br />

q<br />

v<br />

v<br />

1<br />

() t<br />

t<br />

t<br />

( 0) −τ<br />

0q<br />

( 0) −<br />

1 τ q ( 0) ( 0) 0 1<br />

+ τ<br />

0q<br />

+<br />

1 τ 0<br />

q1<br />

= e +<br />

e<br />

…………….(6.10)<br />

2<br />

2<br />

( ) C g<br />

⋅ v ( 0)<br />

1<br />

0<br />

g1<br />

02<br />

01<br />

= …………….(6.11)<br />

−<br />

+<br />

1<br />

1<br />

=<br />

02 0 02<br />

02 0 02<br />

…………….(6.12)<br />

2<br />

2<br />

τ 0 τ 0<br />

() t ( v ( 0) −τ<br />

v ( 0)<br />

) e + ( v ( 0) + τ v ( 0)<br />

) e<br />

τ 0 τ 0<br />

() t ( v ( 0) −τ<br />

v ( 0)<br />

) e + ( v ( 0) + τ v ( 0)<br />

) e<br />

t<br />

t<br />

−<br />

+<br />

1<br />

1<br />

=<br />

01 0 01<br />

01 0 01<br />

…………….(6.13)<br />

2<br />

2<br />

t<br />

t<br />

t’nin büyük değerleri için zamana bağlı olan denklem 2.16 ve 2.17<br />

basitleştirilebilmektedir, bu durumda denklemler şu şekilde yazılabilir.<br />

v<br />

v<br />

01<br />

02<br />

1<br />

2<br />

τ 0<br />

() t = ( v ( 0) + τ v ( 0)<br />

) e<br />

1<br />

2<br />

01<br />

0<br />

01<br />

t<br />

+<br />

τ 0<br />

() t = ( v ( 0) + τ v ( 0)<br />

) e<br />

02<br />

0<br />

02<br />

t<br />

+<br />

…………….(6.14)<br />

Burada görüldüğü gibi, her iki çıkış geriliminin de büyüklüğü zaman ile üstsel olarak<br />

artmaktadır. dv 01 (0) ve dv 02 (0) küçük değerli polaritelere bağlı olarak, her bir<br />

invetörün çıkış gerilimi ilk değeri olan V th değerinden V OL yada V OH değerine<br />

sapmaktadır. Dolayısıyla v 01 her zaman v 02 nin zıttı olmalıdır. Çünkü; bu iki çıkış<br />

gerilimi bir birinin tersi değerleri almaktadır. Örneğin;<br />

v<br />

v<br />

01<br />

02<br />

: V<br />

: V<br />

th<br />

th<br />

→ V<br />

OH<br />

yadaV<br />

OL<br />

→ VOLyadaV<br />

OH<br />

…………….(6.15)<br />

gibi birbirinin zıttı değerleri almaktadırlar.

24<br />

Şekil 2.16. İki Kararlı Devrelerin Davranışını Temsil Eden Faz Aralığı<br />

v 01 ve v 02 arasındaki bu ilişkiyi yukarıdaki faz aralığı grafiği açıklamaktadır. V 01 =V th ,<br />

V 02 =V th işlem noktası karasız bölgeyi göstermektedir. V 01 =V OL , V 02 =V OH ve<br />

V 01 =V OH , V 01 =V OL işlem noktaları da kararlı bölgeleri göstermektedirler.<br />

Çift kararlı devreler kararsız işlem noktasından, kararlı işlem noktalarından birine<br />

geçerken aşağıdaki şekilde görüldüğü gibi, sinyalin kaskad bağlı iki invertörden<br />

oluşan döngüde birçok kez dolaşabileceği düşünülebilir.<br />

Şekil 2.17. Kurma Süresince İki İnvertörden Oluşan Döngüdeki Geçici Durum<br />

Sinyalinin Yayılım Gecikmesi

25<br />

Bu periot süresince çıkış geriliminin ( v 01 ) zamana bağlı davranışı şu şekilde olur;<br />

() t<br />

( 0)<br />

v<br />

+<br />

01 τ 0<br />

v<br />

01<br />

t<br />

= e<br />

…………….(6.16)<br />

Döngü kazancını ( kaskad bağlı invertörlerin gerilim kazancı ) A harfiyle ifade<br />

edersek;<br />

A<br />

n<br />

t<br />

+<br />

τ 0<br />

= e<br />

…………….(6.17)<br />

Olur. Bu eşitlik, kararlı noktalara erişene kadar sapmanın ( gecikmenin ) zamana<br />

bağlı değişimini ifade etmektedir.<br />

2.1.6.2. S – R LATCH<br />

Şekil 2.18. de S ( SET ) ve R ( RESET ) girişleri olan basit CMOS SR Latch<br />

görülmektedir. Bu devre iki adet CMOS NOR2 kapısı içermektedir. Her bir NOR<br />

kapısının giriş terminallerinden bir tanesi diğer NOR kapısının çıkışı ile çapraz<br />

olarak bağlanmıştır. SR Latch devresi bir birini tamamlayan Q ve Q’ çıkışlarına<br />

sahiptir. Q çıkışı lojik ‘1’ iken Q’ çıkışı lojik ‘0’ dır. Aynı şekilde Q çıkışı lojik ‘0’<br />

iken Q’ çıkışı lojik ‘1’ dir. Şekilden de kolaylıkla görülebileceği gibi her iki girişte<br />

lojik ‘0’ olduğunda çıkış bir önceki çıkış konumunu korur. Şayet set girişi lojik ‘1’,<br />

reset girişi lojik ‘0’ yapılırsa Q çıkışı lojik ‘1’ Q’ çıkışı lojik ‘0’ olur. Bunun anlamı<br />

SR Latch, önceki durumunu önemsemeksizin set pozisyonunu alır demektir. Aynı<br />

şekilde set girişi lojik ‘0’, reset girişi lojik ‘1’ yapılırsa Q çıkışı lojik ‘0’, Q’ çıkışı<br />

lojik ‘1’ olur. Yani SR Latch önceki durumunu önemsemeksizin reset pozisyonunu<br />

alır.

26<br />

Eğer her iki girişte lojik ‘1’ yapılırsa; bu durumda her iki çıkış noktası da lojik ‘0’<br />

olmaya zorlanacaktır. Bundan dolayı bu giriş kombinasyonuna normal çalışma<br />

modunda izin verilemez. Bu devrenin doğruluk çizelgesi aşağıdaki gibidir.<br />

Çizelge 2.1. S-R Latch Devresinin Doğruluk Çizelgesi<br />

S R Q Q’ İş<br />

0 0 Önceki Önceki Hold<br />

1 0 1 0 Set<br />

0 1 0 1 Reset<br />

1 1 0 0 İzin verimez<br />

Şekil 2.18. S-R Latch Devre Şekli<br />

Şekil 2.18 deki dört nMOS transistorun ( M1, M2, M3, M4 ) işlem modları dikkate<br />

alınarak devreyi daha ayrıntılı inceleyelim. Şayet set girişi V OH ve reset girişi V OL ise<br />

paralel bağlanmış olan M1 ve M2 transistorları iletimdedir. Dolayısıyla, Q’<br />

noktasındaki gerilim V OL = 0 kabul edilebilir (lojik-LOW). Aynı zamanda M3 ve M4<br />

transistorları kesimdedir. Bunun sonucunda Q noktasındaki gerilim V OH dir. Eğer<br />

reset girişi V OH ye eşit ve reset girişi V OL ye eşit ise M1 ve M2 kesimde, M3 ve M4<br />

iletimde olur. Her iki giriş gerilimi de V OL ye eşit olursa, SR Latch devresinin önceki<br />

durumuna bağlı olarak iki çıkış durumu oluşur. Bu durumlar aşağıdaki çizelgede<br />

olduğu gibi özetlenebilir. Kolaylık olması için tamamlayıcı pMOS transistorların<br />

işlem modları listelenmemiştir.

27<br />

Çizelge 2.2. PMOS transistorların İşlem Modları<br />

S R Q Q’ Operation<br />

V OH V OL V OH V OL M1-M2 on, M3-M4 off<br />

V OL V OH V OL V OH M1-M2 off, M3-M4 on<br />

V OL V OL V OH V OL M1-M4 off, M2 on<br />

V OL V OL V OL V OH M1-M4 off, M3 on<br />

Şekil 2.18. de verilen devrenin çalışmasını inceleyebilmek için PSPICE devre analiz<br />

programında uygun program aşağıda yazılmıştır. Devrenin 1 ( S Girişi ), 4, 5 ve 6 ( R<br />

Girişi ) noktalarından alınan sinyal eğrileri de şekil 2.19. de verilmiştir.<br />

S-R FLIP-FLOP<br />

VDD 2 0 DC 5V<br />

VR 6 0 PWL(0NS 0V 0.25NS 0V 0.26NS 5V 0.4NS 5V 0.41NS 0V 0.8NS 0V<br />

+0.81NS 5V 1.12NS 5V 1.13NS 0V 1.6NS 0V 1.61NS 5V )<br />

VS 1 0 PWL(0NS 5V 0.1NS 5V 0.11NS 0V 0.5NS 0V 0.51NS 5V 0.7NS 5V<br />

+0.71NS 0V 1.25NS 0V 1.26NS 5V 1.5NS 5V 1.51NS 0V 1.62NS 0V)<br />

.MODEL CMOSN NMOS (Level=7<br />

MPO1 3 1 2 2 CMOSP W=50U L=0.2U<br />

MPO2 5 4 3 3 CMOSP W=30U L=0.2U<br />

MPO3 7 6 2 2 CMOSP W=50U L=0.2U<br />

MPO4 4 5 7 7 CMOSP W=30U L=0.2U<br />

MNO1 5 1 0 0 CMOSN W=20U L=0.2U<br />

MNO2 5 4 0 0 CMOSN W=10U L=0.2U<br />

MNO3 4 5 0 0 CMOSN W=10U L=0.2U<br />

MNO4 4 6 0 0 CMOSN W=20U L=0.2U<br />

MPO5 8 4 2 2 CMOSP W=2U L=0.2U

28<br />

MNO5 8 4 0 0 CMOSN W=1U L=0.2U<br />

MPO6 9 5 2 2 CMOSP W=2U L=0.2U<br />

MNO6 9 5 0 0 CMOSN W=1U L=0.2U<br />

.TRAN .001NS 2NS<br />

.PROBE<br />

.END<br />

5.0V S<br />

0V<br />

V(1)<br />

5.0V R<br />

0V<br />

V(6)<br />

5.0V<br />

0V<br />

V(4)<br />

Q<br />

SEL>> Q'<br />

0V<br />

0s 0.4ns 0.8ns 1.2ns 1.6ns 2.0ns<br />

V(5)<br />

Time<br />

Şekil 2.19. Giriş Ve Çıkış Dalga Şekilleri<br />

t plh = 0,1086 ns ( 0’ dan1’ e geçerken harcanan zaman )<br />

t phl = 0,1174 ns ( 1’ den 0’ a geçerken harcanan zaman )

29<br />

SR Latch devresinin transient analizi, durum değişikliğindeki sonuçlar dikkate<br />

alınarak açıklanacaktır. Set sinyali uygulanınca önceki reset konumundaki Latch set<br />

oluyor yada reset sinyali uygulanınca set konumundaki Latch reset oluyor. Bie başka<br />

durum, her iki çıkış noktası da eş zamanlı olarak gerilim geçişine uğrar. Çıkışlardan<br />

biri düşük lojik seviyeden yüksek lojik seviyeye yükselirken diğeri çıkış noktası,<br />

kendisinin yüksek lojik seviyesinden düşük lojik seviyeye geçer. Böylece, iki çıkış<br />

noktasının eş zamanlı olarak anahtarlanması için zaman gereksiniminin miktarı bir<br />

problem oluşturur. Bu problemin çözümü, her bir çıkış noktasının iki eş diferansiyel<br />

denkleminin eş zamanlı çözümünü gerektirir. Şayet iki olay eş zamanlıdan ziyade<br />

sıralı olarak meydana gelirse problem oldukça basitleştirilebilir. Bu kabul<br />

anahtarlama zamanının fazla tahmin edilmesine sebep olabilir.<br />

Her iki çıkış noktası için anahtarlama zamanının hesaplanmasında, her iki çıkış ile<br />

toplam parazitik kapasitans bulunacaktır. Devredeki her bir kapasitans aşağıdaki<br />

şekilde ifade edilebilir.<br />

C Q = C gb,2 + C gb,5 + C db,3 + C db,4 + C db,7 + C sb,7 + C db,8<br />

C Q’ = C gb,3 + C gb,7 + C db,1 + C db,2 + C db,5 + C sb,5 + C db,6<br />

Set ‘1’ reset ‘0’ olduğu durumda, yükselme zamanı aşağıdaki gibi hesaplanabilir.<br />

t rise,Q (SR Latch)= t rise,Q (NOR2) + t fall,Q’ (NOR2)<br />

burada şunu unutmamak gerekir, t rice,Q anahtarlama zamanını hesaplanmasında NOR2<br />

kapısının yükselme ve düşme zamanları için iki ayrı hesaplamaya ihtiyaç duyulur. Q’<br />

çıkış gerilimi M1 transistorunun iletime geçmesinden dolayı yüksek seviden alçak<br />

seviyeye düşer. Bunu takiben Q çıkışı M3 transistorunun kesime gitmesi ile alçak<br />

seviyeden yüksek seviyeye çıkar. Bu yöntemde M1 ve M2 transistorları kesimde<br />

kabul edilebilir, gerçi M2 Q çıkışının yükselmesinden dolayı iletime geçebilir,<br />

böylece Q’ noktasının düşme zamanını kısaltır. Bu yaklaşım, bununla birlikte,<br />

gecikme zamanı için basit bir tahmin olarak kabul edilebilir.

30<br />

2.1.7. STATİK LATCH DEVRESİNİN OPTİMİZASYONU<br />

Set / Reset Latch, statik ardışıl devrelerde genellikle kullanılan yapılardan biridir. Bu<br />

yapı, statik flip-flopların özünü oluşturmaktadır. Genellikle S / R latchler birbirine<br />

çapraz bağlı iki adet NOR yada NAND kapısından oluşmaktadır. Bu her iki tip S / R<br />

latch devresinde de kompleks pozitif geri besleme bloğu vardır. Bu geri besleme<br />

bloğu SPICE yada diğer devre similatörlerinde geçici durum similasyonu ( transient<br />

simulation ) yaparken fazla zaman tüketimi oluşturmaktadır. Bu problem fazla sayıda<br />

latch içeren kopleks VLSI devrelerde daha kötü sonuçlar oluşturmaktadır. Bu<br />

problemi gidermek için CMOS S / R latch devreleri için genel zamanlama<br />

MACROMODEL leri geliştirilmektedir. Bu model uygulanırken öncelikle, CMOS<br />

Latch lerin büyük sinyal eşdeğer devre karakteristik dalga şekilleri göz önüne<br />

alınmaktadır (Burns, 1964). Daha sonra, devre lineer hale getirilmektedir.<br />

Genel zamanlama mokromodeli uygulanarak, farklı CMOS S / R latch lerin ( farklı<br />

kanal boyutlu, farklı kapasitif yüklü, farklı aygıt parametreli ve giriş dalga şekilli )<br />

sinyal zamanlaması kolaylıkla ve tatmin edici doğrulukla hesaplanabilmektedir.<br />

Bununla beraber bu makromodel, latchlerin hız karakteristik analizlerine, çeşitli<br />

CMOS flip-flopların sinyal zamanının hesaplanmasına ve uygun kanal boyutlarının<br />

belirlenmesine uygulanabilmektedir.<br />

2.1.7.1. Makromodelin Yapısı<br />

Bu makromodel oluşturulurken CMOS NAND tipi S / R latch kullanılmıştır. Bu<br />

devrenin karakteristik dalga şekli SPICE devre tasarım programı kullanılarak elde<br />

edilmiştir. Kullanılacak olan devre, şekil 2.20. de gösterilmektedir. Şekil 2.21. deki<br />

dalga şekli üzerinde verilen numaralar, latch devresi üzerinde gösterilmiş olan<br />

numaralardır.<br />

Şekil 2.20 ve şekil 2.21 de görüldüğü gibi, sürme devresinin sağ tarafındaki NAND<br />

kapısının giriş gerilimi olan V 17 gerilimi artarken çıkış gerilimi olan V 21 de herhangi<br />

bir değişiklik olmamaktadır. Çünkü, o anda V 20 gerilimi düşük ( low ) gerilim<br />

seviyesindedir ve M N3 isimli NMOS kesimdedir. Dolayısıyla V 21 gerilimi V DD<br />

geriliminin seviyesindedir. Sürme devresinde sadece giriş gerilimi etkin olduğundan,

31<br />

V 16 gerilim değeri düşmektedir. Sürme devresinin sol tarafındaki NAND kapısının<br />

giriş gerilimi V 16 nedeniyle buranın çıkış gerilimi olan V 20 , yükselen karakteristik bir<br />

dalga şekline sahiptir. Karakteristik yükselme zamanı T r , V 20 = 0.1 . V DD değeri ile<br />

V 20 = 0.9 . V DD değeri arasında tanımlanmaktadır. Bu bölgede V 17 gerilimi ile V 20<br />

gerilimi birbirine benzemektedir.<br />

Şekil 2.20 NAND-Tipi CMOS Statik Latch Devre Şekli

32<br />

Şekil 2.21. NAND-Tipi CMOS Statik Latch Devresinin Karakteristik Dalga Şekli<br />

Şekil 2.20. de görülen yük devresinde V 20 gerilimi M N4L isimli NMOS u iletime<br />

geçirmektedir. Bu yüzden V 26 gerilimi deşarj olarak 0 V seviyesine inmektedir.<br />

Bununla birlikte bu gerilim V 24 gerilimi üzerinde önemsenmeyecek bir etkiye<br />

sahiptir. Yükleme devresindeki V 20 gerilimi sağ taraftaki NAND kapısını sürerek V 21<br />

gerilimini düşürmektedir. Bu düşen V 21 gerilimi geri besleme yolu ile M N1 isimli<br />

NMOS a iletilmektedir. V 20 gerilimi, V 21 geri besleme sinyalinden neredeyse<br />

bağımsızdır. Bu yüzden yükselme zamanının yerini tutan T r , sürme sinyali V 16 ve<br />

sabit değerli geri besleme sinyali V 21 ile sürme devresinin sol tarafındaki NAND<br />

kapısı dikkate alınarak modellenebilmektedir.<br />

Benzer şekilde karakteristik düşme zamanı T f , V 21 = 0.9 . V DD değeri ile V 21 = 0.1 .<br />

V DD değeri arasında tanımlanmaktadır. Bu düşme zamanı, sürme devresinin sağ<br />

tarafındaki NAND kapısı göz önüne alınarak tanımlanabilir. Burada giriş<br />

gerilimlerinden biri V 20 ve diğer giriş gerilimi V DD gerilim değerine yükselen V 17<br />

gerilimidir. Bu bölgede V 21 ve V 16 gerilimleri benzer düşen karakteristik dalga<br />

şekillerine sahiptirler.<br />

Yükselme zamanı hesaplamasında devrenin eşdeğer devresini bulmak için, yükselme<br />

zamanı süresince her bir noktanın geçici durum davranışı ( transient behaviour )<br />

öncelikle incelenmektedir. Bu zaman süresince, V 17 , V 23 ve V 24 gerilimleri ya sabit<br />

değerlere yada yavaşça değişen değerlere sahip olmaktadırlar. Güç kaynağı gerilimi

33<br />

ile birlikte gerilim değerinin yavaşça değişmesi veya sabit değerde olması, geçici<br />

durum davranışında ya önemsenmeyecek etkiye sahiptir yada herhangi bir etkiye<br />

sahip değildir (WU, C.Y., 1985 ). Bu gerilimler toprağa kısa devre durumundadır. Bu<br />

durum göz önüne alınarak oluşturulan eşdeğer devre, şekil 2.22 de gösterilmektedir.<br />

Şekil 2.22. de MOSFET lerin işlem bölgeleri gösterilmektedir. Yükselme zamanı T r<br />

süresine bazı MOSFET ler iki işlem bölgesinde çalışmayı gerektirmektedir fakat<br />

hesaplamayı kolaylaştırabilmek için sadece bir işlem bölgesi göz önüne alınmaktadır.<br />

Bu basitleştirme işlemi sayesinde, hesaplama karmaşıklığı ve hesaplama hataları en<br />

aza indirilebilmektedir.<br />

Şekil 2.22. Devrede Kullanılan MOSFET lerin İşlem Bölgeleri<br />

Şekil 2.22. deki devrenin ayrıntılı eşdeğer devresi farklı işlem bölgelerinde MOSFET<br />

in büyük işaret eşdeğer devresi kullanılarak oluşturulabilmektedir. MOSFET in<br />

büyük işaret eşdeğer devresi şekil 2.23. de verilmiştir.

34<br />

Şekil 2.23. MOSFET’in Büyük İşaret Eşdeğer Devresi<br />

Büyük işaret eş değer devre şekli kullanılarak oluşturulan ayrıntılı eşdeğer devre<br />

şekilleri de şekil 2.24 de verilmiştir.<br />

Çizelge 2.3. Farklı İşlem Bölgelerindeki Gate Kapasitesi<br />

Kapasitans Lineer Bölge Saturation Bölgesi Off bölgesi<br />

C C GSOV<br />

+ C 0<br />

WL / 2 C GSOV<br />

W + 2C<br />

0<br />

WL / 3<br />

W<br />

gs<br />

gd<br />

C GSOV<br />

C C GDOV<br />

W + C 0<br />

WL / 2 C GDOV<br />

W<br />

W<br />

C GDOV<br />

C<br />

gb<br />

C GBOV<br />

W<br />

C GBOV<br />

W C GBOV<br />

W + C 0<br />

WL

35<br />

Şekil 2.24. a) Yükselme Zamanı<br />

b) Düşme Zamanı

36<br />

Yükselme Zamanı Durumu<br />

C1<br />

= CBDP<br />

1<br />

+ CBDP2<br />

+ CGDOVPWP<br />

2<br />

+ CBDN<br />

1<br />

+ CONWN1LN1<br />

/ 2 + + CGDOVNWN1<br />

+ C<br />

+ C<br />

GDOVPW<br />

P3<br />

+ COPWP3LP3<br />

+ CGSOVNWN<br />

3<br />

+ CGDOVNWN<br />

3<br />

+ 2CONWN3LN<br />

3<br />

/ 2 + CL<br />

C1L<br />

= CGSOVPWP3L<br />

+ CGDOVPWP3L<br />

+ COPWP3L<br />

LP3L<br />

+ CGSOVNWN<br />

4L<br />

+ CGDOVNW<br />

+ CONWN<br />

4LLN<br />

4L<br />

C<br />

2<br />

= CBSN1<br />

+ CBDN<br />

2<br />

+ CGSOVNWN1<br />

+ CONWN1LN1<br />

/ 2<br />

C<br />

3<br />

= C GDOVN<br />

WN 2<br />

C<br />

4<br />

= CGDOVPWP<br />

1<br />

+ COPWP<br />

1LP1<br />

/ 2<br />

1<br />

⎡<br />

⎤<br />

⎢<br />

7η<br />

P<br />

VDD<br />

/ 8 −VBINSP<br />

− (<br />

P<br />

−1) VDD<br />

− 2<br />

SP<br />

( 2<br />

FP<br />

+ VDD<br />

/ 4)<br />

2<br />

1<br />

1<br />

η<br />

1<br />

γ<br />

1<br />

φ<br />

1<br />

/ 3<br />

α<br />

1<br />

≅ β<br />

P1<br />

⎢<br />

P<br />

⎢<br />

( ) ⎥ ⎥⎥ F<br />

−<br />

PR<br />

⎣−VDD<br />

4 exp − PF<br />

t<br />

DR<br />

⎦<br />

1<br />

⎡<br />

⎤<br />

α = − − 7 / 8 − 2 ( 2 + 3 / 4) 2<br />

2<br />

β<br />

N1<br />

VDD<br />

VBINSN1<br />

η<br />

N1V<br />

DD<br />

γ<br />

SN1<br />

φFN1<br />

VDD<br />

/ 3<br />

⎢⎣<br />

⎥ ⎦<br />

GSOVP<br />

W<br />

+ NC<br />

1<br />

⎧<br />

⎫<br />

α = ⎨ − − ( − ) / 8 − 2 [ 2 + 3( − )/<br />

4]<br />

2<br />

3<br />

β<br />

N1<br />

VDD<br />

VBINSN1<br />

VDD<br />

VTNF<br />

η<br />

N1<br />

γ<br />

SN1<br />

φFN1<br />

VDD<br />

VTNF<br />

/ 3⎬<br />

⎩<br />

⎭<br />

Düşme Zamanı Durumu<br />

C′<br />

+ CGSOVPWP2<br />

+ CL<br />

+ NC′<br />

2L<br />

C′<br />

2L<br />

= CGSOVNWN<br />

2L<br />

+ C<br />

GDOVNWN<br />

2L<br />

+ CONWN<br />

2L<br />

LN<br />

2L<br />

+ CGSOVPWP2L<br />

+ C<br />

+ 2COPWP2L<br />

LP2L<br />

/ 3<br />

C ′ = CBDN<br />

4<br />

+ CGDOVNWN<br />

4<br />

+ CONWN<br />

4LN<br />

4<br />

2 + CBSN<br />

3<br />

+ CGSOVNWN<br />

3<br />

+ C<br />

C ′<br />

3<br />

= CGDOVPWP3<br />

+ CGDOVNWN<br />

3<br />

+ CONWN<br />

3LN<br />

3<br />

/ 2<br />

PF<br />

⎡<br />

−<br />

⎤<br />

PR<br />

⎢V<br />

DD<br />

−VDD<br />

4 exp( − PR<br />

tdf<br />

) −VBINSN<br />

3<br />

−η<br />

N 3VDD<br />

/ 8<br />

α ′<br />

1<br />

≅ β<br />

N 3 ⎢<br />

⎢ ( ) ⎥ ⎥⎥ 1<br />

⎣−<br />

2γ<br />

2 + / 4 2<br />

SN 3<br />

φFN<br />

3<br />

VDD<br />

/ 3<br />

⎦<br />

PF<br />

⎡ −<br />

⎤<br />

Pr<br />

⎢V<br />

DD<br />

4 exp( − Pr<br />

tdf<br />

) −VBINSN<br />

3<br />

−η<br />

N 3V<br />

DD/<br />

20<br />

α ′<br />

2<br />

≅ β<br />

N 3 ⎢<br />

1<br />

⎢<br />

⎣−<br />

2γ<br />

2 + /10 2<br />

SN 3<br />

φFN<br />

3<br />

VDD<br />

/ 3<br />

1<br />

= CBDP3<br />

+ CBDP4<br />

+ CGDOVPWP4<br />

+ CBDN<br />

3<br />

+ CONWN1LN1<br />

+ CGDOVNWN1<br />

+ COPWP2LP2<br />

/ 2<br />

GDOVP<br />

2<br />

/<br />

ONWN<br />

3LN<br />

3<br />

( ) ⎥ ⎥⎥ ⎦<br />

⎡<br />

α ′ ≅ − − / 20 − 2<br />

2<br />

3<br />

β<br />

N 4<br />

VDD<br />

VBINSN<br />

4<br />

η<br />

N 4VDD<br />

γ<br />

SN 4 FN 4 DD<br />

3<br />

⎢⎣<br />

1<br />

⎤<br />

( 2φ<br />

+ V /10) /<br />

⎥ ⎦<br />

N 4L<br />

W<br />

P2L<br />

P3<br />

1L<br />

/ 2<br />

Şekil 2.25. Yükselme ve Düşme Zamanlarındaki Kapasite ve İletkenlik Faktörleri

37<br />

Kararkteristik dalga şekli neredeyse giriş sinyallerinden bağımsızdır. Bu şunu ifade<br />

etmektedir; çıkış gerilimi V 20 şekil 2.25.a) daki devrenin kutupları yada sıfırlarına<br />

bağlıdır. Çıkış gerilimi V 20 nin zamanlama sinyalini kutuplar ve sıfırlar ( poles and<br />

zeros ) vasıtasıyla tanımlamak için, lineer olmayan şekil 2.25.a) daki devrenin lineer<br />

hale getirilmesi gerekmektedir. Devreyi lineer hale getirmek için kullanılacak olan<br />

teknik öncelikle, pn birleşme noktası kapasitansı ve drain akımının lineer hale<br />

getirilmesini gerektirmektedir ( WU, C.Y., 1985 ).<br />

Lineer hale getirilen noktada t=t e seçildikten sonra, her bir MOSFET için bulk-source<br />

ve drain-source gerilimleri V GS<br />

′ ,<br />

V ′<br />

BS<br />

ve V DS<br />

′ tanımlanabilmektedir. Lineer noktada<br />

pn birleşme yeri kapasitansları C BD ve C BS SPICE2 programındaki formül<br />

kullanılarak hesaplanabilmektedir ( VLADIMIRESCU, A., LIU, S., 1985 ).<br />

Drain akımını lineer hale getirme işleminde, SPICE2 programındaki lineer bölge<br />

drain akımı,<br />

I<br />

dP1<br />

⎡<br />

= β<br />

P1<br />

−V<br />

⎢⎣<br />

+ β η V<br />

ı<br />

dN1<br />

− β<br />

P1<br />

N1<br />

P1<br />

= β<br />

⎡<br />

⎢<br />

V<br />

⎣<br />

N1<br />

DD<br />

2<br />

20<br />

⎡<br />

⎢<br />

V<br />

⎣<br />

BINSP1<br />

/ 2<br />

DD<br />

−V<br />

−<br />

+ β V<br />

−V<br />

BINSN1<br />

P1<br />

BINSN1<br />

( η −1) V − 2γ<br />

( 2φ<br />

+ V −V<br />

′ )<br />

P1<br />

DD<br />

− 2γ<br />

V<br />

16<br />

− 2γ<br />

SN1<br />

SN1<br />

DD<br />

SP1<br />

( 2φ<br />

+ V ′ )<br />

1<br />

2<br />

FP1<br />

⎤<br />

/ 3<br />

⎥<br />

V<br />

⎦<br />

DD<br />

20<br />

1<br />

2<br />

⎤<br />

/ 3 V<br />

⎥⎦<br />

( 2φ<br />

+ V ′ ) / 3 V − β η V<br />

2<br />

22 / 2<br />

FN1<br />

FN1<br />

22<br />

20<br />

1<br />

2<br />

⎤<br />

⎥<br />

⎦<br />

22<br />

20<br />

− β<br />

N1<br />

N1<br />

N1<br />

η V<br />

N1<br />

2<br />

20<br />

20<br />

/ 2<br />

− β V<br />

P1<br />

16<br />

V<br />

20<br />

..(1)<br />

..(2)<br />

Denklemlerdeki V 16 ve V 20 gerilimleri zaman domainninde tanımlanmalıdır.<br />

() t = V exp( − P t) u()<br />

t<br />

V16 DD<br />

f<br />

..(3)<br />

V<br />

() t = V { 1−<br />

exp[ − P ( t − t )] u( t − t )}<br />

20 DD<br />

r dr<br />

dr<br />

..(4)<br />

() t ( V −V<br />

){ − [ − P ( t − t )]} ⋅u( t − t )<br />

V22 =<br />

DD TNF<br />

1 exp<br />

r dr 2<br />

dr 2<br />

..(5)<br />

t dr ( t dr2 ) V 16 ve V 20 gerilimlerinin dalga şekilleri arasındaki ilk yükselme zamanıdır.<br />

M N1 MOSFET inin eşik ( Threshold ) gerilimi V TNF şu şekilde ifade edilebilmektedir;

38<br />

V<br />

TNF<br />

⎪⎧<br />

⎡<br />

+ ⎨ 2γ<br />

⎪⎩<br />

⎢⎣<br />

⎧ ⎡<br />

= −⎨2<br />

γ<br />

⎩<br />

⎢⎣<br />

SN<br />

( 2φ<br />

)<br />

1<br />

2<br />

1<br />

2<br />

−V<br />

⎤<br />

+ γ<br />

⎥⎦<br />

⎤<br />

⎥⎦<br />

2<br />

⎫<br />

⎬ / 2<br />

⎭<br />

⎡<br />

⎢⎣<br />

2<br />

2<br />

( 2φ<br />

) − 2V<br />

+ γ SN + 4 2γ<br />

V ( 2φ<br />

) + γ V −V<br />

TN / 2<br />

FN<br />

SN<br />

FN<br />

TN<br />

TN<br />

SN<br />

SN<br />

TN<br />

FN<br />

1<br />

2<br />

SN<br />

DD<br />

⎤⎪⎫<br />

⎬ ⎥⎦ ⎪⎭<br />

1<br />

2<br />

(6a)<br />

V<br />

TN<br />

V BINN<br />

1<br />

SN<br />

( 2φ<br />

FN<br />

)2<br />

≡ + γ<br />

…..(6b)<br />

Genellikle lineer hale getirme işlemi, hesaplama hatalarını en aza indirmektedir.<br />

Lineerleştirme için en ideal durum, MOSFET in lineer bölgesinin merkez noktasıdır.<br />

Bu yüzden lineer nokta V = 3V<br />

/ 4 olarak seçilebilmektedir. Böylece zaman t=t e<br />

20 DD<br />

şu şekilde ifade edilebilmektedir;<br />

e<br />

dr<br />

( ln 4) Pr<br />

t = T + /<br />

.....(7)<br />

2<br />

2<br />

Benzer teknik kullanılarak eşitlik 1 ve 2 deki V 20 , V<br />

16<br />

, V<br />

20<br />

ve V 22 gerilimleri<br />

lineer hale getirilebilmektedir. Sonuç olarak I dP1 ve I dN1<br />

edilebilmektedir;<br />

şu şekilde ifade<br />

I dP 1<br />

α1V20<br />

= ………..(8)<br />