Eine Einführung in die Schaltungsent- wicklung mit VHDL

Eine Einführung in die Schaltungsent- wicklung mit VHDL

Eine Einführung in die Schaltungsent- wicklung mit VHDL

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

INTERSTAATLICHE HOCHSCHULE<br />

FÜR TECHNIK BUCHS NTB<br />

<strong>E<strong>in</strong>führung</strong> <strong>in</strong> <strong>VHDL</strong><br />

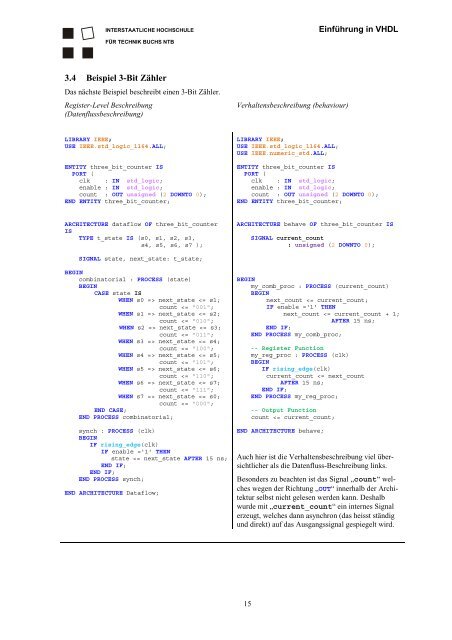

3.4 Beispiel 3-Bit Zähler<br />

Das nächste Beispiel beschreibt e<strong>in</strong>en 3-Bit Zähler.<br />

Register-Level Beschreibung<br />

(Datenflussbeschreibung)<br />

Verhaltensbeschreibung (behaviour)<br />

LIBRARY IEEE;<br />

USE IEEE.std_logic_1164.ALL;<br />

ENTITY three_bit_counter IS<br />

PORT (<br />

clk : IN std_logic;<br />

enable : IN std_logic;<br />

count : OUT unsigned (2 DOWNTO 0);<br />

END ENTITY three_bit_counter;<br />

LIBRARY IEEE;<br />

USE IEEE.std_logic_1164.ALL;<br />

USE IEEE.numeric_std.ALL;<br />

ENTITY three_bit_counter IS<br />

PORT (<br />

clk : IN std_logic;<br />

enable : IN std_logic;<br />

count : OUT unsigned (2 DOWNTO 0);<br />

END ENTITY three_bit_counter;<br />

ARCHITECTURE dataflow OF three_bit_counter<br />

IS<br />

TYPE t_state IS (s0, s1, s2, s3,<br />

s4, s5, s6, s7 );<br />

ARCHITECTURE behave OF three_bit_counter IS<br />

SIGNAL current_count<br />

: unsigned (2 DOWNTO 0);<br />

SIGNAL state, next_state: t_state;<br />

BEGIN<br />

comb<strong>in</strong>atorial : PROCESS (state)<br />

BEGIN<br />

CASE state IS<br />

WHEN s0 => next_state