Eine Einführung in die Schaltungsent- wicklung mit VHDL

Eine Einführung in die Schaltungsent- wicklung mit VHDL

Eine Einführung in die Schaltungsent- wicklung mit VHDL

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

INTERSTAATLICHE HOCHSCHULE<br />

FÜR TECHNIK BUCHS NTB<br />

<strong>E<strong>in</strong>führung</strong> <strong>in</strong> <strong>VHDL</strong><br />

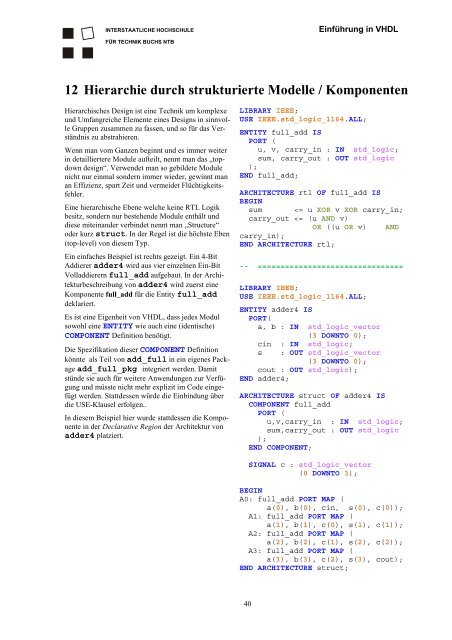

12 Hierarchie durch strukturierte Modelle / Komponenten<br />

Hierarchisches Design ist e<strong>in</strong>e Technik um komplexe<br />

und Umfangreiche Elemente e<strong>in</strong>es Designs <strong>in</strong> s<strong>in</strong>nvolle<br />

Gruppen zusammen zu fassen, und so für das Verständnis<br />

zu abstrahieren.<br />

Wenn man vom Ganzen beg<strong>in</strong>nt und es immer weiter<br />

<strong>in</strong> detailliertere Module aufteilt, nennt man das „topdown<br />

design“. Verwendet man so gebildete Module<br />

nicht nur e<strong>in</strong>mal sondern immer wieder, gew<strong>in</strong>nt man<br />

an Effizienz, spart Zeit und vermeidet Flüchtigkeitsfehler.<br />

<strong>E<strong>in</strong>e</strong> hierarchische Ebene welche ke<strong>in</strong>e RTL Logik<br />

besitz, sondern nur bestehende Module enthält und<br />

<strong>die</strong>se <strong>mit</strong>e<strong>in</strong>ander verb<strong>in</strong>det nennt man „Structure“<br />

oder kurz struct. In der Regel ist <strong>die</strong> höchste Eben<br />

(top-level) von <strong>die</strong>sem Typ.<br />

E<strong>in</strong> e<strong>in</strong>faches Beispiel ist rechts gezeigt. E<strong>in</strong> 4-Bit<br />

Ad<strong>die</strong>rer adder4 wird aus vier e<strong>in</strong>zelnen E<strong>in</strong>-Bit<br />

Vollad<strong>die</strong>rern full_add aufgebaut. In der Architekturbeschreibung<br />

von adder4 wird zuerst e<strong>in</strong>e<br />

Komponente full_add für <strong>die</strong> Entity full_add<br />

deklariert.<br />

Es ist e<strong>in</strong>e Eigenheit von <strong>VHDL</strong>, dass jedes Modul<br />

sowohl e<strong>in</strong>e ENTITY wie auch e<strong>in</strong>e (identische)<br />

COMPONENT Def<strong>in</strong>ition benötigt.<br />

Die Spezifikation <strong>die</strong>ser COMPONENT Def<strong>in</strong>ition<br />

könnte als Teil von add_full <strong>in</strong> e<strong>in</strong> eigenes Package<br />

add_full_pkg <strong>in</strong>tegriert werden. Da<strong>mit</strong><br />

stünde sie auch für weitere Anwendungen zur Verfügung<br />

und müsste nicht mehr explizit im Code e<strong>in</strong>gefügt<br />

werden. Stattdessen würde <strong>die</strong> E<strong>in</strong>b<strong>in</strong>dung über<br />

<strong>die</strong> USE-Klausel erfolgen..<br />

In <strong>die</strong>sem Beispiel hier wurde stattdessen <strong>die</strong> Komponente<br />

<strong>in</strong> der Declarative Region der Architektur von<br />

adder4 platziert.<br />

LIBRARY IEEE;<br />

USE IEEE.std_logic_1164.ALL;<br />

ENTITY full_add IS<br />

PORT (<br />

u, v, carry_<strong>in</strong> : IN std_logic;<br />

sum, carry_out : OUT std_logic<br />

);<br />

END full_add;<br />

ARCHITECTURE rtl OF full_add IS<br />

BEGIN<br />

sum