Eine Einführung in die Schaltungsent- wicklung mit VHDL

Eine Einführung in die Schaltungsent- wicklung mit VHDL

Eine Einführung in die Schaltungsent- wicklung mit VHDL

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

INTERSTAATLICHE HOCHSCHULE<br />

FÜR TECHNIK BUCHS NTB<br />

<strong>E<strong>in</strong>führung</strong> <strong>in</strong> <strong>VHDL</strong><br />

Als Modus kommen <strong>die</strong> Schlüsselwörter IN, OUT,<br />

INOUT oder BUFFER <strong>in</strong> Frage. Der Datentyp beschreibt<br />

<strong>die</strong> Art der Werte, <strong>die</strong> das PORT-Signal annehmen<br />

kann.<br />

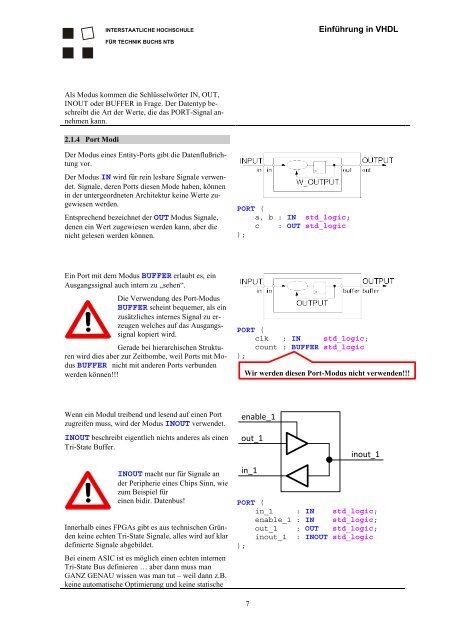

2.1.4 Port Modi<br />

Der Modus e<strong>in</strong>es Entity-Ports gibt <strong>die</strong> Datenflußrichtung<br />

vor.<br />

Der Modus IN wird für re<strong>in</strong> lesbare Signale verwendet.<br />

Signale, deren Ports <strong>die</strong>sen Mode haben, können<br />

<strong>in</strong> der untergeordneten Architektur ke<strong>in</strong>e Werte zugewiesen<br />

werden.<br />

Entsprechend bezeichnet der OUT Modus Signale,<br />

denen e<strong>in</strong> Wert zugewiesen werden kann, aber <strong>die</strong><br />

nicht gelesen werden können.<br />

PORT (<br />

a, b : IN std_logic;<br />

c : OUT std_logic<br />

);<br />

E<strong>in</strong> Port <strong>mit</strong> dem Modus BUFFER erlaubt es, e<strong>in</strong><br />

Ausgangssignal auch <strong>in</strong>tern zu „sehen“.<br />

Die Verwendung des Port-Modus<br />

BUFFER sche<strong>in</strong>t bequemer, als e<strong>in</strong><br />

zusätzliches <strong>in</strong>ternes Signal zu erzeugen<br />

welches auf das Ausgangssignal<br />

kopiert wird.<br />

Gerade bei hierarchischen Strukturen<br />

wird <strong>die</strong>s aber zur Zeitbombe, weil Ports <strong>mit</strong> Modus<br />

BUFFER nicht <strong>mit</strong> anderen Ports verbunden<br />

werden können!!!<br />

PORT (<br />

clk : IN std_logic;<br />

count : BUFFER std_logic<br />

);<br />

Wir werden <strong>die</strong>sen Port-Modus nicht verwenden!!!<br />

Wenn e<strong>in</strong> Modul treibend und lesend auf e<strong>in</strong>en Port<br />

zugreifen muss, wird der Modus INOUT verwendet.<br />

INOUT beschreibt eigentlich nichts anderes als e<strong>in</strong>en<br />

Tri-State Buffer.<br />

INOUT macht nur für Signale an<br />

der Peripherie e<strong>in</strong>es Chips S<strong>in</strong>n, wie<br />

zum Beispiel für<br />

e<strong>in</strong>en bidir. Datenbus!<br />

Innerhalb e<strong>in</strong>es FPGAs gibt es aus technischen Gründen<br />

ke<strong>in</strong>e echten Tri-State Signale, alles wird auf klar<br />

def<strong>in</strong>ierte Signale abgebildet.<br />

Bei e<strong>in</strong>em ASIC ist es möglich e<strong>in</strong>en echten <strong>in</strong>ternen<br />

Tri-State Bus def<strong>in</strong>ieren … aber dann muss man<br />

GANZ GENAU wissen was man tut – weil dann z.B.<br />

ke<strong>in</strong>e automatische Optimierung und ke<strong>in</strong>e statische<br />

enable_1<br />

out_1<br />

<strong>in</strong>_1<br />

<strong>in</strong>out_1<br />

PORT (<br />

<strong>in</strong>_1 : IN std_logic;<br />

enable_1 : IN std_logic;<br />

out_1 : OUT std_logic;<br />

<strong>in</strong>out_1 : INOUT std_logic<br />

);<br />

7