Eine Einführung in die Schaltungsent- wicklung mit VHDL

Eine Einführung in die Schaltungsent- wicklung mit VHDL

Eine Einführung in die Schaltungsent- wicklung mit VHDL

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

INTERSTAATLICHE HOCHSCHULE<br />

FÜR TECHNIK BUCHS NTB<br />

<strong>E<strong>in</strong>führung</strong> <strong>in</strong> <strong>VHDL</strong><br />

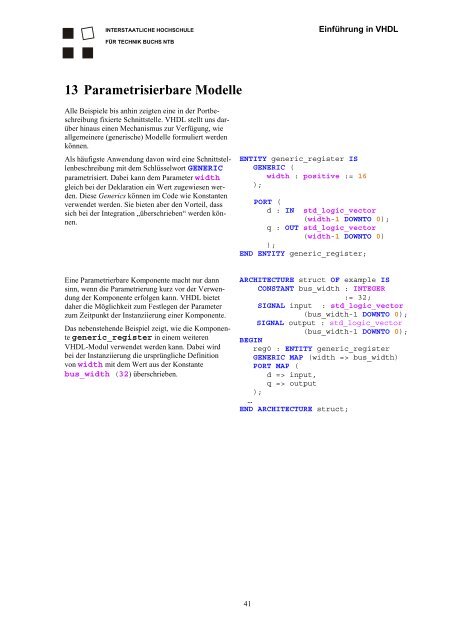

13 Parametrisierbare Modelle<br />

Alle Beispiele bis anh<strong>in</strong> zeigten e<strong>in</strong>e <strong>in</strong> der Portbeschreibung<br />

fixierte Schnittstelle. <strong>VHDL</strong> stellt uns darüber<br />

h<strong>in</strong>aus e<strong>in</strong>en Mechanismus zur Verfügung, wie<br />

allgeme<strong>in</strong>ere (generische) Modelle formuliert werden<br />

können.<br />

Als häufigste Anwendung davon wird e<strong>in</strong>e Schnittstellenbeschreibung<br />

<strong>mit</strong> dem Schlüsselwort GENERIC<br />

parametrisiert. Dabei kann dem Parameter width<br />

gleich bei der Deklaration e<strong>in</strong> Wert zugewiesen werden.<br />

Diese Generics können im Code wie Konstanten<br />

verwendet werden. Sie bieten aber den Vorteil, dass<br />

sich bei der Integration „überschrieben“ werden können.<br />

ENTITY generic_register IS<br />

GENERIC (<br />

width : positive := 16<br />

);<br />

PORT (<br />

d : IN std_logic_vector<br />

(width-1 DOWNTO 0);<br />

q : OUT std_logic_vector<br />

(width-1 DOWNTO 0)<br />

);<br />

END ENTITY generic_register;<br />

<strong>E<strong>in</strong>e</strong> Parametrierbare Komponente macht nur dann<br />

s<strong>in</strong>n, wenn <strong>die</strong> Parametrierung kurz vor der Verwendung<br />

der Komponente erfolgen kann. <strong>VHDL</strong> bietet<br />

daher <strong>die</strong> Möglichkeit zum Festlegen der Parameter<br />

zum Zeitpunkt der Instanziierung e<strong>in</strong>er Komponente.<br />

Das nebenstehende Beispiel zeigt, wie <strong>die</strong> Komponente<br />

generic_register <strong>in</strong> e<strong>in</strong>em weiteren<br />

<strong>VHDL</strong>-Modul verwendet werden kann. Dabei wird<br />

bei der Instanziierung <strong>die</strong> ursprüngliche Def<strong>in</strong>ition<br />

von width <strong>mit</strong> dem Wert aus der Konstante<br />

bus_width (32) überschrieben.<br />

ARCHITECTURE struct OF example IS<br />

CONSTANT bus_width : INTEGER<br />

:= 32;<br />

SIGNAL <strong>in</strong>put : std_logic_vector<br />

(bus_width-1 DOWNTO 0);<br />

SIGNAL output : std_logic_vector<br />

(bus_width-1 DOWNTO 0);<br />

BEGIN<br />

reg0 : ENTITY generic_register<br />

GENERIC MAP (width => bus_width)<br />

PORT MAP (<br />

d => <strong>in</strong>put,<br />

q => output<br />

);<br />

…<br />

END ARCHITECTURE struct;<br />

41