1 25 2 10 3 15 4 20 5 20 6 20 7 20 8 20 150 Note: - Ing. H. Heuermann

1 25 2 10 3 15 4 20 5 20 6 20 7 20 8 20 150 Note: - Ing. H. Heuermann

1 25 2 10 3 15 4 20 5 20 6 20 7 20 8 20 150 Note: - Ing. H. Heuermann

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

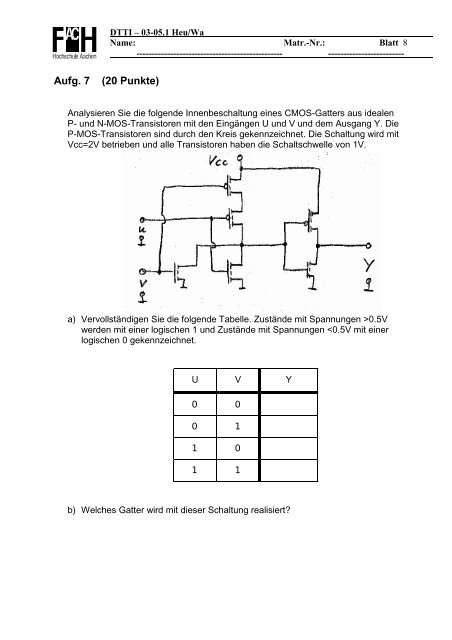

DTTI – 03-05.1 Heu/Wa<br />

Name: Matr.-Nr.: Blatt 8<br />

------------------------------------------------ -------------------------<br />

Aufg. 7<br />

(<strong>20</strong> Punkte)<br />

Analysieren Sie die folgende Innenbeschaltung eines CMOS-Gatters aus idealen<br />

P- und N-MOS-Transistoren mit den Eingängen U und V und dem Ausgang Y. Die<br />

P-MOS-Transistoren sind durch den Kreis gekennzeichnet. Die Schaltung wird mit<br />

Vcc=2V betrieben und alle Transistoren haben die Schaltschwelle von 1V.<br />

a) Vervollständigen Sie die folgende Tabelle. Zustände mit Spannungen >0.5V<br />

werden mit einer logischen 1 und Zustände mit Spannungen